Frequency divider

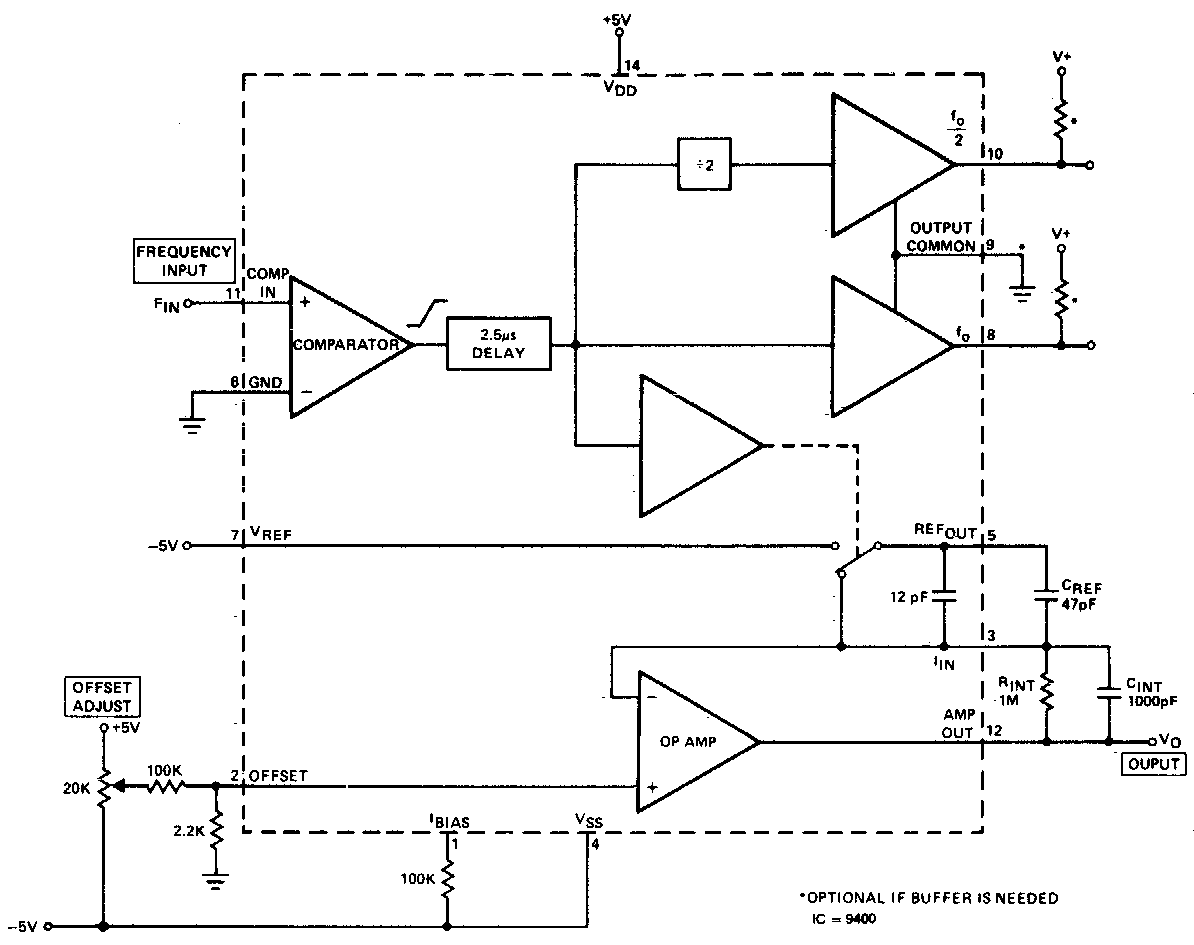

If the input frequency is known, the timer can be utilized as a frequency divider by adjusting the duration of the timing cycle. The figure illustrates the waveforms of the timer when employed as a divide-by-three circuit. This application leverages the characteristic that this circuit cannot be retriggered during the timing cycle.

The described circuit operates as a frequency divider by utilizing a timer IC, such as the 555 timer, configured in a monostable or astable mode, depending on the desired output waveform characteristics. In this specific application, the timer is set up to divide the input frequency by three.

To achieve this, the timing cycle must be adjusted to ensure that the output pulse width corresponds to one-third of the input signal's period. The timer's output will generate a square wave signal that toggles between high and low states, effectively creating a divided frequency output.

The waveforms depicted in the accompanying figure demonstrate the relationship between the input frequency and the output frequency. The timer's inability to be retriggered during its timing cycle is a crucial feature that ensures stable operation. This means that once the timer is triggered by an input pulse, it will complete its timing cycle before it can respond to another input pulse, thereby preventing any unintended frequency division or glitches in the output signal.

In practice, the resistors and capacitors used in the timing circuit must be carefully selected to achieve the desired timing intervals. The values of these components will determine the high time and low time of the output signal, directly influencing the effective frequency division ratio. By calculating the required time intervals based on the input frequency, appropriate component values can be derived to configure the timer accurately for the divide-by-three application.

This circuit can be applied in various electronic systems where frequency division is necessary, such as in digital clocks, frequency synthesizers, or communication systems, where precise timing and frequency manipulation are essential for proper operation.If the input frequency is known, the timer can easily be used as a frequency divider by adjusting the length of the timeing cycle. Figure shows the waveforms of the timer when used as a divide-by-three circuit. This application makes use of the fact that this circuit cannot be retriggered during the timing cycle. 🔗 External reference

The described circuit operates as a frequency divider by utilizing a timer IC, such as the 555 timer, configured in a monostable or astable mode, depending on the desired output waveform characteristics. In this specific application, the timer is set up to divide the input frequency by three.

To achieve this, the timing cycle must be adjusted to ensure that the output pulse width corresponds to one-third of the input signal's period. The timer's output will generate a square wave signal that toggles between high and low states, effectively creating a divided frequency output.

The waveforms depicted in the accompanying figure demonstrate the relationship between the input frequency and the output frequency. The timer's inability to be retriggered during its timing cycle is a crucial feature that ensures stable operation. This means that once the timer is triggered by an input pulse, it will complete its timing cycle before it can respond to another input pulse, thereby preventing any unintended frequency division or glitches in the output signal.

In practice, the resistors and capacitors used in the timing circuit must be carefully selected to achieve the desired timing intervals. The values of these components will determine the high time and low time of the output signal, directly influencing the effective frequency division ratio. By calculating the required time intervals based on the input frequency, appropriate component values can be derived to configure the timer accurately for the divide-by-three application.

This circuit can be applied in various electronic systems where frequency division is necessary, such as in digital clocks, frequency synthesizers, or communication systems, where precise timing and frequency manipulation are essential for proper operation.If the input frequency is known, the timer can easily be used as a frequency divider by adjusting the length of the timeing cycle. Figure shows the waveforms of the timer when used as a divide-by-three circuit. This application makes use of the fact that this circuit cannot be retriggered during the timing cycle. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713