Precision Clock Generator

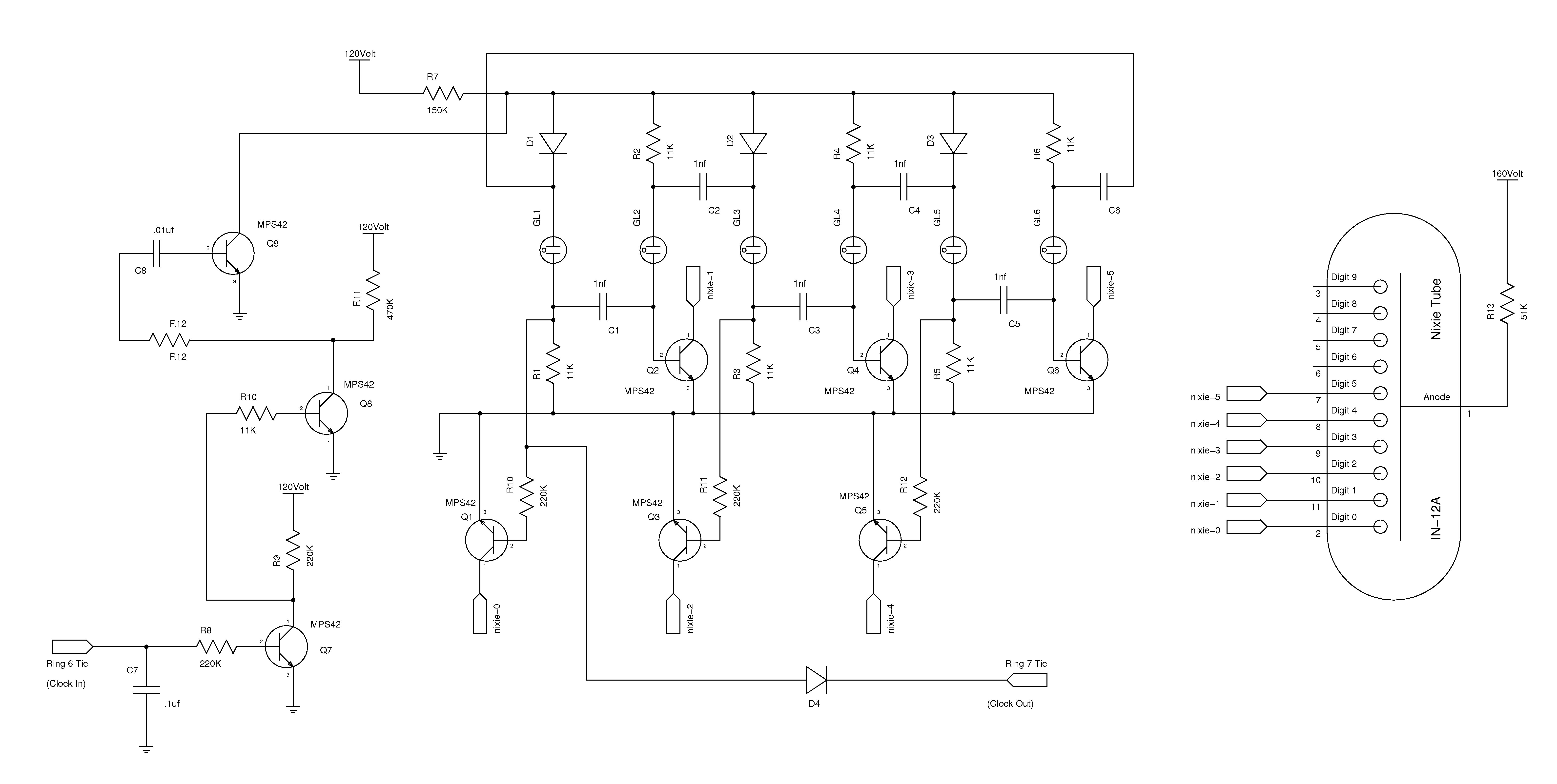

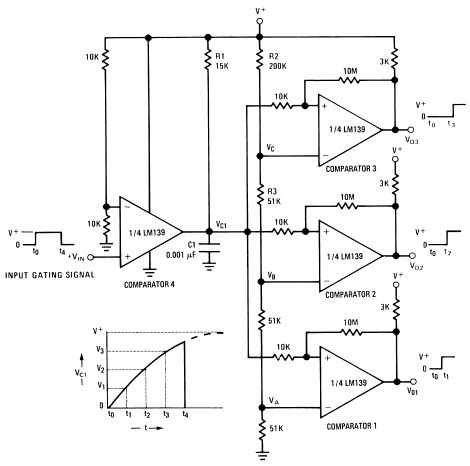

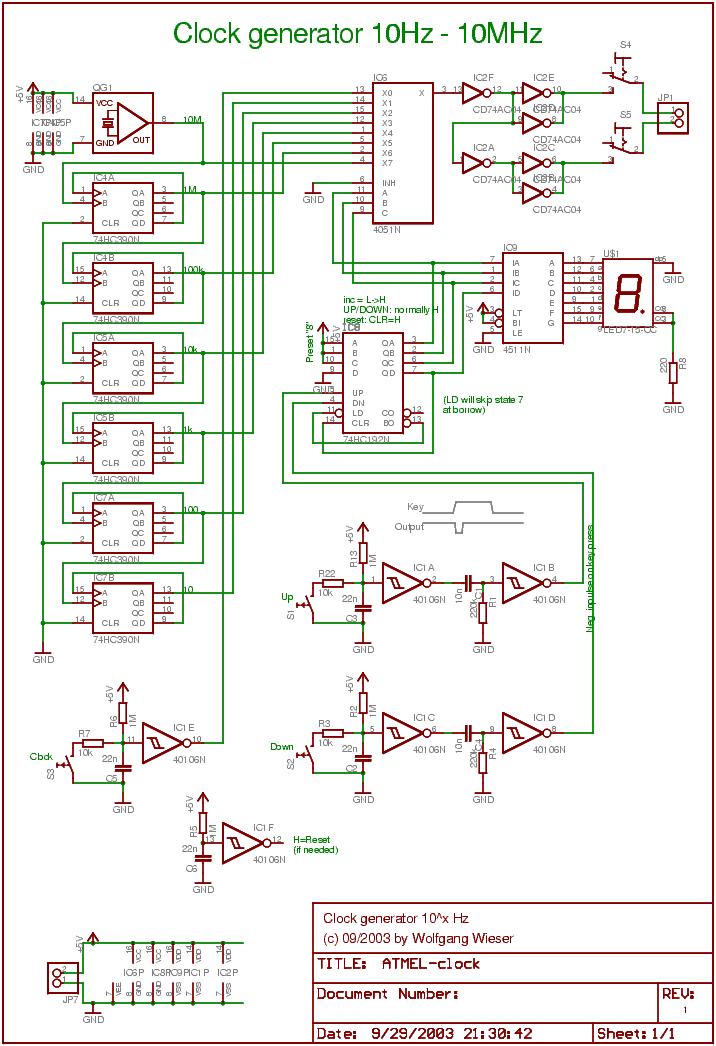

The device described can generate a complementary clock signal at frequencies ranging from 10Hz to 10MHz in factors of ten. It is referred to as the "10xHz clock generator," where 'x' is a number between 1 and 7. Additionally, the device allows for manual clock impulse creation via a push button. Frequency selection is managed using two push buttons/switches: S1 to increase the frequency by a factor of 10 and S2 to decrease it. The frequency is determined by three pins, A, B, and C, on the 4051, which represent the binary value of 'x.' When 'x' is set to 7 (A, B, C being HIGH), the direct signal from the crystal-controlled oscillator (OG1) is selected. Lower values/combinations select lower frequencies from a divide-cascade configuration utilizing three 74HC390 chips. It is important to note that pressing the "up" button when at value 7 will revert to value 0 (manual clocking), while pressing down at value 0 will step to 6 instead of 7. This behavior was acknowledged prior to circuit construction, and correcting it was deemed unnecessary given the circuit complexity. The CD40106 is employed for switch debouncing, particularly through IC1B and IC1D, which generate a small negative impulse when the up/down key is pressed. This design choice ensures that frequency changes occur upon pressing the switch rather than upon release, avoiding counterintuitive operation. The output stage consists of two parallel 74AC04 inverters, each capable of sourcing and sinking up to 24mA with slew rates comparable to the HC family. Due to the differing number of inverters through which the complementary signals pass, they are not perfectly synchronized, but the delay of less than 7ns is not expected to cause significant issues. It should be noted that bypass capacitors are not included in the design, as they have been soldered directly onto the IC socket pins for optimal performance. This approach also simplifies the PCB design, which has proven challenging in past iterations.

The clock generator circuit is designed to provide a versatile and efficient method for generating clock signals across a wide frequency range. The architecture primarily employs a 4051 multiplexer, which is pivotal for selecting the desired frequency based on the binary inputs provided by the pins A, B, and C. The use of push buttons S1 and S2 allows for intuitive user interaction, enabling easy frequency adjustments. The cascading configuration of the 74HC390 chips facilitates division of the input frequency, ensuring that the generator can produce a wide variety of output frequencies while maintaining signal integrity.

The inclusion of the CD40106 for switch debouncing is a critical design element, as it enhances the reliability of the user interface by preventing erroneous signal transitions caused by mechanical bounce in the push buttons. The design of the impulse generation through IC1B and IC1D ensures that the user experiences immediate feedback when adjusting the frequency, aligning with user expectations for responsive control.

The output stage, utilizing 74AC04 inverters, is engineered to deliver robust drive capability, making it suitable for interfacing with various loads. The consideration of signal propagation delay due to the unequal number of inverters for the complementary signals is a thoughtful approach in ensuring that the overall performance of the clock generator remains within acceptable limits for most applications.

Overall, the design reflects a balance between functionality and practicality, with careful attention given to user interaction, signal integrity, and circuit simplicity. This clock generator serves as a valuable tool for applications requiring precise timing signals, whether in experimental setups or integrated into larger electronic systems.The device presented here can generate a complementary clock signal at frequencies of 10Hz to 10MHz in steps of factor10. Thus, I chose to call it "10xHz clock generator" (with x being a number between 1 and 7). It can also be used to manually create clock impulses using a press button. The frequency is selected using two press buttons/swiches: S1 to switch the frequency up by a factor of 10 and S2 to switch it down. The frequency selection is determined by the three pins A, B, C at the 4051 which are just the binary representation of the x-value. 7 (i. e. A, B, C being HIGH) selects the direct signal from the crystal-controlled oscillator OG1 while lower numers/combinations select lower frqeuencies from the divide-cascade built-up with three 74HC390 chips.

Note that when pressing the "up" button when value 7 is active will switch back to value "0" (i. e. manual clocking, see below) while pressing down at value "0" will step to 6 instead of 7. I knew this bug before building the circuit but I decided that implementing the correct behavior was not worth the additional circuicy. The CD40106 is used to debounce the switches. Especially note IC1B and IC1D which form a small negative impulse when pressing the up/down key. This is needed to make the frequency change when pressing the switch instead of when releasing it which would be counter-intuitive/unexpected behaviour.

The output stage is done with two parallel 74AC04 inverters which can source and sink up to 24mA each with slew rates at least as good as the HC family. Due to the fact that the complementary signals travel through a different number of inverters, they are not exactly in sync but the delay of about <7ns should not make big trouble.

Note: The design above leaves away all the bypassing capacitors. That is because I chose to solder them directly on the IC socket pins for optimum performance and because otherwise the required signal lines proved to make PCB design much more complicated in the past. 🔗 External reference

The clock generator circuit is designed to provide a versatile and efficient method for generating clock signals across a wide frequency range. The architecture primarily employs a 4051 multiplexer, which is pivotal for selecting the desired frequency based on the binary inputs provided by the pins A, B, and C. The use of push buttons S1 and S2 allows for intuitive user interaction, enabling easy frequency adjustments. The cascading configuration of the 74HC390 chips facilitates division of the input frequency, ensuring that the generator can produce a wide variety of output frequencies while maintaining signal integrity.

The inclusion of the CD40106 for switch debouncing is a critical design element, as it enhances the reliability of the user interface by preventing erroneous signal transitions caused by mechanical bounce in the push buttons. The design of the impulse generation through IC1B and IC1D ensures that the user experiences immediate feedback when adjusting the frequency, aligning with user expectations for responsive control.

The output stage, utilizing 74AC04 inverters, is engineered to deliver robust drive capability, making it suitable for interfacing with various loads. The consideration of signal propagation delay due to the unequal number of inverters for the complementary signals is a thoughtful approach in ensuring that the overall performance of the clock generator remains within acceptable limits for most applications.

Overall, the design reflects a balance between functionality and practicality, with careful attention given to user interaction, signal integrity, and circuit simplicity. This clock generator serves as a valuable tool for applications requiring precise timing signals, whether in experimental setups or integrated into larger electronic systems.The device presented here can generate a complementary clock signal at frequencies of 10Hz to 10MHz in steps of factor10. Thus, I chose to call it "10xHz clock generator" (with x being a number between 1 and 7). It can also be used to manually create clock impulses using a press button. The frequency is selected using two press buttons/swiches: S1 to switch the frequency up by a factor of 10 and S2 to switch it down. The frequency selection is determined by the three pins A, B, C at the 4051 which are just the binary representation of the x-value. 7 (i. e. A, B, C being HIGH) selects the direct signal from the crystal-controlled oscillator OG1 while lower numers/combinations select lower frqeuencies from the divide-cascade built-up with three 74HC390 chips.

Note that when pressing the "up" button when value 7 is active will switch back to value "0" (i. e. manual clocking, see below) while pressing down at value "0" will step to 6 instead of 7. I knew this bug before building the circuit but I decided that implementing the correct behavior was not worth the additional circuicy. The CD40106 is used to debounce the switches. Especially note IC1B and IC1D which form a small negative impulse when pressing the up/down key. This is needed to make the frequency change when pressing the switch instead of when releasing it which would be counter-intuitive/unexpected behaviour.

The output stage is done with two parallel 74AC04 inverters which can source and sink up to 24mA each with slew rates at least as good as the HC family. Due to the fact that the complementary signals travel through a different number of inverters, they are not exactly in sync but the delay of about <7ns should not make big trouble.

Note: The design above leaves away all the bypassing capacitors. That is because I chose to solder them directly on the IC socket pins for optimum performance and because otherwise the required signal lines proved to make PCB design much more complicated in the past. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713