20Mhz-clock-phase-lock

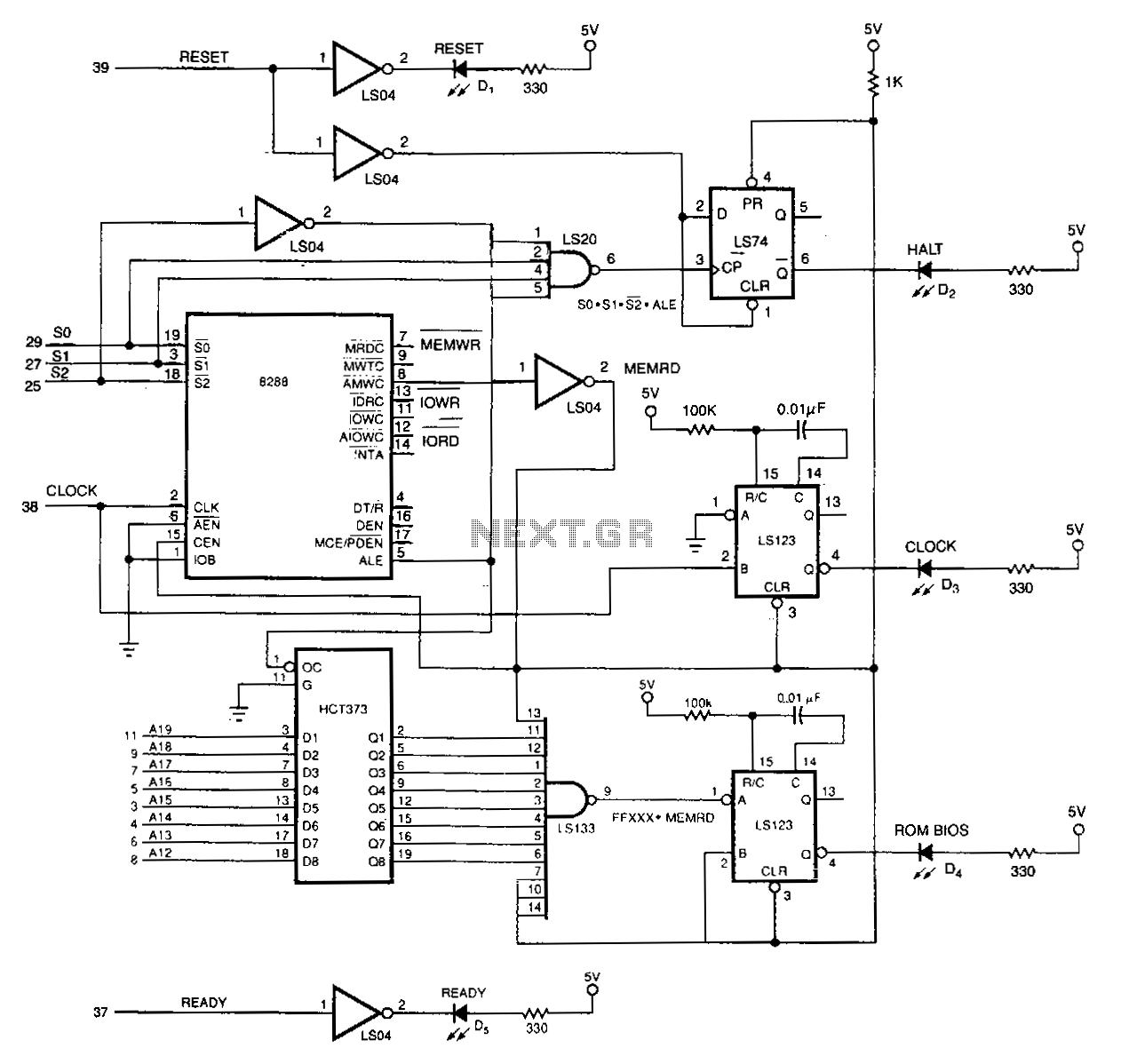

The 20-MHz clock is phase-locked to the 10-MHz NuBus clock of Apple's Mac II. It employs simple and cost-effective CMOS circuitry to generate square waves at 10 MHz and 20 MHz. The output duty cycle settings are not affected by variations in Vee. The circuit receives a NuBus clock signal, which has a specified 75 percent duty cycle at 10 MHz, meaning the square wave is high for 75 ns and low for the remaining 25 ns. To create the 20-MHz signal, the circuit generates a 25-ns negative-going pulse that is delayed by 50 ns from the falling edge of the 10-MHz NuBus clock input at point E. This pulse is then combined with the NuBus clock to produce the 20-MHz clock at point G. Finally, applying the 25-ns pulse to the set input of a set-reset flip-flop results in a 10-MHz square wave at point F.

The circuit utilizes a phase-locked loop (PLL) architecture, where the 10-MHz NuBus clock serves as the reference frequency. The CMOS circuitry is designed to ensure low power consumption while maintaining signal integrity. The input signal from the NuBus clock is processed to generate a precise 20-MHz output.

At point E, the input clock signal is monitored, and upon detecting the falling edge, a 50-ns delay is introduced before generating a negative-going pulse. This pulse is critical for synchronizing the output frequency to the desired 20 MHz. The timing relationships and delays are meticulously calculated to ensure that the output signals maintain the required frequency and duty cycle.

The combination of the delayed pulse and the original NuBus clock at point G produces the 20-MHz clock signal. This signal is then routed to various components that require a 20-MHz clock for operation.

Point F is significant as it provides a 10-MHz square wave output, which is generated by utilizing a set-reset flip-flop configuration. The 25-ns pulse applied to the set input effectively toggles the flip-flop, producing a stable 10-MHz output that adheres to the original duty cycle requirements.

Overall, this circuit exemplifies efficient design principles in digital electronics, leveraging CMOS technology for reliable performance in clock generation applications. The careful consideration of timing, duty cycle, and power consumption makes it suitable for integration into systems that require precise clock signals.The 20-MHz clock phase-locks to Apple"s Mac II 10-MHz NuBus clock. It uses a simple, inexpensive CMOS circuitry to generate 10-and 20-MHz square waves. The output duty cycle settings are insensitive to Vee variations. The input to the circuit is a NuBus clock signal with specifications that call for a 75 percent duty cycle at 10 MHz-a square wave that"s high for 75 ns and low for the remaining 25 ns. To generate the 20-MHz signal, the circuit produces a 25-ns negative-going pulse, delayed 50 ns from the falling edge of the 10-MHz NuBus clock input at point E. NO Ring that pulse with the NuBus clock produces the 20-MHz clock at point G. Finally, applying the 25-ns pulse to the set input of a set-reset input, results in a 10-MHz square wave at F.

🔗 External reference

The circuit utilizes a phase-locked loop (PLL) architecture, where the 10-MHz NuBus clock serves as the reference frequency. The CMOS circuitry is designed to ensure low power consumption while maintaining signal integrity. The input signal from the NuBus clock is processed to generate a precise 20-MHz output.

At point E, the input clock signal is monitored, and upon detecting the falling edge, a 50-ns delay is introduced before generating a negative-going pulse. This pulse is critical for synchronizing the output frequency to the desired 20 MHz. The timing relationships and delays are meticulously calculated to ensure that the output signals maintain the required frequency and duty cycle.

The combination of the delayed pulse and the original NuBus clock at point G produces the 20-MHz clock signal. This signal is then routed to various components that require a 20-MHz clock for operation.

Point F is significant as it provides a 10-MHz square wave output, which is generated by utilizing a set-reset flip-flop configuration. The 25-ns pulse applied to the set input effectively toggles the flip-flop, producing a stable 10-MHz output that adheres to the original duty cycle requirements.

Overall, this circuit exemplifies efficient design principles in digital electronics, leveraging CMOS technology for reliable performance in clock generation applications. The careful consideration of timing, duty cycle, and power consumption makes it suitable for integration into systems that require precise clock signals.The 20-MHz clock phase-locks to Apple"s Mac II 10-MHz NuBus clock. It uses a simple, inexpensive CMOS circuitry to generate 10-and 20-MHz square waves. The output duty cycle settings are insensitive to Vee variations. The input to the circuit is a NuBus clock signal with specifications that call for a 75 percent duty cycle at 10 MHz-a square wave that"s high for 75 ns and low for the remaining 25 ns. To generate the 20-MHz signal, the circuit produces a 25-ns negative-going pulse, delayed 50 ns from the falling edge of the 10-MHz NuBus clock input at point E. NO Ring that pulse with the NuBus clock produces the 20-MHz clock at point G. Finally, applying the 25-ns pulse to the set input of a set-reset input, results in a 10-MHz square wave at F.

🔗 External reference