Build A Byte Blaster Circuit

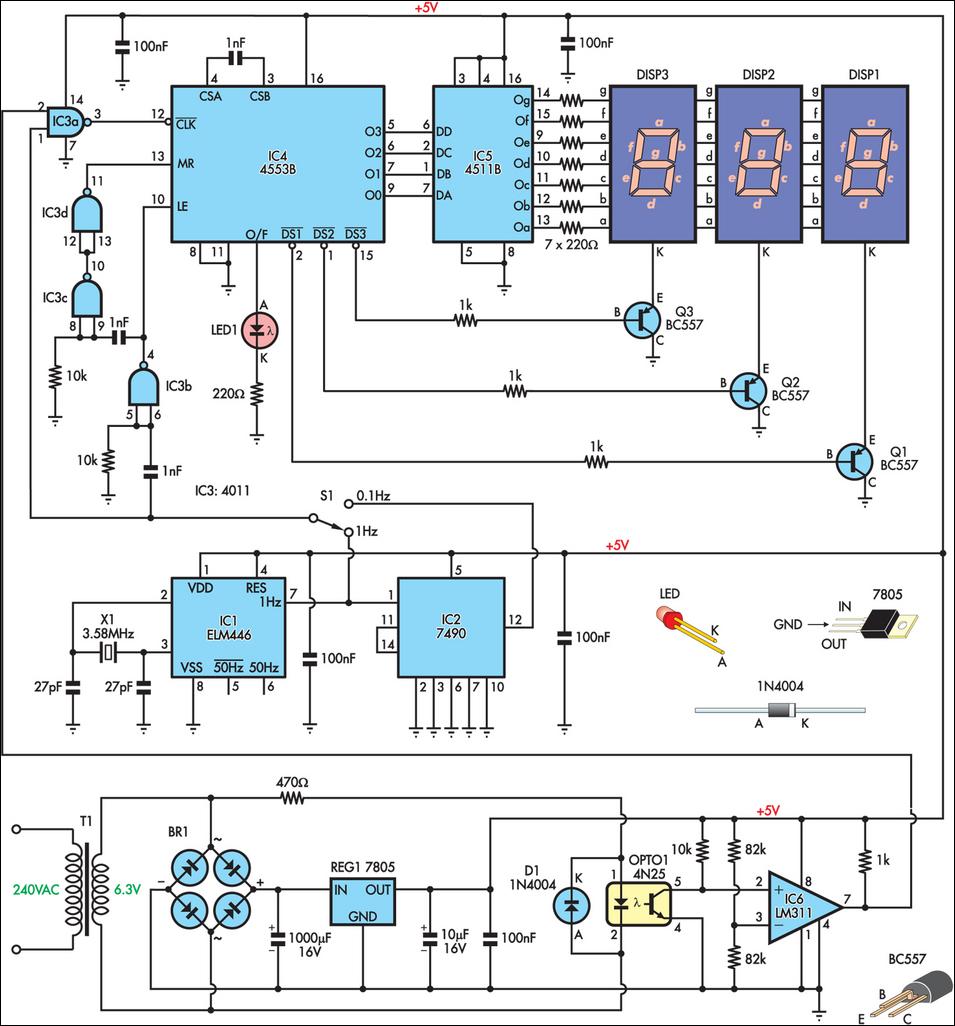

This schematic is directly sourced from the Altera ByteBlaster datasheet or manual, which provides comprehensive details regarding the connector's functionality and pin connections. It is advisable to review the datasheet available on their website or through a search engine for thorough understanding. The 74LS244 is a Low Power Schottky Octal Buffer. A limitation of this design is that some computer parallel ports may not supply sufficient power for this circuit. The ByteBlaster MV is an updated design that addresses this issue, which will be discussed further. The resistors in this design serve as simple current-limiting components, ensuring that no surge of current from the JTAG or parallel ports can potentially damage the 74LS244. The pins for the 10-pin connector are clearly labeled, with only 8 out of the 10 pins connected to the JTAG-style connector.

The schematic in question is integral to understanding the operation of the Altera ByteBlaster, a device used for programming and debugging FPGA and CPLD devices. The 74LS244 octal buffer plays a crucial role in this circuit, providing signal buffering and isolation between the programming interface and the target device. This is particularly important to maintain signal integrity and protect sensitive components from potential damage due to high current levels.

In this design, the use of current-limiting resistors is essential. These resistors are strategically placed to prevent excessive current flow that could occur during signal transitions, which could otherwise lead to overheating or failure of the 74LS244. The careful selection of these resistors ensures that the circuit operates within safe limits, allowing for reliable performance across varying conditions.

The 10-pin connector is a critical interface for the ByteBlaster, enabling communication between the programming device and the target hardware. Although the connector features 10 pins, only 8 are utilized in the JTAG configuration. This pin arrangement is designed to facilitate straightforward connections while minimizing the risk of miswiring. Each pin's function is labeled clearly, aiding in the assembly and troubleshooting processes.

The updated ByteBlaster MV design provides enhancements over the original model, particularly in power management. By addressing the power limitations of some parallel ports, it ensures that the device can operate effectively across a wider range of systems. This advancement is vital for users who require compatibility with various computer architectures and configurations.

In summary, the schematic derived from the Altera ByteBlaster documentation encapsulates essential design elements, including the role of the 74LS244 buffer, the importance of current-limiting resistors, and the functionality of the 10-pin connector. Understanding these components is crucial for effective implementation and operation of the ByteBlaster in programming and debugging applications.This schematic is taken directly from the Altera ByteBlaster datasheet or manual. They spill out all the fine print and details of how the connector works & what connections go where. Find the datasheet on their website or through google and give it a good read through. The 74LS244 is a Low Power Schottky Octal Buffer. A downside to using this ch ip in this design is that some computer parallel ports may not offer enough power for this circuit. The ByteBlaster MV is an updated design that solves this problem, something we`ll explore later on. These resisitors act as simple current limiting resistors. They make sure no surge of current can come from the JTAG or Parallel ports that might potentially damage the 74LS244. The pins for the 10-Pin connector are again clearly labeled. Notice that only 8 of the 10 pins are actually connected to the JTAG style connector. 🔗 External reference

The schematic in question is integral to understanding the operation of the Altera ByteBlaster, a device used for programming and debugging FPGA and CPLD devices. The 74LS244 octal buffer plays a crucial role in this circuit, providing signal buffering and isolation between the programming interface and the target device. This is particularly important to maintain signal integrity and protect sensitive components from potential damage due to high current levels.

In this design, the use of current-limiting resistors is essential. These resistors are strategically placed to prevent excessive current flow that could occur during signal transitions, which could otherwise lead to overheating or failure of the 74LS244. The careful selection of these resistors ensures that the circuit operates within safe limits, allowing for reliable performance across varying conditions.

The 10-pin connector is a critical interface for the ByteBlaster, enabling communication between the programming device and the target hardware. Although the connector features 10 pins, only 8 are utilized in the JTAG configuration. This pin arrangement is designed to facilitate straightforward connections while minimizing the risk of miswiring. Each pin's function is labeled clearly, aiding in the assembly and troubleshooting processes.

The updated ByteBlaster MV design provides enhancements over the original model, particularly in power management. By addressing the power limitations of some parallel ports, it ensures that the device can operate effectively across a wider range of systems. This advancement is vital for users who require compatibility with various computer architectures and configurations.

In summary, the schematic derived from the Altera ByteBlaster documentation encapsulates essential design elements, including the role of the 74LS244 buffer, the importance of current-limiting resistors, and the functionality of the 10-pin connector. Understanding these components is crucial for effective implementation and operation of the ByteBlaster in programming and debugging applications.This schematic is taken directly from the Altera ByteBlaster datasheet or manual. They spill out all the fine print and details of how the connector works & what connections go where. Find the datasheet on their website or through google and give it a good read through. The 74LS244 is a Low Power Schottky Octal Buffer. A downside to using this ch ip in this design is that some computer parallel ports may not offer enough power for this circuit. The ByteBlaster MV is an updated design that solves this problem, something we`ll explore later on. These resisitors act as simple current limiting resistors. They make sure no surge of current can come from the JTAG or Parallel ports that might potentially damage the 74LS244. The pins for the 10-Pin connector are again clearly labeled. Notice that only 8 of the 10 pins are actually connected to the JTAG style connector. 🔗 External reference