Digital Buffer

1. Definition and Core Functionality

1.1 Definition and Core Functionality

A digital buffer is a crucial electronic component designed to accommodate and manage the flow of digital signals. At its core, a buffer acts as a stabilizing intermediary that stores and subsequently transfers signals from one circuit to another, thus ensuring that the integrity and timing of these signals are preserved. By seamlessly interfacing different circuits, a digital buffer serves as a critical facilitator in complex systems, where signal distortion or timing bottlenecks can lead to failures or degraded performance.

The functionality of a digital buffer is grounded in its ability to isolate components, allowing for varied input and output characteristics without sacrificing performance. By utilizing transistors, primarily in the form of CMOS (Complementary Metal-Oxide-Semiconductor) technology, digital buffers can effectively increase the input impedance while decreasing the output impedance. This property not only minimizes signal disturbance but also enables the buffer to drive subsequent stages with higher loads than what the original signal source could manage.

Core Specifications

Key specifications of a digital buffer generally include:

- Input and Output Voltage Levels: These levels determine the operational states of the buffer, commonly aligned with standard logic families such as TTL (Transistor-Transistor Logic) or CMOS, enabling compatibility with various circuits.

- Propagation Delay: The time taken for a change at the input to reflect at the output. This delay is significant in high-speed circuits where synchronization is critical.

- Drive Capability: The maximum current the buffer output can source or sink while maintaining specified voltage levels. This is particularly essential when interfacing with load-heavy components.

Operational Context and Applications

Considering these characteristics, digital buffers find extensive applications in various fields, including:

- Signal Conditioning: Buffers are often used to condition signals for further processing, reducing loading effects which could distort the original signal.

- Data Bus Isolation: In microprocessor systems, buffers are employed to isolate different parts of the data bus, thereby preventing conflicts and reducing noise between components.

- Memory Read/Write Operations: Buffers facilitate efficient data transfer between processors and memory modules, ensuring accurate and timely data handling.

Ultimately, the digital buffer is pivotal in achieving high-performance electronic systems. Its role extends beyond mere signal management; it also contributes to overall system reliability, ensuring that the discrete operations that form the backbone of digital electronics occur without interference and with precision.

This equation models the output voltage of a buffer in relation to the input voltage, taking into account the resistances of the source and load. Here, \(V_{out}\) demonstrates how a buffer can effectively manage and adapt input signals for different electrical environments.

1.2 Types of Digital Buffers

The concept of digital buffers is of paramount importance in both theoretical and practical aspects of electronic design. As integral components in digital circuits, they serve to isolate and manage signal integrity without altering the logical value of the inputs. In this section, we will explore various types of digital buffers, elaborating on their functionality, applications, and nuances.Unidirectional Buffers

Unidirectional buffers, as the name suggests, allow signals to flow in a single direction. These buffers can be seen as simple amplifiers for digital signals, strengthening the input signals without affecting their logic levels. A common implementation is the *74HC125*, which consists of four independent buffers, each of which can drive its output high or low based on the input logic voltage. Practically, unidirectional buffers are widely used in applications like fan-out management, where a single signal needs to drive multiple inputs effectively. By isolating the load from the original signal source, they help maintain the performance and integrity of the circuit.Bidirectional Buffers

In contrast, bidirectional buffers facilitate signal passage in both directions, making them essential in communication interfaces and data buses. An example of such buffering is manifested in *transceivers*, which not only send but also receive data. The *74HC245* is a typical bidirectional buffer used in microcontrollers and communication lines. The primary advantage of bidirectional buffers lies in their ability to manage data flow dynamically. This ability is critical in applications where both sending and receiving data under varying conditions is necessary, such as in memory or I/O operations.Tri-State Buffers

Tri-state buffers are a specific type of digital buffer that can assume three different states: a high logic level, a low logic level, and a high-impedance state (or off state). This third state effectively disconnects the buffer from the circuit, allowing multiple devices to share the same output line without conflict. Employing tri-state buffers is vital in bus architectures, where they permit multiple devices to connect to a shared communication path without interference. The tri-state buffer is typically controlled by an enable input signal that determines whether the buffer outputs the signal or enters a high-impedance state, ensuring orderly data transfer. Practically employed in microprocessors, memory devices, and other complex digital systems, tri-state buffers enhance the flexibility of system design, maximizing the efficient use of pathways for data flow.Voltage Level Translators

Voltage level translators function as buffers managing signal integrity between devices that operate at different voltage levels. These buffers ensure that logic levels are translated appropriately, facilitating compatibility between 3.3V and 5V components, for instance. Such devices, like the *TXB0108*, play a crucial role in mixed-signal applications. As digital systems become more complex, the integration of various voltage levels can lead to challenges with signal integrity. Voltage level translators provide a critical solution by enabling seamless communication across different parts of an electronic circuit without risk of damaging sensitive components.Applications and Practical Considerations

In practice, the application of digital buffers extends well beyond mere signal amplification. They are fundamental in clock distribution networks, where maintaining signal integrity is vital across distributed systems. Additionally, their roles in memory interfacing, data acquisition systems, and peripheral device management underscore their versatility and necessity in modern electronics. When selecting a buffer type, engineers must consider factors such as signal propagation delay, output drive specifications, signal conditioning needs, and power consumption. These considerations will inform the choice of buffer based on system requirements, ultimately shaping device performance and reliability. Diving deeper into the specifics of buffer selection and usage leads to greater efficiency in electronic design, underscoring the significance of understanding the types, functionalities, and applications of digital buffers in today's technological landscape.2. Electrical Characteristics

2.1 Electrical Characteristics

The digital buffer is a crucial component in modern digital circuits, providing isolation and signal integrity across various functionalities. Understanding its electrical characteristics is essential for optimal circuit design and performance. This section delves into the fundamental electrical properties, laying the groundwork for analyzing how buffers can enhance signal processing and communication in complex systems.

Voltage Levels

At the core of digital buffers are their voltage levels, which determine the '1' and '0' states in digital logic. Typically, logic high (1) and logic low (0) are defined by specific voltage ranges, often influenced by the technology used (e.g., TTL, CMOS). For instance:

- TTL buffers: Logic high is generally above 2.0 V, and logic low is below 0.8 V.

- CMOS buffers: Logic levels are often between the supply voltages, with logic high being VDD (e.g., 5 V) and logic low being 0 V.

The precise definition of these levels affects noise margins, a crucial factor in ensuring successful digital communication. It can be mathematically characterized by the noise margin, which is the difference between the minimum input voltage recognized as high and the maximum input voltage recognized as low:

Here, \( NM_H \) denotes the high noise margin, while \( NM_L \) describes the low noise margin. These margins ensure that signals remain distinguishable even in the presence of noise, a vital assurance for maintaining circuit performance in real-world applications.

Current Characteristics

Current characteristics are equally important, particularly concerning output drive capabilities. A digital buffer can output a designated current rated for high logic levels, significantly impacting the performance of connected loads. This led to the specification of two critical parameters:

- Output high current (IOH): The maximum current the buffer can source when in a high state, which directly affects how many loads can be driven.

- Output low current (IOL): The maximum current it can sink when in a low state, similarly essential for driving multiple components.

The relationship can be summarized with Ohm’s Law, and power considerations can be evaluated by defining the buffer's output voltage characteristics:

Understanding these current driving capabilities allows engineers to make informed decisions on the number of devices that can be connected to each buffer output without compromising performance.

Propagation Delay

The propagation delay, defined as the time taken for an input change to reflect at the output, is another critical parameter when selecting digital buffers. It can be a significant factor in high-speed digital applications, affecting the overall timing requirements of a circuit. The propagation delay can be characterized as:

Understanding these values allows designers to effectively manage timing relationships in synchronous systems, which is particularly crucial in clocked logic circuits where timing discrepancies can lead to malfunction or data corruption.

Real-world Applications

Digital buffers are indispensable components in various applications including:

- Driving long-distance communication lines where signal integrity is crucial.

- Isolating different sections of digital circuits, thereby protecting sensitive components from voltage spikes and noise.

- Enhancing signal strength to prevent degradation in high-speed data transmission.

In essence, the electrical characteristics of digital buffers—voltage levels, current capabilities, and propagation delays—are critical metrics for managing performance in advanced electronic designs.

2.2 Timing Parameters

In the realm of digital electronics, timing parameters play a crucial role in the operation of digital buffers. A digital buffer, fundamentally, serves to strengthen and isolate signal levels, but it is the timing characteristics that dictate how effectively it accomplishes this task under varying conditions. Understanding timing parameters in the context of digital buffers becomes particularly essential when designing complex digital systems, such as microprocessors and data communication networks, where signal integrity and timing synchronization can make or break functionality.Propagation Delay

One of the primary timing parameters for any digital buffer is the propagation delay. Propagation delay is the time it takes for an input signal to cause a change at the output, typically measured from the 50% point of the input signal to the 50% point of the output signal. Mathematically, it is represented as:Static and Dynamic Timing

When examining timing parameters, it's valuable to differentiate between static and dynamic timing parameters. Static timing refers to the timing characteristics that do not change as a function of the operating conditions. This includes parameters like setup time and hold time. - Setup time is the minimum time before the clock edge by which a signal must be stable to be reliably sampled. Conversely, hold time is the minimum time after the clock edge that the signal must remain stable. Both these parameters are critical in synchronous circuits to prevent timing violations. Dynamic timing, on the other hand, refers to how these parameters might change based on operating conditions, such as temperature or voltage fluctuations. Understanding both aspects allows for more robust system design.Skew and Jitter

Another important aspect of timing parameters is skew and jitter. Skew is the difference in arrival times between signals that should theoretically arrive simultaneously. In multi-point digital buffers, skew can introduce timing mismatches that can severely impact performance, leading to data misinterpretation. Jitter refers to the variability in signal timing, which can result from multiple sources, including noise and thermal fluctuations. Jitter directly affects the performance of high-speed data transmission systems, where clock signals must remain stable to ensure proper synchronization.Practical Relevance

In practical terms, understanding timing parameters informs the design of digital systems to ensure they function correctly at required speeds without generating errors due to timing mismatches. For example, a well-designed data buffer will ensure that data signals align correctly with clock signals amidst potential variances in temperature, voltage, and load conditions. To summarize, mastering the timing parameters associated with digital buffers is fundamental for engineers and researchers engaged in high-speed signal processing and advanced digital circuit design. As these systems become increasingly complex, a nuanced understanding of these timing characteristics will become indispensable for achieving optimal performance in contemporary digital electronics.2.3 Logic Levels and Compatibility

In the context of digital buffers, understanding logic levels and compatibility is crucial for managing the interaction between various digital circuits. Logic levels refer to the specific voltage ranges that represent logical states—typically binary ‘1’ (high) and ‘0’ (low). The interpretation of these levels can change depending on the technology utilized in circuit design, such as CMOS, TTL, or ECL. The concept of logic levels in digital systems can be characterized by established voltage thresholds. For instance, in a standard TTL (Transistor-Transistor Logic) system, a logical high is defined typically between 2.0 V to 5.0 V, while a logical low spans from 0 V to 0.8 V. On the other hand, CMOS (Complementary Metal-Oxide-Semiconductor) devices may have different levels that can significantly vary, typically influenced by the supply voltage. For example, a 3.3 V CMOS device may define a high level above 2.0 V while considering levels below 1.0 V as low. Understanding these voltage levels is critical for ensuring compatibility between components. Mismatches can lead to misinterpretation of logic levels, causing incorrect circuit operation or even damage. Therefore, the careful selection of devices that operate at the same voltage levels or incorporating logic level converters is vital when integrating different technologies. The following diagram illustrates common logic level definitions for various types of digital technologies: Compatibility also extends beyond just voltage levels; it encompasses input and output impedance, signal integrity, and propagation delays. For instance, even if two devices operate at the same logic levels, significant differences in input impedance could lead to unexpected results. The input of a digital buffer generally presents high impedance, allowing it to connect to multiple sources without significant loading effects on those driving the signals. Furthermore, when two components interact—such as a buffer driving an input pin on a logic gate—engineers must consider electrical characteristics, ensuring that the output rise and fall times meet the necessary specifications for proper function. This need for synchronization underscores the importance of detailed datasheet scrutiny. In practical applications, mismatched logic levels can lead to cascading failures in digital design. An example can be drawn from microcontroller interfacing where different logic levels between the microcontroller and peripheral devices necessitate the use of voltage shifters or specific buffer ICs designed for level translation. The careful evaluation of these characteristics empowers engineers to design robust, reliable, and efficient digital systems. Ultimately, understanding logic levels and compatibility is foundational in ensuring seamless integration across digital devices. By adopting a comprehensive approach to device selection, designers can avoid pitfalls and propel their projects towards successful outcomes—laying the groundwork for complex systems reliant on precise digital logic operations.3. Signal Isolation

3.1 Signal Isolation

In the realm of digital electronics, signal isolation is a pivotal concept, especially when discussing the functions of a digital buffer. A digital buffer acts not only as a gate for data flow but also as a robust barrier between different components within a circuit. This is particularly important in applications where circuit separation is necessary to prevent unwanted coupling and interference. The essence of signal isolation lies in its ability to prevent the direct electrical connection between two circuits. This is crucial in preserving signal integrity, reducing noise, and protecting sensitive components from high-voltage spikes or fluctuations that may arise from a connected device. The digital buffer serves as an intermediary that can effectively decouple these signals, ensuring stable operation.The Mechanism of Signal Isolation

Signal isolation can be achieved through various means, such as optical isolation, capacitive isolation, or transformer-based isolation. In digital buffers, we often leverage the principle of voltage level shifting combined with logic gate functionality. Optical isolators, or optocouplers, are an example of isolators that utilize light for their operation. By converting an electrical signal into a light signal and then back into an electrical signal, a barrier is effectively established. This method prevents high voltages from affecting downstream components, safeguarding against damage and ensuring reliability. Consider an application where a microcontroller interfaces with high-voltage equipment. Direct connection risks exposing the microcontroller to potential voltage spikes. Instead, by employing a digital buffer with optical isolation, the microcontroller can operate at safe voltage levels while still controlling the high-voltage equipment.Determining Buffer Design Parameters

When designing a buffer for signal isolation, there are several critical parameters to consider:- Propagation Delay: This is the time it takes for a signal to pass through the buffer. Selecting a buffer with minimal propagation delay is essential for high-speed applications.

- Isolation Voltage: This defines the maximum voltage that can be applied across the isolation barrier without breakdown. It is crucial in protecting sensitive equipment.

- Input and Output Impedance: The input impedance should be high enough to avoid loading the source signal, while output impedance should match the following stage to prevent reflections.

3.2 Driving Capacitive Loads

In digital electronics, driving capacitive loads is a critical consideration for achieving reliable and efficient circuit performance. A digital buffer functioning as a signal repeater is not only responsible for isolating various stages from each other but also for ensuring that the output can effectively drive capacitive loads, which are prevalent in many electrical applications.

When a buffer outputs a signal to a capacitive load, the load affects not only the signal integrity but also the overall response time of the circuit. Understanding how capacitive loading influences performance necessitates an exploration of the underlying physics and electrical characteristics that govern such interactions.

Capacitive Load Characteristics

Capacitive loads can be found in various components, such as transmission lines, printed circuit boards (PCBs), and input collaterals of subsequent digital stages. These components introduce a non-negligible amount of capacitance, which can lead to several challenges, such as reduced switching speeds and signal degradation.

The key parameter when dealing with capacitive loads is the load capacitance (C), which can be defined as the total effective capacitance presented at the output node of the digital buffer. The buffer's ability to charge or discharge this capacitance significantly influences the rise and fall times of the output signal.

Charging and Discharging a Capacitive Load

When switching occurs, the buffer must charge or discharge the capacitive load, which can be described by the first-order charging equation:

Where:

- V(t): The voltage across the capacitor at time t.

- Vs: The supply voltage.

- Ron: The on-resistance of the buffer output stage.

- C: The load capacitance.

From this equation, it is evident that the time it takes to charge the capacitor—characterized by the time constant τ (tau)—is determined by the product of the on-resistance and the capacitance:

This relationship indicates that as the load capacitance increases, the time taken to reach an adequate voltage level also increases, potentially leading to slower overall circuit operation.

Practical Implications

In practical circuits, buffer design must account for the capacitive nature of the loads it drives. Engineers often consider employing buffers with low output impedance and high drive current capability to mitigate these delays. Additionally, utilizing series resistors can aid in controlling the current, thereby improving the rise and fall times by managing the rate of charging and discharging of capacitive loads.

Furthermore, the output drive capability is paramount in applications where multiple capacitive loads may be driven by a single buffer. Understanding and effectively designing to handle these capacitive loads allow for systems that operate efficiently and with fewer errors, particularly in high-speed digital applications such as data communications, high-speed computing, and RF systems.

Conclusion

Driving capacitive loads presents unique challenges in digital buffer applications, necessitating careful consideration of load parameters and buffer characteristics. As integrated circuit technology evolves, the need for innovative buffering techniques to handle increasing load demands continues to grow, highlighting the importance of this knowledge in modern electronic design.

3.3 Voltage Level Translation

Understanding Voltage Levels in Digital Circuits

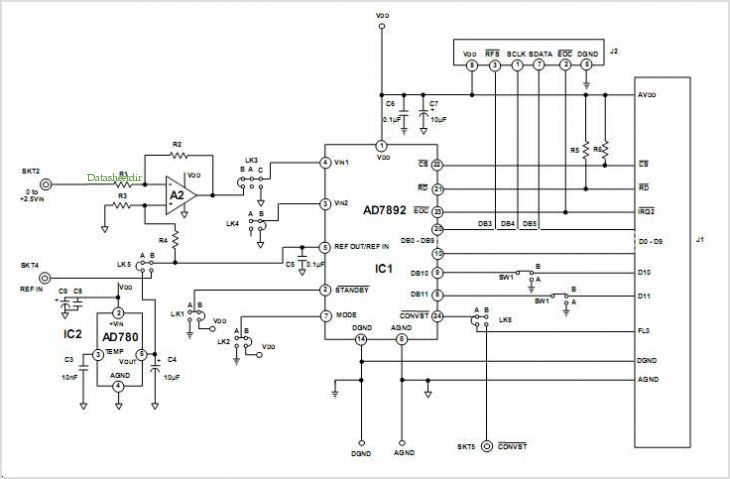

In modern digital systems, integration of components functioning at different voltage levels presents a significant challenge. As devices evolve, the voltage levels that define logic 'high' and 'low' can vary widely. For instance, a microcontroller operating at 3.3V may need to interface with a peripheral requiring 5V logic levels. Without appropriate conversion methods, this mismatch can lead to malfunction or damage of sensitive components. In this context, voltage level translation becomes essential. The primary objective of a voltage level translator is to ensure reliable communication between devices, allowing them to interpret each other's signals correctly despite operating at different voltage thresholds.Types of Voltage Level Translators

There are several approaches to voltage level translation, each suited for different applications. The main categories include:- Active Level Translators: Use transistors or dedicated ICs to shift voltage levels actively. They are suitable for high-speed applications and can accommodate bidirectional data flow. A common example is the BSS138 transistor level shifter.

- Passive Level Translators: Rely on resistors for voltage division and are often simpler and more cost-effective, although they may not support high-speed signals. An example is using resistors in a pull-up configuration for I2C communication.

Active Voltage Level Translation: A Closer Look

For active level translation, consider a common scenario involving a BSS138-based level shifter. The device operates on the principle of dynamic switching using field-effect transistors (FETs). To conceptualize this, imagine two voltage levels: Vhigh for the higher voltage side (5V) and Vlow for the lower voltage side (3.3V). When an input signal arrives on the Vlow side, the resistor network and FET configuration ensure that the output reflects the correct high or low state dictated by the input. The basic operation can be summarized in the following equations, assuming ideal conditions: 1. When the input is high (3.3V): $$ V_{out} (high) = V_{high} $$ 2. When the input is low (0V): $$ V_{out} (low) = V_{low} $$ This method accommodates bidirectional communication, which is particularly useful in protocols like I2C or UART where devices may need to send and receive data interchangeably.Derivation for Signal Translation

To understand how we derive the output voltage in terms of input voltage, we can set up a simple relationship based upon the MOSFET's operation in the cutoff and saturation regions. 1. In cutoff when Vin = 0V: - The FET remains OFF, pulling Vout to ground: $$ V_{out} = 0V $$ 2. In saturation when Vin = high: - The FET turns ON, connecting Vout to Vhigh: $$ V_{out} = V_{high} $$Practical Applications

Successful voltage level translation is pivotal in various applications, including:- I2C Communication: Commonly used in sensors and devices requiring low-speed communication, where different devices may operate at different voltage levels.

- UART Interfaces: Used extensively in serial communication, levels must be translated to ensure proper data interpretation.

- Integrating Legacy Systems: Older devices that utilize higher voltage levels can communicate seamlessly with newer, lower-voltage circuits via specialized level shifters.

- Embedded Systems Tailoring: Custom designs where microcontrollers need to interact with multiple subsystems across varied voltage specifications.

4. Selection Criteria for Buffers

4.1 Selection Criteria for Buffers

In the realm of digital electronics, selecting an appropriate buffer is critical for ensuring robust signal integrity and optimum performance in various applications. Buffers, often found in logic circuits, serve to isolate different parts of a system, provide impedance matching, and enhance driving capabilities. With this understanding, the selection criteria for buffers become pivotal, especially for advanced applications requiring high reliability and performance. One primary consideration in buffer selection is the input and output voltage levels. Buffers must operate reliably within the specified logic level thresholds of the systems they interface with. For instance, while standard TTL (Transistor-Transistor Logic) levels operate typically at 0V to 5V, CMOS (Complementary Metal-Oxide-Semiconductor) buffers may interface at levels such as 0V to 3.3V or even 0V to 15V, depending on the technology used. Advanced applications may require buffers that can accommodate varying voltage levels appropriately by utilizing buffers with adjustable level thresholds or multi-voltage compatibility. Another crucial factor is the buffer's propagation delay, which is the time taken for an input change to reflect at the output. For high-speed applications, such as those in synchronous digital circuits, minimizing propagation delay becomes essential to maintain the integrity of clock signals and data flow. The propagation delay can vary significantly among different buffer types; thus, examining the datasheet specifications is vital to ensure it meets the requirements of the intended application. For instance, buffer ICs optimized for high performance may offer propagation delays in the range of nanoseconds. The drive strength of the buffer is also a significant criterion. This refers to the buffer's ability to produce output currents necessary to drive larger capacitive loads while maintaining signal integrity. Ensuring that the selected buffer can handle the necessary load without significant voltage drop or distortion is vital, particularly when interfacing with multiple inputs or outputs. You gain this information primarily from the buffer's datasheet, which typically provides details on output current specifications. Additionally, power consumption can be a decisive factor, particularly in battery-powered or energy-sensitive applications. Buffers generally fall into two categories: static and dynamic. Static buffers, while providing constant output impedance and quicker switching, tend to consume more power continuously. In contrast, dynamic buffers can exhibit lower power consumption in idle states, but they may require careful consideration regarding charging and discharging times due to their reliance on clock signals for operation. The noise margin is another significant consideration. Buffers should have adequate noise margins to withstand variations and interference in real-world operating conditions. This is typically characterized in datasheets as a measurement of the maximum allowable noise voltage that can be superimposed on the signal without causing incorrect response. Selecting buffers with robust noise margins ensures that critical signals remain unaffected by fluctuations commonly present in electronic environments. In practical applications, the choice of buffer can markedly affect system performance. For instance, using a buffer in a data transmission line can help maintain signal integrity over long distances, as seen in high-speed communication systems. The right buffer can prevent reflections and losses often encountered in such scenarios, ultimately improving the reliability of data transmission. In conclusion, the selection of a digital buffer hinges on several essential criteria, encompassing voltage levels, propagation delays, drive strengths, power consumption, and noise margins. A thorough understanding of these factors allows engineers and researchers to make informed decisions that align with the performance and reliability requirements of their specific applications. Additionally, employing simulation tools can aid in the optimization of buffer selection and integration, enabling engineers to visualize circuit responses under various load conditions and input signals. Understanding these selection criteria further emphasizes the intricacies of modern electronic design, highlighting the importance of buffer technology in ensuring the seamless operation of digital systems across varying applications.4.2 Circuit Design Examples

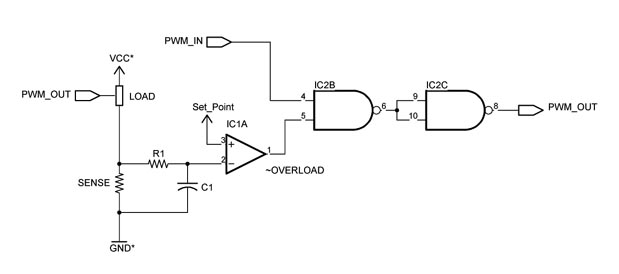

The digital buffer, a crucial component in modern digital systems, serves to isolate circuits, enhance signal integrity, and improve drive capability. In this section, we will delve into practical circuit design examples, illustrating how to implement various buffer configurations effectively.

4.2.1 CMOS Buffer Design

A complementary metal-oxide-semiconductor (CMOS) buffer is a popular choice due to its high noise margins and low static power consumption. The basic configuration involves a PMOS and NMOS transistor connected in series where the input is fed to the gates of both transistors. Here, the output is taken from the common drain of the transistors.

The transfer characteristics of a CMOS buffer can be derived by analyzing the behavior of the PMOS and NMOS transistors in their respective active regions. When the input voltage (Vin) is low (0V), the NMOS is off (non-conducting) while the PMOS turns on, allowing Vout to rise to VDD. Conversely, when Vin is high (approaching VDD), the NMOS turns on, pulling Vout down.

Mathematically, the output voltage can be described as:

Here, \( V_{Tn} \) is the threshold voltage of the NMOS and \( V_{Tp} \) is the threshold voltage of the PMOS.

4.2.2 Tri-State Buffer

Another useful configuration is the tri-state buffer, which allows for three distinct output states: high, low, and high impedance (Z). This is essential in bus systems where multiple devices need to share a common data line without interference.

The tri-state buffer integrates an enable signal, which controls whether the input can pass to the output. When enabled (high), the input signal appears at the output. Conversely, if disabled (low), the output remains in a high-impedance state, effectively disconnecting it from the bus.

The tri-state buffer inverts the logic levels, providing both active high and active low functionalities. This can be expressed as follows:

4.2.3 Practical Implementation Example

For practical implementation, consider designing a buffer using the 74HC125 quad buffer/driver IC. This IC can drive loads while maintaining signal integrity and reducing noise susceptibility. The pin configuration includes four independent buffers, each capable of tri-state operation.

To construct a simple circuit, connect the input signal to one of the data inputs while tying the enable pin to a logic high. The resulting circuit will solidify the connection between input and output while providing isolation when the enable pin is low. This is particularly advantageous in microcontroller applications where multiple sensors or components must share GPIO pins.

For simulation, you can utilize software like SPICE to analyze the performance of these buffer designs under various load conditions and input frequencies, ensuring robust designs that meet desired specifications. The output waveform can then be analyzed to assess delays, rise/fall times, and power dissipation, aligning with system-level requirements.

Understanding these buffer configurations is paramount for advanced circuit design and digital system integration, allowing engineers to optimize performance in complex applications.

4.3 Simulation and Testing

In the realm of digital electronics, simulation and testing are essential practices for ensuring that a digital buffer operates correctly within a given circuit. With the rapid evolution of semiconductor technology and electronic design automation (EDA) tools, engineers and researchers can simulate complex behaviors well before prototyping. This section delves into both the simulation methodologies and practical testing approaches for digital buffers, equipping you with the knowledge to effectively validate designs.

Simulation Techniques

Digital buffers, serving as crucial elements in circuit design, can be simulated using various software tools such as SPICE, ModelSim, and LTspice. The essence of these simulations lies in their capability to model the electrical characteristics of the buffers under different conditions. A key starting point in simulation is understanding the buffer's transfer characteristics, represented by the voltage transfer curve.

The fundamental equations to model the output voltage ($${V}_{out}$$) of a digital buffer based on its input voltage ($${V}_{in}$$) typically follow:

Here, $${V}_{DD}$$ is the supply voltage, $${V}_{th}$$ is the threshold voltage, and $${V}_{tl}$$ is the noise margin voltage. By simulating these parameters, designers can predict how the buffer will react under various input conditions.

Creating a SPICE Model

In a SPICE simulation, buffers can be modeled by defining a voltage source for the input and analyzing the output at different loading conditions. The SPICE netlist would typically look like this:

* Buffer SPICE Model

VDD 1 0 DC 5V

Vin 2 0 PULSE(0 5 0 10n 10n 100n 200n)

M1 3 2 0 0 NDS 1u

C1 3 0 1n

R1 3 0 10kThis snippet indicates a basic buffer setup using a MOSFET with input and output defined. The analysis can offer insights into rise and fall times alongside propagation delays.

Physical Testing of Digital Buffers

Upon completing the simulation phase, physical testing is paramount for validating the designed buffers. Standard practices usually involve using an oscilloscope, logic analyzer, and multimeter. These instruments are vital for measuring output characteristics like rise/fall times and propagation delays, further ensuring they meet specifications.

- Rise and Fall Time Analysis: This involves measuring the time it takes for the output to change from low to high and vice versa. A properly functioning buffer should have rise and fall times significantly lower than the specified threshold.

- Loading Conditions: Testing under various load conditions (capacitive, resistive) is essential to understand how the buffer performs when interfaced with other circuit elements.

In real-world applications, digital buffers play critical roles ranging from data line isolation in communication protocols to power domain isolation in mixed-signal systems. By ensuring that a buffer operates reliably under simulated and physical conditions, the integrity and functionality of the overall design are safeguarded.

In conclusion, embracing both simulation tools and practical testing methodologies is important for engineers working with digital buffers. As technology advances, these techniques will become increasingly vital for managing the complexities of high-speed digital designs.

5. Buffers vs. Inverters

5.1 Buffers vs. Inverters

In digital electronics, understanding the roles of buffers and inverters is crucial due to their fundamental presence in logic design and signal management. Both of these devices manipulate digital signals, but they accomplish their goals in distinctly different ways—each serving different functional purposes in complex circuits.Understanding Buffers

A digital buffer serves as an intermediary between signals, providing increased drive capability without altering the logical state of the input. Specifically, a buffer outputs the same voltage level as its input but can provide greater current to drive subsequent stages, effectively isolating different components of a circuit. Buffers are essential in applications where signal degradation might compromise performance, such as in long-distance transmission lines or complex digital designs, which require reliable signal integrity. The operation of a simple buffer can often be modeled as: $$ V_{out} = V_{in} $$ where \( V_{out} \) is the output voltage, and \( V_{in} \) is the input voltage. This equation illustrates that the output follows the input without transformation, preserving the original logical value.Understanding Inverters

Conversely, an inverter is a fundamental digital logic gate that outputs the logical opposite of its input. If the input is high (logic level '1'), the inverter outputs low (logic level '0'), and vice versa: $$ V_{out} = \begin{cases} 0 & \text{if } V_{in} = 1 \\ 1 & \text{if } V_{in} = 0 \end{cases} $$ This transformation is crucial for creating the necessary negative logic signals for specific conditions in digital circuits. For instance, in CMOS technology, inverters are indispensable for implementing NOT operations and are often used in conjunction with buffers to facilitate complex logic operations in synchronous circuits.Practical Relevance and Applications

The applications for buffers and inverters are broad and nuanced within digital systems. Buffers are frequently employed in:- Driving high-capacitance loads in communication interfaces.

- Line buffering in data transmission protocols, ensuring signal integrity over distances.

- As isolation devices in mixed-signal systems to prevent analog noise from affecting digital circuits.

- Arithmetic operations in arithmetic logic units (ALUs).

- Creating feedback loops in control systems, essential for stability analysis.

- Forming flip-flops when combined with additional gates, crucial for memory storage and state retention.

5.2 Buffers vs. Amplifiers

In the realm of electronics, the distinction between buffers and amplifiers can often be nuanced yet profound. While both serve critical roles in signal processing, their fundamental purposes, configurations, and behaviors vary significantly. Understanding these differences is pivotal for engineers and physicists aiming to optimize circuit designs and signal integrity.

Buffers are primarily utilized for impedance matching, which allows devices with different impedance levels to communicate effectively without signal degradation. A digital buffer, often categorized as a unidirectional logic device, optimally isolates segments of circuits, providing a strong output signal that is capable of driving loads that exceed the input stage’s current capacity. This is visually represented as a square wave, maintaining voltage levels high enough to prevent interference from arising at the source. For example, consider using a buffer to connect a microcontroller output to a higher capacitance load, where the load would otherwise reduce the signal integrity.

On the contrary, amplifiers are designed to increase the amplitude of a signal. Unlike buffers, which maintain the original signal form, amplifiers can modify the signal, making them particularly invaluable in audio and communication applications. A common type of amplifier is the operational amplifier (op-amp), which can produce a larger output signal proportional to its input. The gain of an amplifier, often defined by the formula:

where \(A_v\) is the voltage gain, effectively portrays the amplifier's ability to replicate the input voltage at a larger scale. The design of amplifiers accommodates various configurations such as inverting, non-inverting, and differential modes, each suitable for specific applications based on the desired gain and bandwidth.

When discussing key differences between buffers and amplifiers, consider the following aspects:

- Functionality: Buffers are about signal isolation and impedance matching, while amplifiers focus on signal amplification.

- Output Behavior: Buffers provide a high-quality replica of the input signal, while amplifiers can modify the signal level.

- Signal Integrity: Buffers maintain signal integrity across loads, preventing interaction between different circuit stages.

- Design Complexity: Buffers are generally simpler and require fewer components than amplifiers, which might include feedback mechanisms and complex gain settings.

From a practical viewpoint, both devices can coexist in sophisticated electronic systems. For instance, in a mixed-signal circuit involving microcontrollers and analog sensors, buffers can be utilized to interface digital outputs and sensitive analog inputs without causing loading effects that may distort readings. Analog front-end circuitry, complemented by amplifiers, can further enhance signal strength before digital conversion, thus ensuring accurate data transmission.

In summary, while buffers and amplifiers can occasionally serve overlapping roles, particularly in multi-functional integrated circuits, their core responsibilities, operation modes, and circuits differ significantly. A comprehensive understanding of these components aids in effective circuit design and implementation, reinforcing the integrity and quality of electronic signals throughout various applications.

6. Emerging Technologies

6.1 Emerging Technologies

Introduction to Emerging Technologies in Digital Buffers

The landscape of digital buffers is rapidly evolving, driven by advancements in semiconductor technology, novel materials, and innovative circuit design methodologies. As the demand for higher data rates and lower power consumption intensifies, traditional buffering solutions are giving way to a range of emerging technologies. This section explores these innovative developments and their implications for the future of digital buffering.Quantum Dot Cellular Automata (QCA)

One of the most intriguing emerging technologies is Quantum Dot Cellular Automata (QCA). Unlike conventional CMOS technology, which relies on the flow of electrons, QCA operates using the quantum properties of semiconductor quantum dots. The fundamental building block of QCA is a cell composed of four quantum dots. Information is represented through the arrangement of electrons in these dots rather than by voltage levels. The major advantages of QCA include:- Low power consumption: QCA devices can operate at significantly lower voltages, which reduces power dissipation.

- High density: QCA is capable of achieving higher integration densities than traditional CMOS circuits.

- Inherent parallelism: The nature of QCA allows for parallel data processing, enhancing speed and efficiency.

Carbon Nanotube Transistors (CNTs)

Carbon Nanotube Transistors have emerged as a potential replacement for traditional silicon-based transistors. These devices utilize the unique electrical properties of carbon nanotubes, which can be made to function as either conductors or semiconductors. The high charge carrier mobility in CNTs leads to faster switching speeds and lower power requirements. Key characteristics include:- Scalability: CNTs can be fabricated at a nanoscale, promising continuing improvements in transistor density.

- Thermal stability: Unlike silicon, which can suffer from heat sensitivity, CNTs maintain performance at elevated temperatures.

- Flexibility: CNTs can be integrated with flexible substrates, enabling new form factors for electronic devices.

Memristors

Memristors represent another frontier in digital buffer technology, characterized as a non-volatile memory component. By exhibiting a resistance that is dependent on the charge that has previously passed through it, memristors can remember past states even when powered off. This unique property enables the potential for reconfiguration in buffering applications. The practical implications are profound:- Energy efficiency: Memristors consume significantly less power compared to traditional memory solutions.

- Speed: They offer faster access times due to their analog nature, which allows them to operate without the latency caused by mechanical storage.

- Integration with logic functions: Memristors can perform both storage and logic processing in the same device.

Neuromorphic Computing

Neuromorphic computing mimics the architecture and functioning of the human brain to improve computation and efficiency. In this paradigm, digital buffers are designed to function more like synapses, providing the ability to store and process information in a manner that significantly resembles human cognitive processes. Advantages of neuromorphic digital buffers include:- Enhanced learning capabilities: They can adapt to new information on-the-fly, improving overall efficiency and response time.

- Lower power consumption: Mimicking biological processes often leads to dramatic reductions in energy usage as compared to conventional digital systems.

- Real-time processing: They enable faster processing of sensory data, vital for applications in autonomous systems and artificial intelligence.

Conclusion

Digital buffers are on the cusp of transformation as emerging technologies like QCA, CNTs, memristors, and neuromorphic computing pave the way for revolutionary advancements. These technologies not only promise to improve the performance and efficiency of buffers but also expand the boundaries of what is possible in electronic signaling and data processing. As we continue to explore these avenues, the future of digital buffering looks to be as exciting as it is promising.6.2 Integration with Other Components

In the realm of digital electronics, the digital buffer serves as a fundamental component, transforming and reinforcing signals within a circuit. Its functionality extends beyond merely serving as a passive link; it integrates seamlessly with a range of other components, facilitating complex operations and improving overall circuit performance. This section delves into the practical considerations and methodologies involved in integrating digital buffers with resistors, capacitors, logic gates, and microcontrollers.

Connecting Digital Buffers with Passive Components

Resistors and Capacitors are often used in conjunction with digital buffers to shape signal integrity. For example, when buffering a signal in a high-speed data line, it's essential to consider the effect of parasitic capacitance and resistive loading. In such scenarios, a resistor-capacitor (RC) network can be deployed to manage rise and fall times, ensuring the digital buffer can output a cleaner signal. This is crucial in applications such as telecommunications, where signal fidelity can significantly affect data transmission rates.

In cases where a digital buffer is buffering a rapidly changing signal, the incorporation of a resistor in series can limit current and manage signal reflections, while a capacitor in parallel can filter out high-frequency noise. The values of these components should be selected based on the desired bandwidth and timing characteristics of the system. The analysis can be performed using circuit simulation software to optimize the values before final implementation.

Integration with Logic Gates

Digital buffers also find versatile applications when integrating with logic gates. They can serve to isolate logical sections of circuits, thereby preventing drag or loading effects that can occur when direct connections are made between gates. By placing a buffer between two gates, one can achieve greater drive strength and improved noise margins. For example, in a cascading configuration where an output of one logic gate feeds into the input of another, a buffer can ensure that the output maintains proper voltage levels, thus enhancing the reliability of the circuit.

To exemplify this, consider integrating a buffer between a low-power CMOS gate and a high-load TTL input. The buffer allows for the CMOS gate to drive the TTL input's higher current demand without compromising its own operational characteristics. This cascading arrangement significantly enhances the interoperability of components from different logic families, promoting extensive versatility in design.

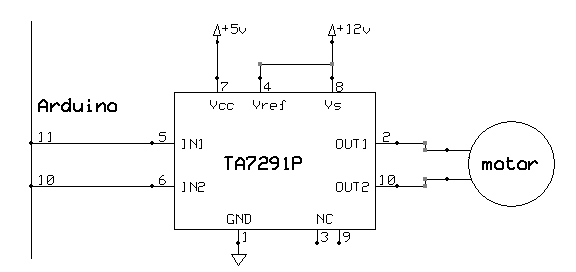

Interfacing with Microcontrollers

When interfacing buffers with microcontrollers, it is essential to consider signal levels and communication protocols. Digital buffers can interface various microcontroller outputs, reinforcing signals that drive external devices such as sensors, displays, or communication peripherals. Additionally, they often act as line drivers for long-distance signal transmission, ensuring the integrity of the data over potentially noisy environments like automotive or industrial applications.

For instance, when a microcontroller needs to send signals to multiple outputs, the inclusion of buffers can facilitate simultaneous driving of multiple devices without significant voltage drop or delay. It is critical to assess the input/output specifications of both the microcontroller and the buffered device to prevent damage or functional degradation. Consequently, careful attention must be paid to the choice of buffer type, capacitive load, and feedback mechanisms to maintain robust communication throughout the system.

Conclusion

Integration of digital buffers with passive components, logic gates, and microcontrollers is not just a matter of connection—it's a strategic stage in circuit design that enhances performance and reliability. The judicious application of buffers allows for tailored circuit configurations to meet varying design specifications. By considering the broader system interactions and potential pitfalls associated with signal integrity, engineers can leverage digital buffers to build efficient, effective circuitry suited to complex applications.

7. Recommended Textbooks

7.1 Recommended Textbooks

- Digital Fundamentals by Thomas L. Floyd — A comprehensive guide covering digital electronics principles, including digital buffers. It explores logic gates, circuits, and applications with detailed examples.

- Digital Design: Fundamentals of Digital Logic with VHDL Design — Focuses on logic design and implementation strategies using VHDL. Provides insights into buffer design, signal integrity, and FPGA applications.

- Digital Design: Principles and Practices by John F. Wakerly — Offers an in-depth analysis of digital systems, including thorough treatment of digital buffers, from basic to advanced concepts.

- Digital Logic and Computer Design by M. Morris Mano — Covers foundational concepts in digital logic, encompassing digital buffers, sequential circuits, memory devices, and more.

- Digital Systems: Principles and Applications by Ronald J. Tocci — Details practical applications of digital systems, with discussions on buffer circuits and signal transmission.

- Digital Logic Design by B. S. Givone — Explores algorithms used in digital design and synthesis, with practical approaches to using buffers in logic circuits.

- Mixed Signal and DSP Design Techniques by Walt Kester — While focused on mixed-signal and DSP, this text provides a valuable context for understanding inter-system communication, where buffers play a significant role.

7.2 Online Resources

- Electronics Tutorials — Digital Buffer — Comprehensive guide on digital buffers, how they function in digital circuits, and their significance in enhancing signal strength.

- All About Circuits — Buffers, Inverters, and Drivers — Detailed exploration of digital logic elements, focusing on buffers and their role in digital circuits, including practical applications and examples.

- SparkFun Electronics — Digital Logic: Buffers — Overview and historical context of digital buffers, providing insights into their evolution and functionality within modern electronics.

- Texas Instruments — Logic Buffers & Drivers Guide — Technical reference document from Texas Instruments detailing buffer functionality, specifying use-cases, operation parameters, and integration with other ICs.

- ScienceDirect — Digital Buffer — Peer-reviewed articles and academic research discussing digital buffers, with specific focus on advanced applications and theoretical models.

- Circuit Digest — Digital Logic Gates and Buffers — Educational resource providing foundational and advanced insights into logic gates and buffers, integrating schematic diagrams and simulations.

- Mouser Electronics — Introduction to Buffers — Guide aimed at helping engineers understand buffer types and characteristics, tailored for practical application in real-world circuit design.

7.3 Scientific Journals

- IEEE Xplore: Digital Buffer Design — Offers insights into digital buffer design in diffractive optical elements, illustrating advances in digital buffering technologies.

- ACM Digital Library: High-Speed Digital Buffer Solutions — Discusses high-speed digital buffer implementations in computer networks, with evaluations on performance improvements.

- SAGE Journals: Digital Buffers in Electronic Design — Explores the applications of digital buffers in electronic circuit design, providing case studies and theoretical discussions.

- ScienceDirect: The Role of Buffers in Modern Devices — Analyzes the role of digital buffers in improving efficiency and signal integrity in modern electronic devices.

- IET Digital Library: Advances in Buffer Circuitry — Offers a comprehensive review of advancements in buffer circuit design and their impact on electronic systems.

- Elsevier Microelectronics Journal — Provides numerous articles and research papers on the innovations and practical challenges in digital buffer designs.

- Springer: Enhanced Digital Buffers for Circuit Applications — Discusses new techniques in crafting digital buffers to improve speed and reliability in circuit applications.