Digital-logic-probe

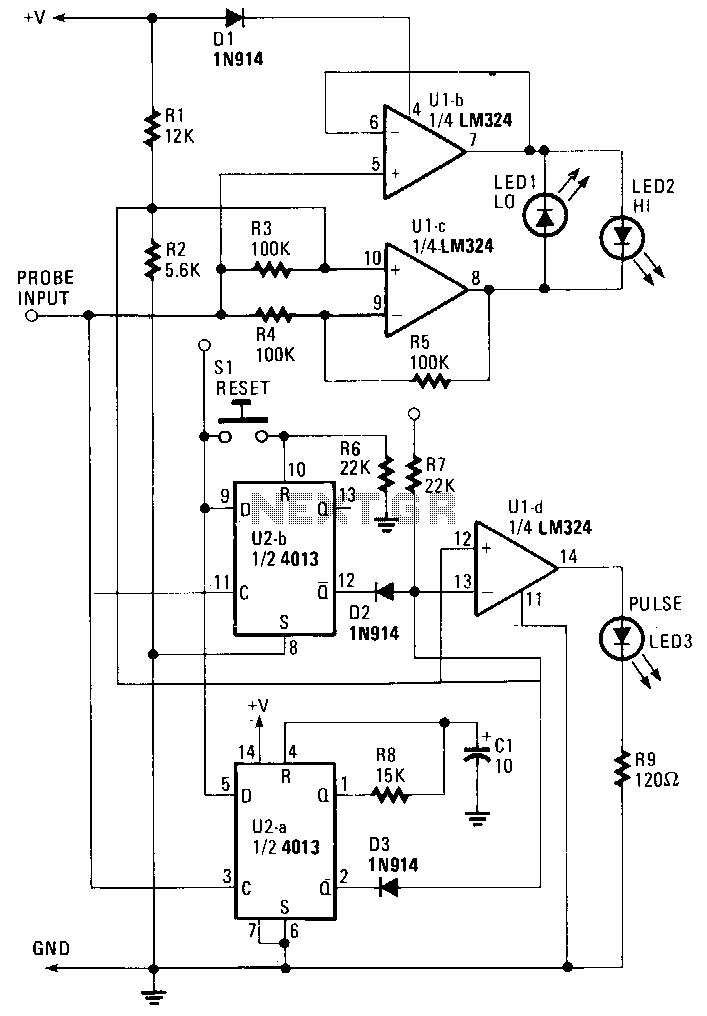

The probe operates using the power supply from the circuit under test (CUT). The input at the probe tip is divided into two pathways. One pathway directs the signal to the clock inputs of U2a and U2b. The other pathway connects to the inverting input of U1c, which functions as an inverting-mode integrator, and the non-inverting input of U1b, configured as a non-inverting unity-gain amplifier, initially set to a logic-low state. This low state, which is below the reference voltage at pin 10, results in a high output at pin 7 of U1b.

When U1b outputs low and U1c outputs high, LED1 is forward-biased and illuminates, while LED2 remains reverse-biased and dark. If the logic level at the same pin transitions to high, this high state is applied to pin 5 of U1b, causing its output to become high. Consequently, LED2 becomes forward-biased and lights up, while LED1 is reverse-biased and turns off. If a clock frequency is detected at the probe input, LED1 and LED2 will alternate illumination, potentially appearing constantly lit depending on the frequency of the input signal. This frequency is also fed into the clock inputs of both flip-flops, resulting in the Q outputs of U2a and U2b alternating between high and low states. Each time the Q outputs of the two flip-flops drop, the output of U1d increases, illuminating LED3 and indicating the detection of a pulse stream.

The described circuit employs a probe that utilizes the power supply of the circuit under test, enhancing its utility in diagnostics and testing applications. The signal at the probe tip is effectively split into two distinct pathways, allowing for simultaneous processing of the input signal. The first pathway feeds the clock inputs of two flip-flops (U2a and U2b), which are integral to the circuit's operation, enabling the detection of alternating signals.

The second pathway serves dual functions: it feeds the inverting input of U1c, which acts as an integrator, and the non-inverting input of U1b, which operates as a unity-gain amplifier. The configuration of U1b ensures that when the input signal is low, the output becomes high, thus activating LED1. Conversely, when the input signal transitions to high, LED2 is activated while LED1 turns off, demonstrating a clear visual indication of the logic state.

The incorporation of LEDs as indicators provides a straightforward visual feedback mechanism for the circuit's operational status. The alternating illumination of LED1 and LED2 in response to detected clock frequencies indicates the dynamic nature of the input signal and the circuit's ability to respond to varying frequencies. The output from the flip-flops, which alternates based on the clock signal, further enhances the circuit's capability to detect pulse streams, with LED3 providing a clear indication of this detection.

This design exemplifies a robust approach to signal processing in electronic testing environments, facilitating the observation of signal characteristics through visual indicators, and ensuring that the circuit under test can be monitored effectively in real-time.The probe relies on the power supply of the CUT (circuit-under-test). The input to the probe, at probe tip, is fed along two paths. One path flows to the clock inputs of U2a and U2b. The other path feeds both the inverting input of Ulc, which is set up as an inverting-mode integrator, and the noninverting input of Ulb, which is configured as a noninverting unity-gain amplifier, in a logic-low state. That low, below the reference set at pin 10, causes Ulb"s output at pin 7 to become high. With Ubl outputting low and Ulc outputting high, LEDl is forward-biased, and lights. LED2, reverse-biased, remains dark. Suppose that the logic level on the same pin becomes high. That high is applied to pin 5 of Ulb, causing its output to be high. LED2 is now forward-biased and lights, while LEDl is reverse-biased and becomes dark. Assume that a clock frequency is sensed at the probe input; LEDl and LED2 alternately light, and depending on the frequency of the signal, can appear constantly lit. That frequency, which is also applied to the clock input of both flip-flops, causes the Q outputs of U2a and U2b to simultaneously alternate between high and low.

Each time that the Q outputs of the two flip-flops decrease, the output of Uld increases, lighting LED3, indicating that a pulse stream has been detected.

When U1b outputs low and U1c outputs high, LED1 is forward-biased and illuminates, while LED2 remains reverse-biased and dark. If the logic level at the same pin transitions to high, this high state is applied to pin 5 of U1b, causing its output to become high. Consequently, LED2 becomes forward-biased and lights up, while LED1 is reverse-biased and turns off. If a clock frequency is detected at the probe input, LED1 and LED2 will alternate illumination, potentially appearing constantly lit depending on the frequency of the input signal. This frequency is also fed into the clock inputs of both flip-flops, resulting in the Q outputs of U2a and U2b alternating between high and low states. Each time the Q outputs of the two flip-flops drop, the output of U1d increases, illuminating LED3 and indicating the detection of a pulse stream.

The described circuit employs a probe that utilizes the power supply of the circuit under test, enhancing its utility in diagnostics and testing applications. The signal at the probe tip is effectively split into two distinct pathways, allowing for simultaneous processing of the input signal. The first pathway feeds the clock inputs of two flip-flops (U2a and U2b), which are integral to the circuit's operation, enabling the detection of alternating signals.

The second pathway serves dual functions: it feeds the inverting input of U1c, which acts as an integrator, and the non-inverting input of U1b, which operates as a unity-gain amplifier. The configuration of U1b ensures that when the input signal is low, the output becomes high, thus activating LED1. Conversely, when the input signal transitions to high, LED2 is activated while LED1 turns off, demonstrating a clear visual indication of the logic state.

The incorporation of LEDs as indicators provides a straightforward visual feedback mechanism for the circuit's operational status. The alternating illumination of LED1 and LED2 in response to detected clock frequencies indicates the dynamic nature of the input signal and the circuit's ability to respond to varying frequencies. The output from the flip-flops, which alternates based on the clock signal, further enhances the circuit's capability to detect pulse streams, with LED3 providing a clear indication of this detection.

This design exemplifies a robust approach to signal processing in electronic testing environments, facilitating the observation of signal characteristics through visual indicators, and ensuring that the circuit under test can be monitored effectively in real-time.The probe relies on the power supply of the CUT (circuit-under-test). The input to the probe, at probe tip, is fed along two paths. One path flows to the clock inputs of U2a and U2b. The other path feeds both the inverting input of Ulc, which is set up as an inverting-mode integrator, and the noninverting input of Ulb, which is configured as a noninverting unity-gain amplifier, in a logic-low state. That low, below the reference set at pin 10, causes Ulb"s output at pin 7 to become high. With Ubl outputting low and Ulc outputting high, LEDl is forward-biased, and lights. LED2, reverse-biased, remains dark. Suppose that the logic level on the same pin becomes high. That high is applied to pin 5 of Ulb, causing its output to be high. LED2 is now forward-biased and lights, while LEDl is reverse-biased and becomes dark. Assume that a clock frequency is sensed at the probe input; LEDl and LED2 alternately light, and depending on the frequency of the signal, can appear constantly lit. That frequency, which is also applied to the clock input of both flip-flops, causes the Q outputs of U2a and U2b to simultaneously alternate between high and low.

Each time that the Q outputs of the two flip-flops decrease, the output of Uld increases, lighting LED3, indicating that a pulse stream has been detected.