I2C Bus I2C Interface description

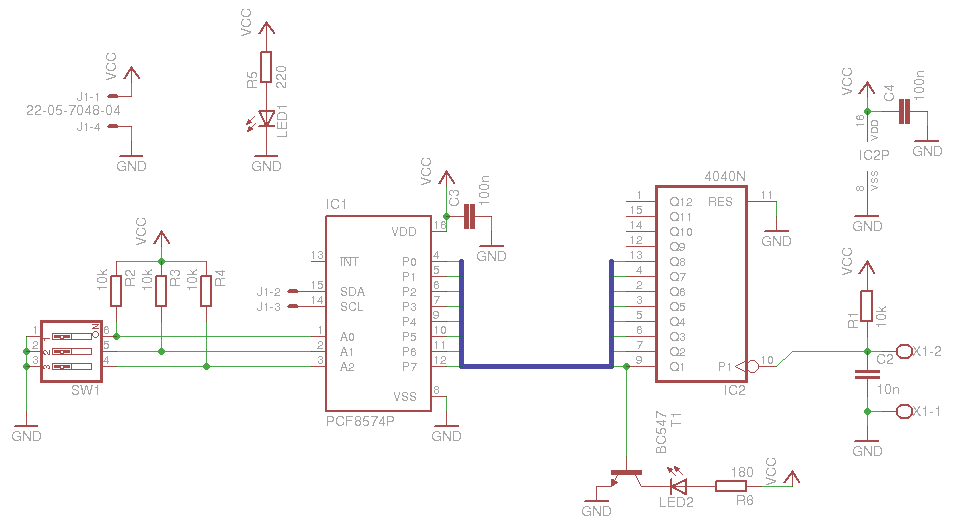

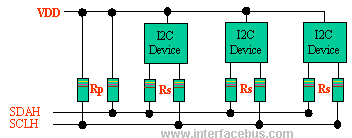

The I2C bus employs a bi-directional Serial Clock Line (SCL) and Serial Data Line (SDA). Both the SCL and SDA lines are pulled high using a pull-up resistor (Rp). An optional resistor (Rs) is utilized for ESD protection in hot-swap devices. No additional lines are specified. Any device can function as a Transmitter or Receiver, and as a Master or Slave. Data and clock signals are transmitted from the Master while the clock line is high. The bus can accommodate multiple Masters and Slaves, but only one Master can be active at any time. I2C Slaves can either receive or transmit data to the Master. Due to its two-wire configuration (one clock and one data line), I2C communication is half-duplex. The maximum bus capacitance is 400pF, which limits the number of devices and the length of the I2C bus. The interface utilizes 8-bit long bytes, with the Most Significant Bit (MSB) transmitted first, and each device assigned a unique address. Data on the SDA line changes only when the SCL line is low. A start frame is indicated when SDA drops while SCL is high, and a stop condition is indicated when SDA rises while SCL is high. The Start condition signals the beginning of a frame, while the Stop condition marks the end. Each transfer on the I2C bus consists of 9 bits: eight data bits followed by a 1-bit acknowledgment. The listener acknowledges receipt of the byte in two ways: by overwriting the 1-bit with a 0-bit to indicate readiness for more data, or by leaving the trailing 1-bit to indicate it is not ready. The Master (talker) generates both the clock and the message. An I2C message starts with a Start bit, followed by a 7-bit Slave address and a direction bit (1 for Read, 0 for Write). Upon receiving the slave address, the slave must respond; otherwise, the Master will send a Stop or Retry bit. If the Master sends a Write bit, it follows with a sub-address to specify a particular register. The slave ceases acknowledgment after the last byte of the transfer. It is important to note that the I2C bus has a maximum capacitance of 400pF, which defines the maximum number of I2C components and the bus length. The I2C bus length is not explicitly defined in the specifications; however, if the bus lines on a PCB or ribbon cable exceed 10 cm and include VDD and VSS lines, the recommended wiring pattern is SDA - [Power/Ground or Ground] - SCL. Alternatively, if VDD and VSS lines are embedded within the PCB, they may be omitted. Twisted pair or shielded cables may also be used, but the cable length will depend on the cable type (and its capacitance) and the number of I2C devices. The voltage (VDD) can vary between devices, but all devices must relate their output levels to the voltage provided by the pull-up resistors (Rp). It is possible to operate with two different bus voltages, but translation is required (refer to the specifications). The I2C serial interface illustrates the pull-up resistor connected to VDD (supply voltage). The I2C bus is also known as the Inter-IC Bus or the IIC Bus, with I2C being the most commonly used term. Other references include I2C Serial Port, I2C Digital Interface, I2C Interface, or I2C Interface Specification.

The I2C bus architecture is a popular choice for inter-device communication in embedded systems due to its simplicity and versatility. The two-wire configuration allows for efficient use of PCB space and minimizes wiring complexity. The pull-up resistors (Rp) are critical in ensuring that the SCL and SDA lines are maintained at a high logic level when not actively driven low by any device. The optional ESD protection resistor (Rs) enhances the robustness of the system, particularly in environments where devices may be hot-swapped.

In terms of data transmission, the half-duplex nature of I2C means that devices cannot send and receive data simultaneously, which is a trade-off for the simplicity of the two-wire interface. The acknowledgment mechanism is a vital part of the protocol, ensuring that data integrity is maintained. The Master device controls the timing of the communication and initiates data transfers, which is essential for coordinating the interactions between multiple devices on the bus.

The unique addressing scheme allows for a theoretically large number of devices on the bus, although practical limitations such as bus capacitance and physical layout must be considered. The maximum bus capacitance of 400pF effectively limits the number of devices that can be connected, and careful attention must be paid to the layout of the PCB or cable to maintain signal integrity.

In applications where devices operate at different voltage levels, I2C supports level translation, allowing seamless communication across devices with varying supply voltages. This feature enhances the flexibility of the I2C bus in mixed-voltage environments.

Overall, the I2C bus is an efficient and effective solution for communication in a wide range of electronic applications, from simple sensor networks to complex multi-device systems. Its ease of implementation and support for multiple devices make it a preferred choice for many designers in the field of electronics.The I2C bus uses a bi-directional Serial Clock Line [SCL] and Serial Data Lines [SDA]. Both the SCL and SDA lines are pulled high via an Rp resistor. Resistor Rs is optional, and used for ESD protection for `Hot-Swap` devices. No other lines are specified. Any device may be a Transmitter or Receiver, and a Master or Slave. Data and clock are sent from the Master ~ valid while the clock line is high. The link may have multiple Masters and Slaves on the bus, but only one Master may be active at any one time. I2C Slaves may receive or transmit data to the master. I2C, due to its two-wire nature (one clock, one data) can only communicate half-duplex. The maximum bus capacitance is 400pF, which sets the maximum number of devices on the I2C bus and the maximum line length.

The interface uses 8 bit long bytes, MSB [Most Significant Bit] first, with each device having a unique address. Data on the SDA data line only changes when the clock line [SCL] is low. However if SDA drops while SCL is high a start of frame is indicated. Also if SDA rises while SCL is high than a stop condition is indicated. The Start condition indicates a start of frame and the Stop condition indicates an end of frame. Each transfer on the I2C is 9 bits long, eight data bits followed by a `1` bit. The listener acknowledges the receipt of the byte in one of two ways; the listener may over write the `1` bit with a `0` bit indicating ready for more data.

or leaving the trailing `1` indicating not ready for data. The Master [talker] always generates the clock and the message. An I2C message begins with a Start bit, followed by a 7 bit Slave address and then a direction bit [`1` for Read, `0` for Write]. Once the slave address is sent, the slave is required to respond, otherwise the master will send a Stop or Retry bit.

If the Master sends a Write bit, the master will follow that with a sub-address to indicate a particular register. The slave will stop acknowledging the last byte of the transfer. Remember that the I2C bus is defined as having a maximum capacitance of 400pF, that defines the maximum number of I2C components on the I2C bus and the I2C length [in combination].

So the I2C Bus length is never defined in the I2C Bus specification. However, there is one note in the interface specification: If the length of the bus lines on a PCB or ribbon cable exceeds 10 cm and includes the VDD and VSS lines, the wiring pattern must be: SDA - [Power/Ground or Ground] - SCL, or no Vdd/Vss lines if there embedded within the PCB. Of course this could also be a twisted pair or shielded cable but I2C cable length still depends on the type of cable [and its capacitance] and the number of I2C devices.

The voltage VDD may be different for each device, but all devices have to relate their output levels to the voltage produced by the pull-up resistors [RP] It is possible to run off two different bus voltages, but they have to be translated [refer to the spec. ]. The I2C serial interface above show the I2C Pull-Up connecting to Vdd [supply voltage]. The I2C bus may also be seen as the Inter-IC Bus or the IIC Bus which all mean the same thing. The most common term is of course I2C. Of course there are always other references; I2C Serial Port, I2C Digital Interface, I2C Interface or I2C Interface Specification.

🔗 External reference

The I2C bus architecture is a popular choice for inter-device communication in embedded systems due to its simplicity and versatility. The two-wire configuration allows for efficient use of PCB space and minimizes wiring complexity. The pull-up resistors (Rp) are critical in ensuring that the SCL and SDA lines are maintained at a high logic level when not actively driven low by any device. The optional ESD protection resistor (Rs) enhances the robustness of the system, particularly in environments where devices may be hot-swapped.

In terms of data transmission, the half-duplex nature of I2C means that devices cannot send and receive data simultaneously, which is a trade-off for the simplicity of the two-wire interface. The acknowledgment mechanism is a vital part of the protocol, ensuring that data integrity is maintained. The Master device controls the timing of the communication and initiates data transfers, which is essential for coordinating the interactions between multiple devices on the bus.

The unique addressing scheme allows for a theoretically large number of devices on the bus, although practical limitations such as bus capacitance and physical layout must be considered. The maximum bus capacitance of 400pF effectively limits the number of devices that can be connected, and careful attention must be paid to the layout of the PCB or cable to maintain signal integrity.

In applications where devices operate at different voltage levels, I2C supports level translation, allowing seamless communication across devices with varying supply voltages. This feature enhances the flexibility of the I2C bus in mixed-voltage environments.

Overall, the I2C bus is an efficient and effective solution for communication in a wide range of electronic applications, from simple sensor networks to complex multi-device systems. Its ease of implementation and support for multiple devices make it a preferred choice for many designers in the field of electronics.The I2C bus uses a bi-directional Serial Clock Line [SCL] and Serial Data Lines [SDA]. Both the SCL and SDA lines are pulled high via an Rp resistor. Resistor Rs is optional, and used for ESD protection for `Hot-Swap` devices. No other lines are specified. Any device may be a Transmitter or Receiver, and a Master or Slave. Data and clock are sent from the Master ~ valid while the clock line is high. The link may have multiple Masters and Slaves on the bus, but only one Master may be active at any one time. I2C Slaves may receive or transmit data to the master. I2C, due to its two-wire nature (one clock, one data) can only communicate half-duplex. The maximum bus capacitance is 400pF, which sets the maximum number of devices on the I2C bus and the maximum line length.

The interface uses 8 bit long bytes, MSB [Most Significant Bit] first, with each device having a unique address. Data on the SDA data line only changes when the clock line [SCL] is low. However if SDA drops while SCL is high a start of frame is indicated. Also if SDA rises while SCL is high than a stop condition is indicated. The Start condition indicates a start of frame and the Stop condition indicates an end of frame. Each transfer on the I2C is 9 bits long, eight data bits followed by a `1` bit. The listener acknowledges the receipt of the byte in one of two ways; the listener may over write the `1` bit with a `0` bit indicating ready for more data.

or leaving the trailing `1` indicating not ready for data. The Master [talker] always generates the clock and the message. An I2C message begins with a Start bit, followed by a 7 bit Slave address and then a direction bit [`1` for Read, `0` for Write]. Once the slave address is sent, the slave is required to respond, otherwise the master will send a Stop or Retry bit.

If the Master sends a Write bit, the master will follow that with a sub-address to indicate a particular register. The slave will stop acknowledging the last byte of the transfer. Remember that the I2C bus is defined as having a maximum capacitance of 400pF, that defines the maximum number of I2C components on the I2C bus and the I2C length [in combination].

So the I2C Bus length is never defined in the I2C Bus specification. However, there is one note in the interface specification: If the length of the bus lines on a PCB or ribbon cable exceeds 10 cm and includes the VDD and VSS lines, the wiring pattern must be: SDA - [Power/Ground or Ground] - SCL, or no Vdd/Vss lines if there embedded within the PCB. Of course this could also be a twisted pair or shielded cable but I2C cable length still depends on the type of cable [and its capacitance] and the number of I2C devices.

The voltage VDD may be different for each device, but all devices have to relate their output levels to the voltage produced by the pull-up resistors [RP] It is possible to run off two different bus voltages, but they have to be translated [refer to the spec. ]. The I2C serial interface above show the I2C Pull-Up connecting to Vdd [supply voltage]. The I2C bus may also be seen as the Inter-IC Bus or the IIC Bus which all mean the same thing. The most common term is of course I2C. Of course there are always other references; I2C Serial Port, I2C Digital Interface, I2C Interface or I2C Interface Specification.

🔗 External reference