Integrator-ramp-generator-with-initial-condition-reset

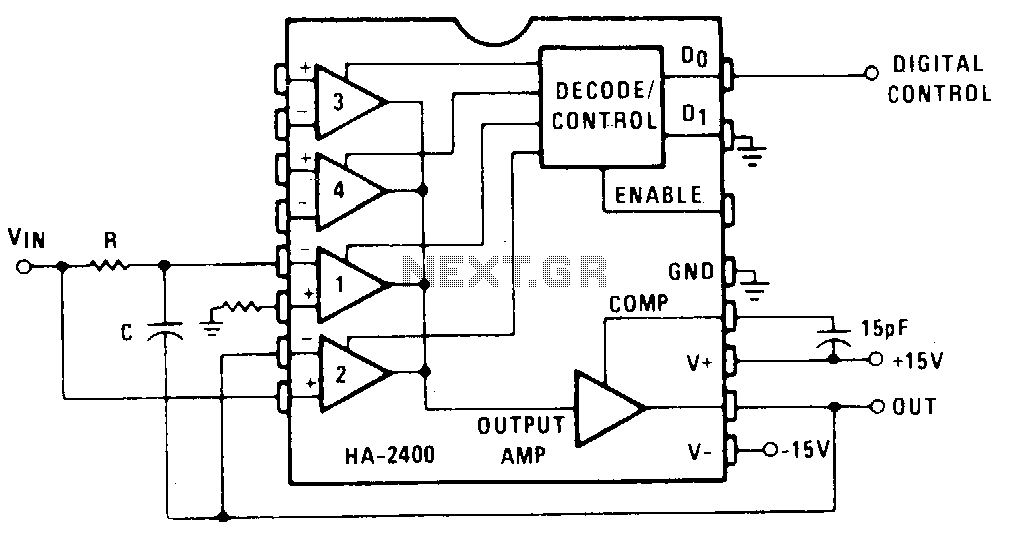

Channel 1 is configured as a conventional integrator, while Channel 2 is set up as a voltage follower. When Channel 2 is activated, the output will track the voltage of VJN, and capacitor C will discharge to maintain 0 V across it. When Channel 1 is subsequently activated, the output will initially reflect the instantaneous value of VJN and will then begin integrating towards the opposite polarity. This circuit is particularly suitable for generating timing ramps using a fixed DC input. Numerous variations, such as the development of programmable time constant integrators, are feasible.

The circuit described consists of two primary channels: Channel 1, functioning as an integrator, and Channel 2, serving as a voltage follower. The integrator is designed to convert a voltage input into a proportional output that represents the integral of that input over time. This is achieved through the use of an operational amplifier (op-amp) configured in the integrator topology, where the feedback element is a capacitor. The output voltage of the integrator will change over time based on the input voltage, allowing for the generation of ramp signals.

Channel 2, configured as a voltage follower, is crucial for maintaining the voltage level of VJN without loading the source. This configuration provides high input impedance and low output impedance, ensuring that the voltage across the capacitor remains stable when Channel 2 is activated. When Channel 2 is switched on, it effectively discharges capacitor C to maintain 0 V across it, allowing for accurate tracking of the input voltage.

The operation of the circuit begins with Channel 2 being activated, which allows the output to follow the input voltage VJN. Once Channel 1 is activated, the initial output reflects the instantaneous value of VJN. Following this, the integrator begins to accumulate charge, leading to a gradual change in output voltage that trends towards the opposite polarity, depending on the characteristics of the input signal.

This circuit's design is particularly advantageous for applications requiring timing ramp generation, as it can produce predictable voltage changes over time. The use of a fixed DC input allows for consistent performance, making it suitable for various timing applications. Furthermore, the potential for creating programmable time constant integrators opens avenues for more complex signal processing tasks, enabling customization of the integration time based on specific requirements. This flexibility enhances the circuit's utility in diverse electronic applications.Channell is wired as a conventional integrator, and channel2 as a voltage follower. When channel2 is switched on, the output will follow VJN and C will discharge to maintain 0 V across it. When channel! is then switched on, the output will initially be at the instantaneous value of VJN, and then will commence integrating towards the opposite polarity.

This circuit is particularly suitable for timing ramp generation using a fixed de input. Many variations, such as building programmable time constant integrators, are possible. 🔗 External reference

The circuit described consists of two primary channels: Channel 1, functioning as an integrator, and Channel 2, serving as a voltage follower. The integrator is designed to convert a voltage input into a proportional output that represents the integral of that input over time. This is achieved through the use of an operational amplifier (op-amp) configured in the integrator topology, where the feedback element is a capacitor. The output voltage of the integrator will change over time based on the input voltage, allowing for the generation of ramp signals.

Channel 2, configured as a voltage follower, is crucial for maintaining the voltage level of VJN without loading the source. This configuration provides high input impedance and low output impedance, ensuring that the voltage across the capacitor remains stable when Channel 2 is activated. When Channel 2 is switched on, it effectively discharges capacitor C to maintain 0 V across it, allowing for accurate tracking of the input voltage.

The operation of the circuit begins with Channel 2 being activated, which allows the output to follow the input voltage VJN. Once Channel 1 is activated, the initial output reflects the instantaneous value of VJN. Following this, the integrator begins to accumulate charge, leading to a gradual change in output voltage that trends towards the opposite polarity, depending on the characteristics of the input signal.

This circuit's design is particularly advantageous for applications requiring timing ramp generation, as it can produce predictable voltage changes over time. The use of a fixed DC input allows for consistent performance, making it suitable for various timing applications. Furthermore, the potential for creating programmable time constant integrators opens avenues for more complex signal processing tasks, enabling customization of the integration time based on specific requirements. This flexibility enhances the circuit's utility in diverse electronic applications.Channell is wired as a conventional integrator, and channel2 as a voltage follower. When channel2 is switched on, the output will follow VJN and C will discharge to maintain 0 V across it. When channel! is then switched on, the output will initially be at the instantaneous value of VJN, and then will commence integrating towards the opposite polarity.

This circuit is particularly suitable for timing ramp generation using a fixed de input. Many variations, such as building programmable time constant integrators, are possible. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713