LED Matrix Displays

1. Basic Structure and Working Principle

1.1 Basic Structure and Working Principle

Physical Architecture

An LED matrix display consists of a two-dimensional grid of light-emitting diodes (LEDs) arranged in either a common-anode or common-cathode configuration. In an m×n matrix, m rows and n columns form an addressable grid where each LED sits at the intersection of a row and column line. The matrix structure reduces the required I/O pins from m×n to just m+n, enabling scalable display sizes while minimizing driver complexity.

Electrical Characteristics

The forward voltage (Vf) and current (If) requirements determine the driving circuitry. For a typical red LED with Vf ≈ 1.8–2.2V and If = 10–20mA, the series resistor value follows from Kirchhoff's voltage law:

In multiplexed operation, the duty cycle (D) affects perceived brightness. For an N-row matrix, peak current must satisfy:

Scanning Methods

Two primary scanning techniques exist:

- Row-at-a-time (Raster scan): Activates one row while applying column data, cycling through rows at >60Hz to avoid flicker.

- Charlieplexing: Uses tri-state logic to address n(n-1) LEDs with n pins, trading resolution for pin efficiency.

The refresh rate (frefresh) must exceed the critical flicker frequency:

Optical Considerations

Pixel pitch (p) and viewing distance (d) determine angular resolution. The minimum resolvable angle follows from the Rayleigh criterion:

where Daperture is the effective LED emission area diameter. For daylight visibility, luminance (L) must compensate for ambient light:

Driver Circuitry

Modern implementations use constant-current drivers with shift registers (e.g., 74HC595) or dedicated ICs (MAX7219, IS31FL3731). The load impedance (Zload) must match transmission line characteristics to prevent signal degradation:

where L' and C' are distributed inductance and capacitance per unit length.

1.1 Basic Structure and Working Principle

Physical Architecture

An LED matrix display consists of a two-dimensional grid of light-emitting diodes (LEDs) arranged in either a common-anode or common-cathode configuration. In an m×n matrix, m rows and n columns form an addressable grid where each LED sits at the intersection of a row and column line. The matrix structure reduces the required I/O pins from m×n to just m+n, enabling scalable display sizes while minimizing driver complexity.

Electrical Characteristics

The forward voltage (Vf) and current (If) requirements determine the driving circuitry. For a typical red LED with Vf ≈ 1.8–2.2V and If = 10–20mA, the series resistor value follows from Kirchhoff's voltage law:

In multiplexed operation, the duty cycle (D) affects perceived brightness. For an N-row matrix, peak current must satisfy:

Scanning Methods

Two primary scanning techniques exist:

- Row-at-a-time (Raster scan): Activates one row while applying column data, cycling through rows at >60Hz to avoid flicker.

- Charlieplexing: Uses tri-state logic to address n(n-1) LEDs with n pins, trading resolution for pin efficiency.

The refresh rate (frefresh) must exceed the critical flicker frequency:

Optical Considerations

Pixel pitch (p) and viewing distance (d) determine angular resolution. The minimum resolvable angle follows from the Rayleigh criterion:

where Daperture is the effective LED emission area diameter. For daylight visibility, luminance (L) must compensate for ambient light:

Driver Circuitry

Modern implementations use constant-current drivers with shift registers (e.g., 74HC595) or dedicated ICs (MAX7219, IS31FL3731). The load impedance (Zload) must match transmission line characteristics to prevent signal degradation:

where L' and C' are distributed inductance and capacitance per unit length.

1.2 Types of LED Matrices (Monochrome vs. RGB)

Monochrome LED Matrices

Monochrome LED matrices consist of a single-color LED array, typically emitting red, green, blue, or white light. The simplest configuration involves a grid of LEDs with a common anode or cathode structure, driven via multiplexing to reduce pin count. The luminous intensity I of a single LED in such a matrix is governed by the forward current IF:

where η is the external quantum efficiency. For an N×M matrix, the peak current per LED must be adjusted to account for duty cycle D in multiplexed operation:

Common applications include low-cost informational displays, industrial control panels, and basic signage where color variation is unnecessary.

RGB LED Matrices

RGB matrices integrate red, green, and blue LEDs within each pixel, enabling full-color reproduction via additive color mixing. Each subpixel requires independent current control to achieve precise chromaticity coordinates (x,y) in the CIE 1931 color space. The dominant wavelength λd of each LED type follows:

where h is Planck's constant, c is light speed, and Eg is the semiconductor bandgap energy. Practical implementations use pulse-width modulation (PWM) for intensity control, with color depth determined by the PWM resolution:

for n-bit control per channel. Advanced designs incorporate gamma correction to match human visual perception:

Structural and Drive Circuit Differences

Monochrome matrices typically use a single driver IC per row/column, while RGB implementations require three parallel driver channels per pixel. The increased complexity affects refresh rate fr:

where trow is the row scan time. RGB matrices often employ specialized driver ICs with built-in grayscale control, such as the IS31FL3731 or TLC5947, to manage the higher data rate requirements.

Optical Performance Metrics

Key differences manifest in luminance uniformity and color consistency. For monochrome displays, the primary concern is spatial variation in luminous intensity, quantified by:

RGB matrices require additional characterization of color uniformity through the standard deviation of chromaticity coordinates across the display surface. Thermal management is more critical in RGB designs due to higher power density from multiple active junctions per pixel.

Application-Specific Tradeoffs

Monochrome matrices dominate in applications prioritizing power efficiency and simplicity, such as:

- Transportation information displays

- Medical equipment status indicators

- Industrial process monitoring

RGB implementations are essential for:

- Digital signage and advertising

- Entertainment lighting systems

- High-end instrumentation displays

Common Pixel Configurations (5x7, 8x8, etc.)

LED matrix displays are characterized by their pixel arrangements, which directly influence resolution, character legibility, and display functionality. The most prevalent configurations include 5×7, 8×8, and 16×16, each optimized for specific applications.

5×7 Matrix Configuration

The 5×7 matrix is the de facto standard for alphanumeric displays, offering a balance between resolution and simplicity. Each character is formed by selectively illuminating 35 discrete LEDs (5 columns × 7 rows). The minimal column count restricts horizontal detail, but the 7-row height ensures sufficient vertical resolution for Latin alphabets and numerals. The pixel fill factor F for a 5×7 matrix is given by:

In practice, multiplexing reduces the effective fill factor due to duty cycle limitations. A 1:8 multiplexed 5×7 display with 12 LEDs driven simultaneously has an effective fill factor of:

8×8 Matrix Configuration

8×8 matrices are ubiquitous in graphical applications, providing 64 pixels per module. Their square geometry enables seamless tiling for larger displays. The addressing complexity increases quadratically—an 8×8 passive matrix requires 16 I/O lines (8 rows + 8 columns), while active matrices integrate driver ICs like the MAX7219 to reduce external pin count. The pixel pitch p and viewing distance D follow the relation:

where θ is the human eye's angular resolution (≈1 arcminute). For a 3 mm pitch, the minimum comfortable viewing distance is 5.16 meters.

High-Density Configurations (16×16 and Beyond)

High-resolution matrices (16×16, 32×32, etc.) employ multiplexed active addressing to manage I/O constraints. A 32×32 RGB matrix with 1:16 multiplexing requires:

Modern implementations use shift register cascading (e.g., TPIC6B595) to reduce this to 3-4 signal lines. The refresh rate fr must satisfy:

where fflicker is the critical flicker frequency (typically 60 Hz). For a 32-row matrix, this demands a base refresh rate >3.84 kHz.

Comparative Analysis

The table below summarizes key parameters for common configurations:

| Configuration | Pixels | Typical Use | Addressing Complexity |

|---|---|---|---|

| 5×7 | 35 | Alphanumeric displays | Low (1:7 multiplex) |

| 8×8 | 64 | Basic graphics | Medium (1:8 multiplex) |

| 16×16 | 256 | High-res signage | High (active matrix) |

Advanced configurations like hexagonal or circular pixel arrangements exist for specialized applications but introduce non-trivial coordinate mapping challenges. The transformation from Cartesian (x,y) to hexagonal (u,v,w) coordinates follows:

2. Multiplexing Techniques (Row-Column Scanning)

Multiplexing Techniques (Row-Column Scanning)

Fundamentals of Row-Column Scanning

Row-column scanning is a time-division multiplexing technique used to drive LED matrices with reduced pin count. Instead of individually addressing each LED, the matrix is divided into rows and columns, where only one row is activated at a time while the corresponding column data is applied. This method leverages the persistence of vision effect, where rapid sequential activation of rows creates the illusion of a stable image.

The duty cycle for each LED is given by:

where N is the number of rows. For an 8×8 matrix, the duty cycle per LED is 12.5%, meaning each LED is only illuminated for 1/8th of the total refresh period.

Current Sinking and Sourcing

In a typical row-column scanning setup:

- Rows are driven by a current sink (e.g., a transistor or dedicated driver IC) that pulls the row to ground when active.

- Columns are driven by current sources (e.g., shift registers or GPIO pins) that apply the data signal.

The peak current per LED must be adjusted to compensate for the reduced duty cycle. If the desired average current is Iavg, the peak current Ipeak is:

Refresh Rate Considerations

The refresh rate frefresh must be sufficiently high to avoid flicker, typically above 60 Hz for most applications. The row scan time trow is:

For an 8×8 matrix at 100 Hz refresh rate, each row must be scanned in 1.25 ms. Microcontrollers often use timer interrupts or hardware PWM to manage this timing precisely.

Hardware Implementation

Common driver configurations include:

- Direct GPIO Driving: Suitable for small matrices where the microcontroller has sufficient pins. Rows are switched via NPN transistors, and columns are driven directly by GPIOs.

- Shift Register-Based: Columns are controlled by serial-in-parallel-out shift registers (e.g., 74HC595), reducing the required GPIO count.

- Dedicated LED Drivers: ICs like the MAX7219 or TLC5940 provide built-in multiplexing, current control, and brightness adjustment.

Visualization of Row-Column Scanning

The following diagram illustrates the scanning process for a 4×4 matrix:

Optimization Techniques

To improve performance and reduce flicker:

- Higher Refresh Rates: Increasing frefresh beyond 100 Hz minimizes perceptible flicker.

- Charlieplexing: A variant of multiplexing that leverages high-impedance states to drive N(N-1) LEDs with N pins.

- Gamma Correction: Adjusting brightness levels non-linearly to match human perception.

Practical Limitations

Key challenges include:

- Ghosting: Residual illumination due to slow turn-off times of LEDs or parasitic capacitances.

- Power Dissipation: Higher peak currents increase thermal stress on components.

- Brightness Uniformity: Variations in forward voltage drop across LEDs can cause uneven illumination.

Shift Register-Based Control

Shift registers are fundamental components in LED matrix control, enabling efficient data serialization and parallel output expansion. Their primary role is to reduce the number of microcontroller pins required to drive large LED arrays while maintaining high refresh rates and low computational overhead.

Serial-In, Parallel-Out (SIPO) Operation

The most common implementation uses 74HC595-series shift registers, which employ a serial-in, parallel-out (SIPO) architecture. Data is clocked in bitwise through a single serial input (SER), then latched to parallel outputs when the storage register clock (RCLK) triggers. The shift register clock (SRCLK) advances bits through internal flip-flops at each rising edge, following the timing relationship:

Critical timing constraints emerge when cascading multiple registers. The total propagation delay for an N-register chain scales as:

Cascading and Daisy-Chaining

For M×N LED matrices, shift registers are daisy-chained via the serial output (QH') pin. The output enable (OE) pin implements PWM dimming by toggling at frequencies above 200 Hz to avoid flicker. A complete 8×8 matrix with two-color LEDs typically requires three cascaded registers:

- One register for row selection (common cathode)

- Two registers for column data (red and green anodes)

The refresh rate (f_refresh) depends on the clock frequency (f_clk) and register count (N):

where R represents the number of rows being multiplexed.

Signal Integrity Considerations

High-speed shifting introduces transmission line effects when trace lengths exceed:

where t_r is the rise time (typically 6 ns for 74HC595), ε_r the substrate dielectric constant, and c the speed of light. Termination resistors (33–100 Ω) mitigate reflections when driving long cascades.

Power Distribution Analysis

Simultaneous switching of multiple outputs creates current spikes. The peak supply current I_peak per register is:

where C_load includes both LED capacitance (~20 pF per pixel) and PCB parasitic capacitance. Decoupling capacitors must satisfy:

with ΔV typically held below 5% of VCC.

2.3 Using Dedicated LED Driver ICs (e.g., MAX7219)

Dedicated LED driver ICs such as the MAX7219 simplify the control of LED matrices by handling multiplexing, current regulation, and data shifting internally. These ICs communicate via serial peripheral interface (SPI) or bit-banged protocols, reducing microcontroller overhead and enabling precise brightness control.

Key Features of the MAX7219

The MAX7219 integrates an 8x8 LED matrix driver with the following capabilities:

- 16-bit shift register for cascading multiple drivers.

- Digit-by-digit brightness control via a 4-bit code (0–15).

- Decode mode for 7-segment displays (BCD or no-decode).

- Low-power shutdown mode (150µA standby current).

SPI Communication Protocol

The MAX7219 uses a synchronous serial protocol with the following signals:

- DIN (Data In): Serial data input (MSB-first).

- CLK (Clock): Shifts data on rising edges.

- CS (Chip Select): Active-low latch signal.

Each 16-bit data packet consists of:

Current Regulation and Brightness

The MAX7219 regulates LED current using an external resistor (RSET). The peak current per segment is given by:

where VREF is typically 1.25V, and the DAC adjusts brightness digitally.

Cascading Multiple Drivers

For larger displays, multiple MAX7219 ICs can be daisy-chained. The DOUT pin passes data to the next IC after 16 clock cycles. The total refresh rate scales inversely with the number of drivers:

where N is the number of cascaded ICs.

Practical Implementation

A typical circuit includes:

- Decoupling capacitors (0.1µF and 10µF) near VCC.

- RSET = 10kΩ for ~20mA segment current.

- Series resistors (220Ω) on LED anodes for additional protection.

// Arduino SPI example for MAX7219

#include <SPI.h>

const int CS_PIN = 10;

void sendData(uint8_t address, uint8_t value) {

digitalWrite(CS_PIN, LOW);

SPI.transfer(address);

SPI.transfer(value);

digitalWrite(CS_PIN, HIGH);

}

void setup() {

SPI.begin();

pinMode(CS_PIN, OUTPUT);

sendData(0x09, 0xFF); // Enable BCD decode

sendData(0x0A, 0x0F); // Full brightness

sendData(0x0B, 0x07); // Scan all digits

sendData(0x0C, 0x01); // Normal operation

}

3. GPIO-Based Control

3.1 GPIO-Based Control

Direct GPIO Driving Principles

General-purpose input/output (GPIO) pins on microcontrollers or single-board computers (e.g., Raspberry Pi, ESP32) are the most straightforward way to control LED matrices. Each GPIO pin can source or sink current, typically limited to a few milliamperes (e.g., 16 mA per pin on Raspberry Pi). For an N×M LED matrix, N+M GPIO pins are required—N for rows (anodes) and M for columns (cathodes). The matrix is refreshed rapidly via multiplexing, where only one row is active at a time, and columns are toggled to control individual LEDs.

Here, trefresh is the time each row remains active, and fframe is the desired frame rate (e.g., 60 Hz). For an 8×8 matrix, this yields a row activation time of ~2.1 ms per frame.

Current Limiting and Switching

GPIO pins cannot directly drive high-current LED matrices. A typical LED requires 10–20 mA, exceeding the GPIO's current-sourcing capability. To mitigate this:

- Row drivers: Use PNP transistors (e.g., 2N3906) or dedicated ICs (e.g., ULN2003) to source current to the anodes.

- Column drivers: Employ NPN transistors (e.g., 2N2222) or MOSFETs (e.g., IRLB8721) to sink current from cathodes.

The base/gate current for these transistors is supplied by GPIO pins, while the collector/drain handles the LED current. A current-limiting resistor is placed in series with each LED:

where VCE(sat) is the transistor’s saturation voltage (~0.2 V for BJTs, near 0 V for MOSFETs).

Scanning Algorithms

Two primary methods exist for refreshing the display:

- Row-at-a-time scanning: Activates each row sequentially, with column data updated synchronously. This minimizes GPIO usage but requires precise timing to avoid flicker.

- Charlieplexing: Leverages GPIO tri-state (high/low/high-Z) to control N×(N−1) LEDs with N pins. Suitable for small matrices but complicates software.

Practical Considerations

Voltage drops: Long wires or high currents introduce parasitic resistance, causing uneven brightness. Kelvin connections or local decoupling capacitors mitigate this. Timing jitter from non-real-time operating systems (e.g., Linux on Raspberry Pi) can cause visible artifacts. Solutions include:

- Dedicated PWM hardware (e.g., Raspberry Pi’s PCM/PWM peripherals).

- Bit-banging with cycle-accurate delays (e.g., ESP32’s RMT peripheral).

Example Circuit

A basic 8×8 matrix driven by an ESP32:

Optimization Techniques

Persistent brightness: Adjust trefresh dynamically based on LED duty cycle to compensate for human eye nonlinearity (Weber-Fechner law). Gamma correction maps linear intensity values to perceptual brightness:

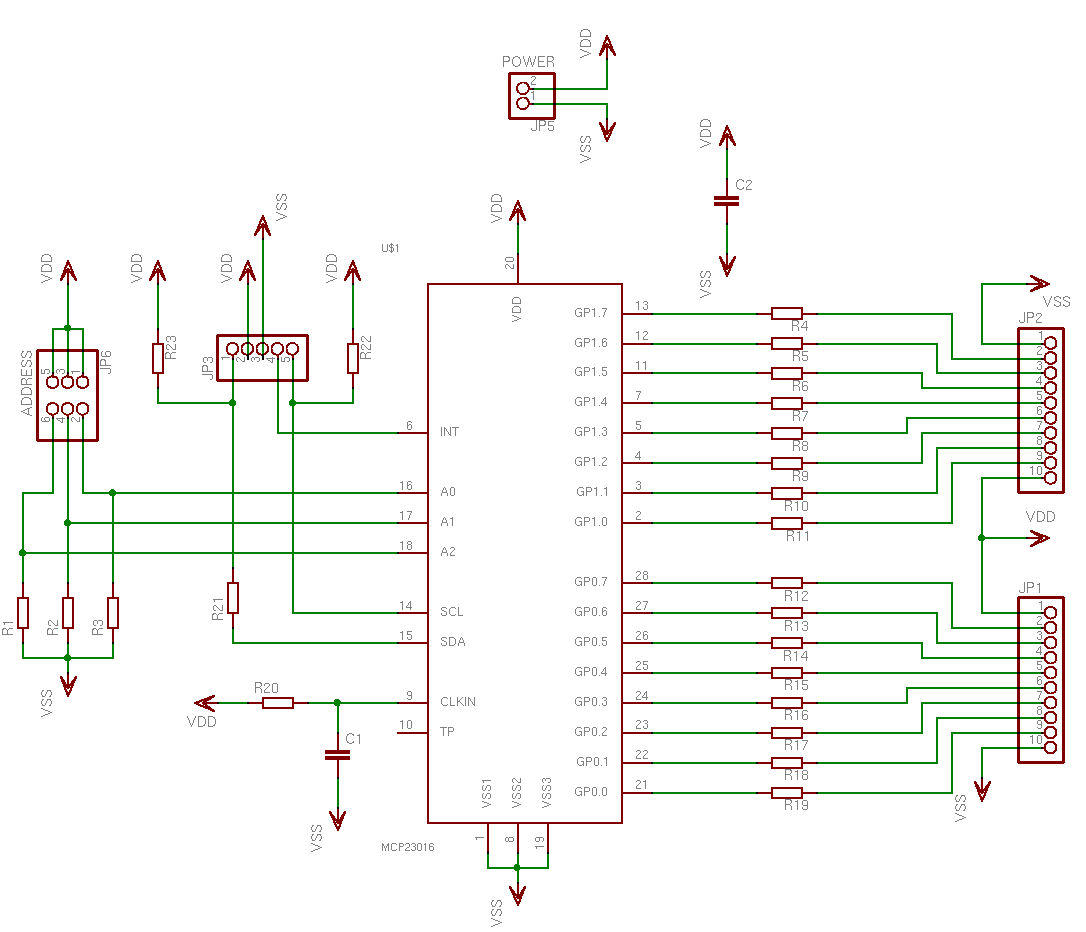

3.2 SPI and I2C Communication Protocols

LED matrix displays commonly employ serial communication protocols like SPI (Serial Peripheral Interface) and I2C (Inter-Integrated Circuit) to interface with microcontrollers or drivers. These protocols offer distinct advantages in terms of speed, complexity, and scalability, making them suitable for different display applications.

SPI Protocol for LED Matrices

SPI is a full-duplex, synchronous serial protocol characterized by high-speed data transfer, typically in the range of 10-100 Mbps. The protocol operates in a master-slave configuration, where the master device (usually a microcontroller) controls one or more slave devices (LED drivers or shift registers).

The SPI bus consists of four primary signals:

- SCLK (Serial Clock) - Generated by the master to synchronize data transfer

- MOSI (Master Out Slave In) - Data line from master to slave

- MISO (Master In Slave Out) - Data line from slave to master (often unused in LED matrices)

- SS/CS (Slave Select/Chip Select) - Active-low signal to enable specific slaves

For an N×M LED matrix, the refresh rate (frefresh) can be calculated based on the SPI clock frequency (fSCLK) and the number of bits (B) required per refresh cycle:

Where B depends on the color depth (e.g., 24 bits for RGB, 8 bits for monochrome). The absence of addressing in SPI necessitates separate chip select lines for multiple displays, making it less scalable than I2C for large arrays.

I2C Protocol for LED Matrices

I2C is a half-duplex, synchronous protocol that uses only two bidirectional lines: SCL (Serial Clock) and SDA (Serial Data). It operates at lower speeds (typically 100-400 kHz in standard mode, up to 3.4 MHz in high-speed mode) but offers built-in addressing, making it more suitable for multi-device systems.

Each I2C device has a 7-bit or 10-bit address, allowing up to 112 or 1008 devices on a single bus respectively. The protocol uses open-drain outputs with pull-up resistors, enabling bus arbitration through clock stretching and collision detection.

The maximum refresh rate for an I2C-driven matrix is constrained by the bus speed and acknowledgment cycles. The time (tframe) to transmit one data frame is:

Where ACK represents the acknowledgment bit duration, Nbytes is the number of data bytes, and tstart/tstop are the start/stop condition times.

Protocol Selection Criteria

The choice between SPI and I2C depends on several factors:

- Speed requirements: SPI is preferable for high refresh rates (>1 kHz) or large matrices

- Pin constraints: I2C uses fewer GPIO pins (2 vs. 3-4 for SPI)

- System complexity: I2C simplifies wiring for multiple displays

- Power consumption: I2C's lower speed generally consumes less power

Modern LED driver ICs like the IS31FL3731 (I2C) and MAX7219 (SPI) implement these protocols with additional features like PWM control and error checking. Some advanced displays combine both protocols, using I2C for configuration and SPI for high-speed data transfer.

3.3 Software Libraries for LED Matrix Control

Controlling LED matrices efficiently requires robust software libraries that handle multiplexing, refresh rates, and data transfer protocols. Advanced libraries optimize performance by leveraging hardware acceleration, DMA (Direct Memory Access), and specialized microcontroller peripherals.

Core Functionality in LED Matrix Libraries

Most high-performance LED matrix libraries implement:

- Hardware-accelerated bit-banging: Using GPIO registers directly for precise timing.

- DMA-driven data transfer: Minimizing CPU overhead during display refreshes.

- Gamma correction: Applying perceptual linearization via lookup tables (LUTs).

- Dithering algorithms: Temporal or spatial dithering for enhanced color depth.

The refresh rate frefresh for an N×M matrix is constrained by:

where trow is the row activation time and tblank is the blanking interval.

Popular Libraries for Embedded Systems

1. FastLED

Optimized for WS2812B and similar addressable LEDs, FastLED employs ARM Cortex-M4/M7 assembly-level optimizations. It supports:

- 12-bit color resolution via hybrid PWM-dithering

- Parallel output on multiple GPIO pins

- Real-time palette blending with fixed-point arithmetic

#include <FastLED.h>

#define NUM_LEDS 256

CRGB leds[NUM_LEDS];

void setup() {

FastLED.addLeds<WS2812B, GPIO_PIN, GRB>(leds, NUM_LEDS);

FastLED.setBrightness(64);

}

2. SmartMatrix

Designed for HUB75 panels, SmartMatrix uses:

- Double-buffered frame storage

- Bresenham's line algorithm for graphics

- CIE 1931 color space conversion

The library achieves 24-bit color depth through 8-8-8 bit RGB partitioning with error diffusion.

FPGA-Based Control Libraries

For ultra-high-density matrices, FPGA libraries like LEDscape implement:

where Cpanel is the panel's color depth and Pparallel is the parallel output width.

Real-Time Operating System (RTOS) Integration

Libraries like FreeRTOS-driven LEDControl utilize:

- Task priorities for refresh timing

- Semaphores for frame buffer synchronization

- Interrupt-driven DMA completion handlers

Typical latency budgets for a 60Hz display:

| Process | Time (µs) |

|---|---|

| Frame buffer swap | ≤50 |

| DMA setup | ≤20 |

| Row transition | ≤2 |

4. Scrolling Text Displays

4.1 Scrolling Text Displays

Scrolling text on an LED matrix involves dynamically shifting pixel data across the display to create the illusion of motion. This requires precise timing, memory management, and efficient rendering techniques to ensure smooth visual transitions.

Pixel Shift Algorithms

The core operation relies on shifting columns or rows of pixel data at regular intervals. For a horizontally scrolling display, each column vector ci in an M×N matrix is replaced by ci-1 at time step Δt:

where ⊕ denotes concatenation and cnew is the next column from a character buffer. The scroll rate v (pixels/second) determines the refresh interval:

Memory Management Techniques

Double buffering is essential to prevent flickering. Two memory blocks alternate roles:

- Display buffer: Actively drives the LED matrix

- Render buffer: Prepares the next frame during vertical blanking

The transition occurs during the display's blanking interval, typically lasting 1-2% of the frame period. For a 16×32 RGB matrix at 120Hz:

Character Glyph Rendering

Font data is stored as bit-packed arrays with 1-8 bits per pixel (bpp). A 5×7 ASCII font with 1bpp encoding requires:

Anti-aliasing improves readability at low resolutions. A 2bpp scheme enables four intensity levels per pixel, computed via spatial dithering:

Hardware Acceleration

Modern LED controllers like the IS31FL3731 integrate hardware scrolling through these key features:

- Dedicated shift registers for column rotation

- DMA support for zero-CPU-overhead updates

- Programmable blanking intervals

The scroll operation reduces to writing start/end columns to control registers:

// Configure horizontal scroll on IS31FL3731

void setScrollRange(uint8_t start, uint8_t end) {

writeRegister(SCROLL_START_REG, start);

writeRegister(SCROLL_END_REG, end);

writeRegister(SCROLL_MODE_REG, 0x01); // Enable continuous scroll

}

Optimal Refresh Strategies

Persistence of vision requires refresh rates above 60Hz. For a 512-pixel display scrolling at 30 pixels/second:

PWM dimming complicates timing. A 10-bit PWM at 1kHz yields an effective refresh rate of:

4.2 Simple Animations and Graphics

Frame Buffering and Refresh Rate Optimization

Animations on LED matrices rely on frame buffering, where pixel states are stored in a memory buffer before being rendered. For an m×n matrix, the buffer size is typically m × n × b bits, where b is the color depth. The refresh rate fr must exceed the flicker fusion threshold (typically 60 Hz) to avoid perceptible flicker. The required data rate D is:

For a 32×32 RGB matrix (24-bit color) at 100 Hz, this demands a bandwidth of 2.46 Mbps. Techniques like double buffering prevent tearing by swapping buffers during vertical blanking intervals.

Scanline Rendering and Persistence of Vision

LED matrices often use multiplexed scanning to reduce I/O pins. A k-row scan requires each row to be active for 1/k of the frame time. The human eye's persistence of vision (≈16 ms) integrates these discrete illuminations into a continuous image. The row-on time trow must satisfy:

For k=8 and fr=100 Hz, trow ≤ 1.25 ms. Insufficient time causes brightness non-uniformity.

Animation Techniques

Sprite-Based Animation

Sprites are pre-rendered bitmaps moved across the display. The sprite position (x(t), y(t)) updates each frame according to motion equations. For linear motion:

Collision detection with screen boundaries requires:

where w and h are sprite dimensions.

Procedural Animations

Dynamic patterns (e.g., sine waves, fractals) are computed in real-time. A traveling wave with amplitude A, wavelength λ, and speed v can be modeled as:

Optimizing these calculations often involves lookup tables (LUTs) or fixed-point arithmetic to reduce computational latency.

Color Mixing and Gamma Correction

PWM duty cycles control perceived brightness, but the human eye responds nonlinearly (Weber-Fechner law). Gamma correction compensates with:

For smooth color transitions, 8-bit PWM (256 levels) per channel is standard, though 10-12 bits are preferred for high-end displays to avoid banding artifacts.

Hardware Considerations

Modern LED drivers (e.g., IS31FL3731, MAX7219) integrate PWM controllers and scan logic. The MAX7219, for instance, supports 8×8 matrices with 16-step brightness control. For larger displays, shift registers (74HC595) or dedicated ICs (TLC5940) cascade to form high-resolution grids.

4.3 Interactive LED Matrix Projects

Real-Time Pixel Manipulation

Interactive LED matrices rely on high-speed multiplexing to enable real-time pixel control. The refresh rate frefresh must exceed the critical flicker fusion threshold (typically 60 Hz) to maintain persistence of vision. For an N×M matrix, the per-row dwell time trow is derived from:

Advanced implementations use bit-angle modulation (BAM) for 12-16 bit color depth while maintaining high refresh rates. The technique distributes PWM duty cycles across multiple refresh cycles, mathematically represented as:

where Dk is the kth bit of the color value and B is the bit depth.

Input-Output Latency Optimization

For touch or motion-based interactivity, the end-to-end latency must be minimized to under 20 ms to maintain perceptual immediacy. This requires:

- Hardware-accelerated row scanning with DMA controllers

- Parallel input sampling at ≥1 kHz rates

- Double-buffered frame memory to prevent tearing

The total system latency τ can be modeled as:

Case Study: Multi-Touch LED Table

A 64×64 RGB matrix with IR touch overlay demonstrates these principles. The system uses:

- STM32H743 MCU with Chrom-ART accelerator

- Custom BAM driver achieving 18-bit color at 120 Hz

- Capacitive sensing with 4 ms response time

Networked Synchronization

For large-scale installations, precise clock synchronization across matrices is achieved using IEEE 1588 (PTP). The timing error ε between nodes must satisfy:

Implementations typically use fiber-optic or wireless time distribution with Kalman filtering to compensate for propagation delays.

5. Common Issues (Ghosting, Flickering)

5.1 Common Issues (Ghosting, Flickering)

Ghosting in LED Matrices

Ghosting occurs when faint residual images appear on an LED matrix due to incomplete discharge of the capacitive elements in the driving circuitry. This phenomenon arises primarily from the parasitic capacitance (Cp) between adjacent LEDs and the finite discharge time constant (τ) of the matrix.

where Rout is the output impedance of the driver IC. For a multiplexed matrix with N rows, the discharge time must satisfy:

Here, Von and Voff represent the forward bias and cutoff voltages of the LEDs, respectively. If this condition is violated, charge accumulation leads to unintended illumination of off-state LEDs.

Mitigation Techniques

- Active discharge circuits: Adding pull-down transistors to rapidly dissipate residual charge.

- Optimized scan timing: Introducing a blanking interval between row transitions.

- Capacitance balancing: Strategic PCB layout to minimize parasitic coupling.

Flickering in LED Matrices

Flickering results from perceptible fluctuations in luminance when the refresh rate (frefresh) approaches the human eye's critical flicker fusion threshold (CFF), typically 60-90 Hz under normal lighting. For an N-row multiplexed display, the per-row dwell time (trow) must satisfy:

In practice, PWM dimming exacerbates flickering because the effective luminance modulation frequency becomes:

where k is the PWM resolution in bits. For example, an 8-bit PWM at 1 kHz yields feff = 3.9 Hz, which is clearly visible.

Advanced Solutions

- High-frequency drivers: Using dedicated ICs like TLC5940 with >1 MHz PWM capability.

- Delta-sigma modulation: Trading PWM resolution for higher effective refresh rates.

- Double-buffering: Eliminating brightness variations during row transitions.

Interplay Between Ghosting and Flickering

These phenomena exhibit an inverse relationship governed by:

where α is a display-specific constant (typically 0.1-0.3). This tradeoff necessitates careful optimization in high-performance applications like avionics displays, where both artifacts must be minimized simultaneously.

5.2 Brightness and Power Consumption Optimization

Luminance and Current Relationship

The luminous intensity (Iv) of an LED is directly proportional to the forward current (IF) under typical operating conditions. However, this relationship becomes nonlinear at higher currents due to thermal effects and efficiency droop. The empirical model is given by:

where η(IF) is the current-dependent efficiency term. For pulse-width modulation (PWM) driven LEDs, the average luminance (Lavg) is:

where D is the duty cycle (0 ≤ D ≤ 1) and Lpeak is the peak luminance at maximum current.

Power Dissipation and Thermal Management

The total power dissipation (Pdiss) in an LED matrix is the sum of individual LED losses and driver inefficiencies:

where N is the number of active LEDs, VF is the forward voltage, Idrv is the driver current, and Rdrv is the driver resistance. Excessive power dissipation leads to junction temperature rise, which reduces LED lifespan and efficiency. The thermal resistance (θJA) must be minimized through proper heatsinking:

Dynamic Current Scaling

To optimize power consumption without sacrificing perceived brightness, adaptive current scaling can be employed. This technique adjusts IF based on ambient light conditions and content type. The human eye's nonlinear response (Weber-Fechner law) allows for reduced current at lower brightness levels:

Thus, a logarithmic current reduction can be applied while maintaining visual fidelity.

Efficient Driving Techniques

Multiplexed LED matrices often suffer from high peak currents. Active current regulation using switching converters or constant-current sinks improves efficiency. The power savings (ΔP) from using an ideal buck converter instead of a linear driver is:

where ηbuck is the converter efficiency (typically 85–95%).

Optimal Refresh Rate and Persistence

The refresh rate must exceed the flicker fusion threshold (~60–90 Hz for most viewers) but higher rates increase power consumption. Persistence optimization balances motion clarity with energy use:

where Ctotal is the cumulative capacitance of the matrix. Subframe addressing techniques like binary-coded modulation can reduce effective refresh power by 30–50%.

Case Study: Large-Scale Video Wall

A 4K LED video wall (3840×2160, 10 mm pitch) with 50% average brightness consumes approximately 8 kW with conventional driving. Implementing:

- Dynamic current scaling (20% reduction)

- Active regulation (12% savings)

- Optimal refresh at 75 Hz (vs. 120 Hz, 18% savings)

yields a total power reduction to 4.7 kW (41% savings) while maintaining perceptual quality.

5.3 Heat Management and Longevity

Thermal Dynamics in LED Matrices

LED matrix displays generate heat primarily through Joule heating in the forward-biased p-n junctions. The power dissipation Pdiss of an individual LED can be modeled as:

where IF is forward current, VF is forward voltage, and ηe is the electro-optical conversion efficiency (typically 20-40% for visible LEDs). For a matrix of m×n LEDs driven at duty cycle D, the total thermal load becomes:

where Pdriver accounts for losses in multiplexing circuitry. This heat must be conducted away from the junction to prevent accelerated degradation.

Temperature-Dependent Degradation Mechanisms

Arrhenius kinetics govern three primary failure modes:

- Lumen depreciation: Phosphor thermal quenching and epoxy yellowing follow

$$ L(t) = L_0 e^{-\alpha t e^{-E_a/kT}} $$where Ea is activation energy (~0.7eV for InGaN LEDs).

- Contact migration: Electromigration at bond pads accelerates with current density J and temperature T via Black's equation:

$$ MTF \propto J^{-n}e^{E_a/kT} $$(Typical n = 2 for aluminum interconnects)

- Epoxy carbonization: Thermal decomposition of encapsulants above 150°C increases optical absorption.

Thermal Resistance Analysis

The junction-to-ambient thermal resistance θJA for an LED in a matrix is the sum of:

where θJC (junction-to-case) is fixed by the LED package, while θCS (case-to-sink) and θSA (sink-to-ambient) depend on system design. For a 8×8 matrix on FR4 PCB:

Active Cooling Strategies

For high-brightness applications (>5000 nits), forced-air cooling becomes necessary. The required airflow can be estimated using:

where ρ is air density (1.2 kg/m³), cp is specific heat (1005 J/kg·K), and ΔT is the allowable temperature rise. A 100W LED wall typically requires 15-20 CFM with properly designed finned heatsinks.

Materials Selection

Advanced thermal interface materials (TIMs) significantly impact performance:

| Material | Thermal Conductivity (W/m·K) | Application |

|---|---|---|

| Silicone grease | 0.8-3.5 | Low-cost consumer displays |

| Graphite pads | 5-20 | High-density arrays |

| Liquid metal | 30-80 | Military/aerospace |

Predictive Maintenance

Implementing temperature derating based on Arrhenius models can extend operational life. A common industry practice reduces drive current by 2% per °C above 85°C junction temperature, following the rule:

Infrared thermography of operating matrices reveals hotspots indicating uneven current distribution or failing components.

6. Recommended Datasheets and Manuals

6.1 Recommended Datasheets and Manuals

- LP5866 6 × 18 LED Matrix Driver with 8-Bit Analog and 8-/16-Bit PWM ... — The LP586x devices are a family of high performance LED matrix drivers. The device integrates 18 constant current sinks with N (N = 1/2/4/6/8/11) switching MOSFETs to support N × 18 LED dots or N × 6 RGB LEDs. The LP5866 integrates 6 MOSFETs for up to 108 LED dots or 36 RGB LEDs. The LP5866 supports both analog dimming and PWM dimming methods.

- Guide to LED Matrix Display: Pixel Pitch, Scan Mode, and Arduino ... — Learn about LED matrix displays, including what P10 and P6 mean, key terms like scan rate, and how to integrate them with Arduino UNO and Mega for stunning projects. Explore the world of LED matrix displays with our comprehensive guide. Understand pixel pitch, scan modes, and how Arduino UNO and Mega handle both RGB a

- LED Matrix Display Series LX P6 RGB - VISUAL ELECTRONIC GmbH - PDF ... — 1. LED Matrix Modules The LED matrix display family LX P6 RGB is ideal for the visualization of situation-related data in the industry. The used LED matrix modules are characterized by extremely bright SMD LEDs which provide a clear readability even in difficult light conditions, such as direct sunlight.

- PDF MAX7219/MAX7221 - Serially Interfaced, 8-Digit LED Display Drivers - Analog — General Description The MAX7219/MAX7221 are compact, serial input/ output common-cathode display drivers that interface microprocessors (μPs) to 7-segment numeric LED displays of up to 8 digits, bar-graph displays, or 64 individual LEDs. Included on-chip are a BCD code-B decoder, multiplex scan circuitry, segment and digit drivers, and an 8x8 static RAM that stores each digit. Only one ...

- MAX7219 Datasheet and Product Info | Analog Devices — The MAX7219/MAX7221 are compact, serial input/output common-cathode display drivers that interface microprocessors (µPs) to 7-segment numeric LED displays of up to 8 digits, bar-graph displays, or 64 individual LEDs. Included on-chip are a BCD code-B decoder, multiplex scan circuitry, segment and digit drivers, and an 8x8 static RAM that stores each digit. Only one external resistor is ...

- PDF LED Matrix Display Series LX P6 RGB - EHS — LED Matrix Display Series LX P6 RGB for industrial use LEDs with excellent luminosity Numbers, characters, symbols, pictures 256 different colors

- Electronic Displays, Inc. — This manual is provided as a guide for using ED2xx and ED4xx Numeric Series LED Signs with RS Logix 5000 software by Allen Bradley. This manual provides detailed configuration instructions to configure Ethernet/IP and importing AOIs (add-on-instructions) to RS Logix 5000 software projects.

- PDF Aquatics Interface with Daktronics Matrix Displays — Daktronics Matrix Displays with Colorado Timing Systems This section assumes that the scoreboard output in the Colorado Timing System (CTS) timer is set to its default settings and that the CTS timer and Hy-Tek's MEET MANAGER are already communicating.

- PDF LED Matrix Displays LX RGB Indoor/Outdoor - EHS — Zwei bis vier Befestigungsnuten am Gehäuse der LED Anzeige erleichtern Ihnen die Montage. Neben dem Standard Befestigungssatz BS L, welcher Teil des Lieferumfanges ist, stehen weitere Montagehilfen wie Wandmontagebügel, Aufhängeösen, Schwenkrahmen und Einbaumontagehilfen zur Verfügung.

- PDF LP5891 48 Current Sources, 64 Scans, Common Cathode LED Matrix Driver — An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers.

6.2 Advanced Topics and Research Papers

- Mini-LED and Micro-LED: Promising Candidates for the Next ... - MDPI — Displays based on inorganic light-emitting diodes (LED) are considered as the most promising one among the display technologies for the next-generation. The chip for LED display bears similar features to those currently in use for general lighting, but it size is shrunk to below 200 microns. Thus, the advantages of high efficiency and long life span of conventional LED chips are inherited by ...

- Light-emitting diode - Wikipedia — The first LED was created by Soviet inventor Oleg Losev [9] in 1927, but electroluminescence was already known for 20 years, and relied on a diode made of silicon carbide.. Commercially viable LEDs only became available after Texas Instruments engineers patented efficient near-infrared emission from a diode based on GaAs in 1962.. From 1968, commercial LEDs were extremely costly and saw no ...

- Automotive Displays: The Race is on Between LCD and OLED! — Another highlight of the symposium was the world's first series integration of an autostereoscopic 3D instrument cluster display (Fig.3) in the new S-Class presented by Achim Pross and colleagues from Mercedes-Benz.Its technical features and challenges are remarkable: A 12.3-inch LCD delivering 1,200 cd/m² with an asymmetric optimized red, green, blue, and white (RGBW) subpixel layout for ...

- Full article: Understanding multi-domain compact modeling of light ... — 1.2. Thermal management key for solid-state lighting performance. The optical, electrical and thermal characteristics of an LED luminaire exhibit a strong interdependency among each other as seen in Figure 2.Only a part of electrical energy consumed by an LED is converted to light ϕ v, while the rest is emitted as heat P h e a t.Inadequate dissipation of this waste heat will overheat the LED ...

- (PDF) Digital Clock Project - ResearchGate — Use of independent LED matrix digital wall for the display that takes a huge space in the circuit and a lot of matr ix code in the controller. Displays only hour and minute.

- Organic Light Emitting Diodes (OLED) - ResearchGate — Other types of technology applications, such as those involving organic light emitting diodes (OLEDs) and organic field-effect transistors (OFETs) as one of the most populous electroluminescent ...

- Radar Absorbing Material - an overview | ScienceDirect Topics — In this review, we classify and organize research papers on the absorbing properties of materials based on MXene in recent years. Based on the types of materials that enhance absorbing performance, the reported composite materials in the articles are classified as pure MXene absorbing materials, MXene/magnetic loss composite materials, MXene/dielectric loss composite materials, MXene ...

- (PDF) Smart Home System: A Comprehensive Review - ResearchGate — In addition to presenting a complete picture of the current smart home system's (SHS) development and characteristics, this paper provides a deep insight into latest hardware and trends.

- Thin-film image sensors with a pinned photodiode structure — Thin-film-based image sensors can offer high absorption over a broad wavelength spectrum and can potentially be monolithically co-integrated with readout circuits made using complementary metal ...

- Altruistic World Online Library • View topic - FREDA BEDI CONT'D (#4) — This is a broad, catch-all category of works that fit best here and not elsewhere. If you haven't found it someplace else, you might want to look here.

6.3 Online Resources and Communities

- GitHub - DIYables/DIYables-LED-Matrix: This LED Matrix library is ... — This LED Matrix library is designed for Arduino, ESP32, ESP8266... to work with the Max7219 LED Matrix - DIYables/DIYables-LED-Matrix ... unlike other libraries that fix characters to 8-pixel width, for a more compact and flexible display; Compatible with any Arduino-API-supported platform, including Arduino, ESP32, ESP8266, and more ...

- The electronic document display: A 6.3-million-pixel AMLCD — Abstract— This paper describes 6.3-million-pixel active-matrix displays in monochrome and color (1.6 million color groups) with a diagonal dimension of 33 cm (13 in.), first discussed by Martin et al. in 1993. These displays have the largest number of pixels of any AMLCDs thus far reported. The monochrome display is intended for office-automation applications where there is a requirement for ...

- LED Displays with Arduino - DroneBot Workshop — In this experiment, I am using a common module that actually contains four 8×8 LED dot matrix displays. Each display has its own MAX7219, and they are daisy-chained. The module has an output, so you can connect a second one. Dot Matrix Displays. Dot Matrix displays have a number of advantages over standard 7-segment displays.

- Raspberry Pi Pico Controlled 64x32 LED Matrix (CircuitPython) — By setting matrix.brightness equal to the dsum of my dummy list I can make it so the display turns off when the list is [0, 0, 0, 0, 0]. displaybmp: This function is just the generic way of displaying a bmp and was pulled from documentation, however the documentation assumes standard matrix and image dimensions, which I wasn't using, so I added ...

- TPS92661EVM-001 LED Matrix Manager Evaluation Module (EVM) User's Guide — timers when the LED string voltage is below 5 V. A 1.5-Ω, 1% sense resistor sits across the JP3 terminals allowing 5-V current to be sensed as I5V = VR81-DROP / 1.5 Ω. 4 TPS92661EVM-001 LED Matrix Manager Evaluation Module (EVM) User's SLVUA51A-September 2014-Revised September 2014 Guide Submit Documentation Feedback

- Dot Matrix LED Displays - Broadcom Inc. — Dot Matrix LED Displays are capable of displaying a full range of alphanumeric characters and simple graphics when assembled in panels. Select up to four products for detailed comparison. Compare Clear All Download Table. Display. of 12 results. Grid List. Select. Product Line. Part Number. Filter by Part Number.

- TPS92662A-Q1 High Brightness LED Matrix Manager with EMI Mitigation ... — TPS92662A-Q1 High Brightness LED Matrix Manager with EMI Mitigation Techniques 1 1 Features 1• AEC-Q100 qualified for automotive applications - Grade 1: -40°C to 125°C ambient operating temperature - Device HBM classification level H1C - Device CDM classification level C5 • Input voltage range: 4.5 V to 60 V • 12 Integrated ...

- Q&A elects 6.3 Flashcards - Quizlet — Study with Quizlet and memorize flashcards containing terms like What is the standard schematic symbol used to designate LEDs?, The circuit symbols for all optoelectronic devices have arrows pointing either toward them or away from them. W hen the arrows point toward the symbol, what does this indicate?, When replacing LED displays, which of the following methods should you use to ensure that ...

- Tiny LED Matrix Display Clock : 8 Steps - Instructables — 4. 8 Characters LED Matrix: Device display is based on 2 x 4 characters LED Matrix display ICs, programmed via 3-wire interface, similar to the RTC circuit's DS1302, with single difference, that data providing line (SDI) is defined as MCU's output (Unless you want to add status check ability to your display circuit).

- SunFounder Newton Lab Kit for Raspberry Pi Pico 2 — SunFounder Newton ... — Thank you for choosing the SunFounder Newton Lab Kit!. This advanced learning kit, built around the Raspberry Pi Pico 2, offers a wide range of components, including displays, sound modules, drivers, controllers, and sensors, designed to give you a deep understanding of electronic devices.