Monostable-operation

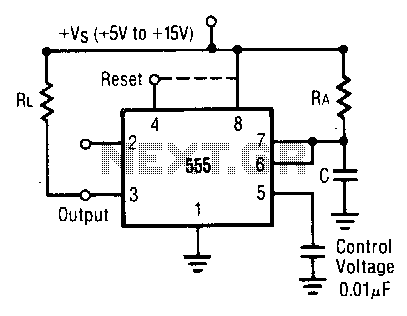

In this mode, the timer operates as a one-shot device. The external capacitor is initially kept discharged by a transistor internal to the timer. When a negative trigger pulse is applied to pin 2, the flip-flop is set, causing the output to go high and releasing the short circuit across the external capacitor. The voltage across the capacitor rises according to the time constant τ = R × C, until it reaches a threshold where the comparator resets the flip-flop, discharging the external capacitor. The output then transitions to a low state. Circuit triggering occurs when the negative-going trigger pulse reaches 1/3 of the supply voltage (Vs); the output remains high until the predetermined time elapses. The duration for which the output stays high is given by 1.1 τ, which can be determined from the associated graph. If a negative pulse is applied to pin 4 (reset) during the timing cycle, it will discharge the external capacitor and restart the cycle at the positive-going edge of the reset pulse. If the reset function is not utilized, pin 4 should be connected to Vs to prevent any unintended resets.

The described timer circuit is configured to operate in a monostable mode, commonly referred to as a one-shot timer. The core functionality relies on an external capacitor and resistor to define the timing interval. When the timer is triggered by a negative pulse at pin 2, the internal flip-flop is activated, resulting in a high output state that allows the capacitor to charge through the resistor. The charging process follows an exponential curve defined by the RC time constant (τ = R × C), thereby controlling the duration of the output high state.

The critical threshold for the trigger pulse is set at 1/3 of the supply voltage (Vs). This ensures that the circuit is responsive only to valid trigger signals, preventing accidental triggering from noise or spurious signals. The output will remain high for a duration of approximately 1.1 τ, which can be illustrated graphically to provide a clear understanding of the timing characteristics.

Additionally, the functionality of pin 4 as a reset input allows for immediate discharge of the external capacitor, enabling the system to restart the timing cycle. This feature is particularly useful for applications requiring precise timing control or for systems that need to respond quickly to external events. If the reset function is not intended for use, it is imperative to tie pin 4 to the supply voltage (Vs) to avoid unintended resets that could disrupt the operation of the timer.

Overall, this timer circuit provides a versatile solution for generating precise timing intervals, with clear mechanisms for triggering and resetting, making it suitable for various electronic applications ranging from simple delay timers to more complex timing sequences in automated systems.In this mode, the timer functions as a one shot. The external capacitor is initially held discharged by a transistor internal to the timer. Applying a negative trigger pulse to pin 2 sets the flip-flop, driving the output high, and releasing the short circuit across the external capacitor. The voltage across the capacitor increases with the time constant r ~ RAC to 213 V5, where the comparator resets the flip-flop and discharges the external capacitor.

The output is now in the low state. Circuit triggering takes place when the negative- going trigger pulse reaches 1/3 Vs; the circuit slaYs in the output high state until the set time elapses. The time the output remains in the high state is 1.1 RAC and can be determined by the graph. A negative pulse applied to pin 4 (reset) during the timing cycle will discharge the external capacitor and start the cycle over again beginning on the positive-going edge of the reset pulse.

If reset function is not used, pin 4 should be connected to Vs to avoid false resetting.

The described timer circuit is configured to operate in a monostable mode, commonly referred to as a one-shot timer. The core functionality relies on an external capacitor and resistor to define the timing interval. When the timer is triggered by a negative pulse at pin 2, the internal flip-flop is activated, resulting in a high output state that allows the capacitor to charge through the resistor. The charging process follows an exponential curve defined by the RC time constant (τ = R × C), thereby controlling the duration of the output high state.

The critical threshold for the trigger pulse is set at 1/3 of the supply voltage (Vs). This ensures that the circuit is responsive only to valid trigger signals, preventing accidental triggering from noise or spurious signals. The output will remain high for a duration of approximately 1.1 τ, which can be illustrated graphically to provide a clear understanding of the timing characteristics.

Additionally, the functionality of pin 4 as a reset input allows for immediate discharge of the external capacitor, enabling the system to restart the timing cycle. This feature is particularly useful for applications requiring precise timing control or for systems that need to respond quickly to external events. If the reset function is not intended for use, it is imperative to tie pin 4 to the supply voltage (Vs) to avoid unintended resets that could disrupt the operation of the timer.

Overall, this timer circuit provides a versatile solution for generating precise timing intervals, with clear mechanisms for triggering and resetting, making it suitable for various electronic applications ranging from simple delay timers to more complex timing sequences in automated systems.In this mode, the timer functions as a one shot. The external capacitor is initially held discharged by a transistor internal to the timer. Applying a negative trigger pulse to pin 2 sets the flip-flop, driving the output high, and releasing the short circuit across the external capacitor. The voltage across the capacitor increases with the time constant r ~ RAC to 213 V5, where the comparator resets the flip-flop and discharges the external capacitor.

The output is now in the low state. Circuit triggering takes place when the negative- going trigger pulse reaches 1/3 Vs; the circuit slaYs in the output high state until the set time elapses. The time the output remains in the high state is 1.1 RAC and can be determined by the graph. A negative pulse applied to pin 4 (reset) during the timing cycle will discharge the external capacitor and start the cycle over again beginning on the positive-going edge of the reset pulse.

If reset function is not used, pin 4 should be connected to Vs to avoid false resetting.