Programmable-gain-differential-input-amplifier

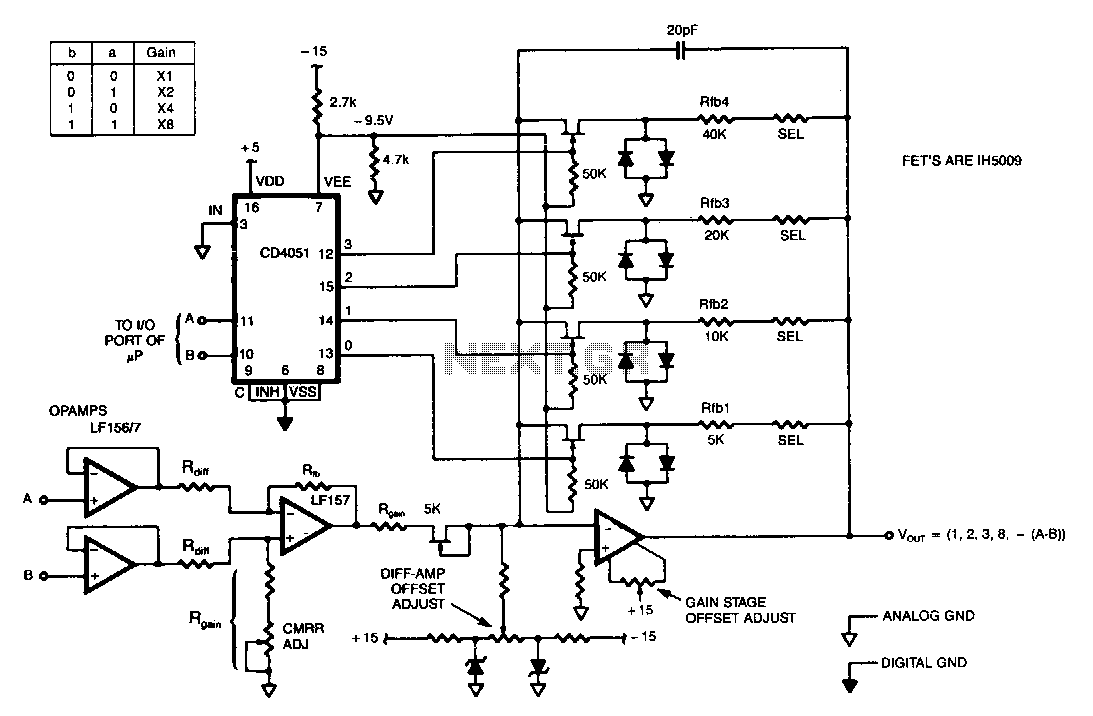

This programmable gain circuit utilizes a CD4051 CMOS Analog Multiplexer as a two to four line decoder, featuring appropriate FET drive for switching between feedback resistors to set the gain to one of four selectable values.

The described programmable gain circuit is designed to enhance signal processing by allowing for adjustable gain levels based on the selected feedback resistor configuration. The CD4051 CMOS Analog Multiplexer serves as the core component, functioning as a decoder that translates binary inputs into a corresponding output line, enabling the selection of one of four feedback resistors.

In this circuit, the gain settings are determined by the configuration of resistors connected to the feedback loop of an operational amplifier (op-amp). Each feedback resistor corresponds to a specific gain value, and the multiplexer facilitates the switching between these resistors based on control signals. The FET drive circuitry is crucial for ensuring that the switching action is fast and efficient, minimizing signal distortion and maintaining the integrity of the amplified signal.

The operation of the circuit can be summarized as follows: when a binary input is applied to the CD4051, it activates one of its output lines, allowing the corresponding feedback resistor to be connected to the op-amp. This selection process determines the gain of the amplifier, which can be adjusted dynamically during operation, making it suitable for applications requiring variable amplification based on changing signal conditions.

To further enhance performance, careful consideration should be given to the choice of feedback resistors, as their values will directly influence the gain settings. Additionally, the layout of the circuit should minimize parasitic capacitance and inductance, which can adversely affect the switching speed and overall performance of the programmable gain circuit. Proper power supply decoupling and grounding techniques should also be implemented to ensure stable operation.This programmable gain circuit employs a CD4051 CMOS Analog Multiplexer as a two to four line decoder, with appropriate FET drive for switching between feedback resistors to program the gain to any one of four values. 🔗 External reference

The described programmable gain circuit is designed to enhance signal processing by allowing for adjustable gain levels based on the selected feedback resistor configuration. The CD4051 CMOS Analog Multiplexer serves as the core component, functioning as a decoder that translates binary inputs into a corresponding output line, enabling the selection of one of four feedback resistors.

In this circuit, the gain settings are determined by the configuration of resistors connected to the feedback loop of an operational amplifier (op-amp). Each feedback resistor corresponds to a specific gain value, and the multiplexer facilitates the switching between these resistors based on control signals. The FET drive circuitry is crucial for ensuring that the switching action is fast and efficient, minimizing signal distortion and maintaining the integrity of the amplified signal.

The operation of the circuit can be summarized as follows: when a binary input is applied to the CD4051, it activates one of its output lines, allowing the corresponding feedback resistor to be connected to the op-amp. This selection process determines the gain of the amplifier, which can be adjusted dynamically during operation, making it suitable for applications requiring variable amplification based on changing signal conditions.

To further enhance performance, careful consideration should be given to the choice of feedback resistors, as their values will directly influence the gain settings. Additionally, the layout of the circuit should minimize parasitic capacitance and inductance, which can adversely affect the switching speed and overall performance of the programmable gain circuit. Proper power supply decoupling and grounding techniques should also be implemented to ensure stable operation.This programmable gain circuit employs a CD4051 CMOS Analog Multiplexer as a two to four line decoder, with appropriate FET drive for switching between feedback resistors to program the gain to any one of four values. 🔗 External reference