PULSE DELAY

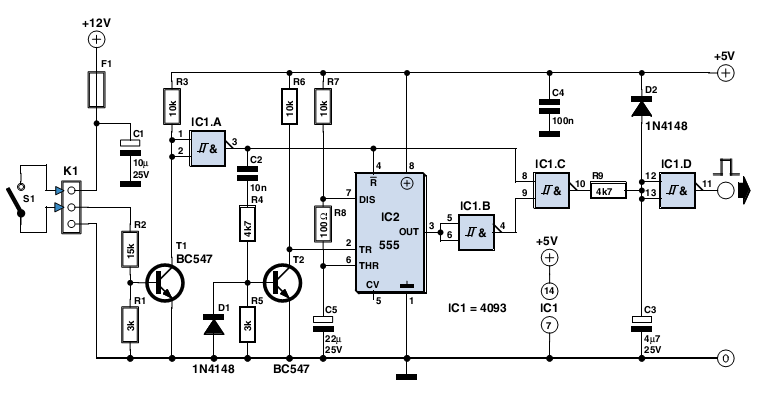

When a GATE signal (between 3V and 15V) is applied, the capacitor C5 functions as a differentiator, converting the gate signal into a brief positive pulse with a width of 10 ms. Diode D1 protects the circuit from negative voltages. The brief pulse generated at the rising edge of the GATE signal makes transistor Q1 briefly conductive, causing the voltage at its collector to drop to 0.2V. The collector is connected to the falling edge trigger pin of U1a, which triggers the monostable U1a, causing its output Q to rise to a high level and remain there for a duration determined by the RC network formed by (R5 + P1)C6. Here, P1 is a 1M logarithmic potentiometer, allowing the delay to be adjusted between 1 ms and 1 s. After this delay, Q returns to a low level, which in turn triggers the second monostable U1b. The output Q of U1b goes high and remains there for a duration set by the RC network formed by (R6 + P2)C7, where P2 is another 1M logarithmic potentiometer, also allowing for a delay between 1 ms and 1 s. The output Q is connected to a voltage divider (R7, R8) that produces the OUTPUT PULSE with an amplitude of 10V. The base of Q2 is connected to the Q output of U1b, driving the LD1 LED.

The described circuit operates in response to a GATE signal within a specified voltage range. The initial differentiating action of capacitor C5 is crucial for generating a precise pulse, which is then used to control subsequent monostable multivibrators (U1a and U1b). The first monostable multivibrator (U1a) is configured to output a high signal for a period defined by the time constant of the RC combination of resistor R5, potentiometer P1, and capacitor C6. The choice of a logarithmic potentiometer allows for finer control over the timing, making it suitable for applications requiring variable pulse widths.

Upon receiving the pulse, Q1 momentarily conducts, pulling the collector voltage low, which is essential for triggering U1a. The output from U1a then initiates a second timing sequence through U1b, utilizing a similar RC timing configuration with R6, P2, and C7. This second stage is designed to ensure that the output pulse duration can also be finely adjusted, providing versatility in the circuit's operation.

The voltage divider formed by resistors R7 and R8 is instrumental in scaling the output pulse to 10V, making it suitable for interfacing with other components or systems that require a specific voltage level. The final output drives an LED (LD1) through transistor Q2, providing a visual indication of the output pulse. The use of transistors for driving the LED ensures that the circuit can handle the necessary current without compromising the integrity of the timing circuit. Overall, this configuration allows for precise control of pulse generation, making it useful in a variety of electronic applications, such as signal processing, timing applications, and control systems.When a GATE signal (between 3V and 15V), the capacitor C5 acts as a differenciator and converts the gate signal into a brief positive pulse (width 10 ms). D1 protects the circuit from negative voltages. The brief pulse created on the rising edge of the GATE signal make Q1 briefly conductive and the voltage at its collecto

r falls down to 0. 2V. The collector is connected to the falling edge trigger pin of U1a. This triggers the monostable U1a and its output Q goes to a high level and stays there for a duration set by the RC cell built around (R5+P1)C6, P1 is a 1M log potentiometer and the delay can be set between 1ms and 1s. After this delay Q returns to the low level and in turn triggers the second monostable U1b whose output Q goes to the high level and stays there for a duration set by the RC cell built around (R6+P2)C7, P2 is a 1M log potentiometer and the delay can be set between 1ms and 1s.

The output Q is connected to a voltage divider (R7, R8) that delivers the OUTPUT PULSE with a amplitude of 10V. The base of Q2 is connected to the Q output of U1b and drives the LD1 LED. 🔗 External reference

The described circuit operates in response to a GATE signal within a specified voltage range. The initial differentiating action of capacitor C5 is crucial for generating a precise pulse, which is then used to control subsequent monostable multivibrators (U1a and U1b). The first monostable multivibrator (U1a) is configured to output a high signal for a period defined by the time constant of the RC combination of resistor R5, potentiometer P1, and capacitor C6. The choice of a logarithmic potentiometer allows for finer control over the timing, making it suitable for applications requiring variable pulse widths.

Upon receiving the pulse, Q1 momentarily conducts, pulling the collector voltage low, which is essential for triggering U1a. The output from U1a then initiates a second timing sequence through U1b, utilizing a similar RC timing configuration with R6, P2, and C7. This second stage is designed to ensure that the output pulse duration can also be finely adjusted, providing versatility in the circuit's operation.

The voltage divider formed by resistors R7 and R8 is instrumental in scaling the output pulse to 10V, making it suitable for interfacing with other components or systems that require a specific voltage level. The final output drives an LED (LD1) through transistor Q2, providing a visual indication of the output pulse. The use of transistors for driving the LED ensures that the circuit can handle the necessary current without compromising the integrity of the timing circuit. Overall, this configuration allows for precise control of pulse generation, making it useful in a variety of electronic applications, such as signal processing, timing applications, and control systems.When a GATE signal (between 3V and 15V), the capacitor C5 acts as a differenciator and converts the gate signal into a brief positive pulse (width 10 ms). D1 protects the circuit from negative voltages. The brief pulse created on the rising edge of the GATE signal make Q1 briefly conductive and the voltage at its collecto

r falls down to 0. 2V. The collector is connected to the falling edge trigger pin of U1a. This triggers the monostable U1a and its output Q goes to a high level and stays there for a duration set by the RC cell built around (R5+P1)C6, P1 is a 1M log potentiometer and the delay can be set between 1ms and 1s. After this delay Q returns to the low level and in turn triggers the second monostable U1b whose output Q goes to the high level and stays there for a duration set by the RC cell built around (R6+P2)C7, P2 is a 1M log potentiometer and the delay can be set between 1ms and 1s.

The output Q is connected to a voltage divider (R7, R8) that delivers the OUTPUT PULSE with a amplitude of 10V. The base of Q2 is connected to the Q output of U1b and drives the LD1 LED. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713