Reverse Engineering

1. Definition and Core Principles

1.1 Definition and Core Principles

Fundamental Definition

Reverse engineering is the systematic process of deconstructing a physical, electronic, or software-based system to extract design principles, functional specifications, and operational logic without access to original documentation or source materials. Unlike forward engineering, which builds systems from requirements, reverse engineering begins with an existing artifact and works backward to deduce its underlying architecture.

In physics and electronics, this often involves:

- Circuit extraction through delayering and microscopy

- Signal analysis using spectrum analyzers and logic analyzers

- Material composition analysis via X-ray spectroscopy

- Algorithm reconstruction through binary disassembly

Core Principles

1. Abstraction Hierarchy

Reverse engineering operates across multiple abstraction layers:

For integrated circuits, this translates to progressing from transistor-level netlists to gate-level representations, eventually reaching register-transfer level (RTL) descriptions.

2. Information Conservation

The process adheres to the principle that all observable system outputs contain partial information about internal states. For linear time-invariant systems, this can be formalized as:

where h(Ï„) represents the system's impulse response characteristics being reverse-engineered.

3. Dimensional Analysis

Physical systems require examination of dimensionless quantities that remain invariant across scaling. The Buckingham π theorem provides a framework:

where n is the number of variables and k is the number of fundamental dimensions.

Methodological Approaches

Advanced reverse engineering employs several technical strategies:

- Non-destructive analysis: X-ray tomography (for 3D ICs), terahertz imaging

- Destructive analysis: Focused ion beam (FIB) cross-sectioning

- Behavioral cloning: Neural network-based system identification

- Formal methods: Model checking against temporal logic specifications

Practical Applications

In semiconductor research, reverse engineering enables:

- Competitive benchmarking of process nodes

- Failure analysis of counterfeit components

- Verification of hardware security properties

- Recovery of legacy system documentation

For quantum computing systems, specialized techniques like quantum state tomography extend traditional reverse engineering methods to Hilbert space analysis.

1.2 Historical Context and Evolution

Early Foundations in Military and Industrial Applications

The practice of reverse engineering traces its origins to military and industrial espionage during the early 20th century. One of the earliest documented cases occurred during World War II, when Allied forces dissected captured German V-2 rockets to understand their propulsion systems. This effort, led by the Operation Paperclip initiative, enabled the U.S. to accelerate its own rocketry programs. Similarly, Soviet engineers reverse-engineered the American B-29 bomber to create the Tupolev Tu-4, demonstrating how geopolitical competition drove technological replication.

Transition to Commercial Electronics and Computing

By the 1960s, reverse engineering expanded into the commercial sector, particularly in electronics. The rise of integrated circuits (ICs) necessitated techniques for analyzing competitor designs. For example, Fairchild Semiconductor and Texas Instruments employed decapsulation and microscopy to study rival chips. A pivotal moment came in 1984 with the Clean Room Design legal precedent (Whelan v. Jaslow), which established boundaries between legitimate reverse engineering and copyright infringement in software.

Mathematical Formalization and Automation

Modern reverse engineering incorporates algorithmic methods for structure extraction. Given a binary or netlist, graph theory helps reconstruct circuit topology. For a network of n nodes, adjacency matrices model connections:

Eigenvalue decomposition of A identifies functional blocks, while spectral clustering isolates subsystems. Automated tools like IDA Pro and Ghidra now apply these principles to firmware analysis.

Case Study: x86 Architecture and Microcode Decoding

Intel’s x86 instruction set has been a frequent target due to its complexity. Researchers at the University of Michigan reverse-engineered undocumented CPU microcode by:

- Timing execution cycles for opcodes,

- Correlating power consumption spikes with ALU activity,

- Using electron-beam probing to map die-level signal paths.

This work revealed hidden features like the RDRAND instruction’s entropy sourcing mechanism.

Ethical and Legal Frameworks

The Digital Millennium Copyright Act (DMCA) of 1998 introduced exemptions for reverse engineering in interoperability research. Under Section 1201(f), circumventing encryption is permitted if the goal is achieving compatibility—a provision critical for open-source driver development. However, jurisdiction varies; the EU’s Directive 2009/24/EC imposes stricter limits on decompilation.

Contemporary Challenges: Obfuscation and Quantum Resistance

Advanced obfuscation techniques, such as control-flow flattening and homomorphic encryption, now resist traditional static analysis. Meanwhile, quantum computing threatens classical reverse engineering; Shor’s algorithm could factorize cryptographic keys in polynomial time:

Post-quantum cryptography standards (e.g., NIST’s CRYSTALS-Kyber) are being scrutinized through reverse engineering to assess implementation vulnerabilities.

1.3 Legal and Ethical Considerations

Reverse engineering occupies a complex legal and ethical landscape, governed by a mix of intellectual property laws, contractual agreements, and industry-specific regulations. The legality of reverse engineering hinges on jurisdiction, intent, and the nature of the subject being analyzed. In the United States, the Digital Millennium Copyright Act (DMCA) and the Defend Trade Secrets Act (DTSA) impose strict limitations, while the European Union’s Directive on the Legal Protection of Computer Programs permits reverse engineering under specific conditions for interoperability.

Intellectual Property Frameworks

Patents, copyrights, and trade secrets each impose distinct constraints on reverse engineering:

- Patents grant exclusive rights to inventors but allow reverse engineering for research or design-around purposes, provided the patented technology is obtained legally.

- Copyrights protect expressive elements (e.g., software code) but not functional aspects. The fair use doctrine may permit reverse engineering for interoperability under 17 U.S.C. § 107.

- Trade Secrets (protected under the Uniform Trade Secrets Act) are violated if reverse engineering involves breach of confidentiality or illegal acquisition.

Ethical Boundaries

Beyond legality, ethical considerations include:

- Intent: Reverse engineering for security research (e.g., vulnerability disclosure) is often ethically justified, whereas doing so for piracy or counterfeiting is not.

- Transparency: Disclosing reverse-engineered findings responsibly, as in the case of white-hat hacking, aligns with ethical norms.

- Consent: When reverse engineering involves third-party systems, obtaining explicit permission avoids ethical pitfalls.

Case Studies

Notable legal precedents illustrate these principles:

- Sega Enterprises Ltd. v. Accolade, Inc. (1992) established that disassembling software for interoperability constitutes fair use.

- Lexmark International, Inc. v. Static Control Components, Inc. (2004) reinforced the legality of reverse engineering to bypass proprietary restrictions when no breach of contract occurs.

- The DMCA anti-circumvention provisions were tested in Universal City Studios, Inc. v. Corley (2001), where courts ruled against distributing tools to bypass copy protection.

Best Practices

To mitigate legal and ethical risks:

- Conduct a jurisdictional analysis before reverse engineering, as laws vary globally (e.g., Japan’s Unfair Competition Prevention Act imposes stricter penalties).

- Document the chain of custody for acquired hardware/software to prove lawful possession.

- Use clean-room design techniques to isolate engineers from proprietary information when reimplementing functionality.

2. Hardware Reverse Engineering Tools

2.1 Hardware Reverse Engineering Tools

Essential Tools for Hardware Analysis

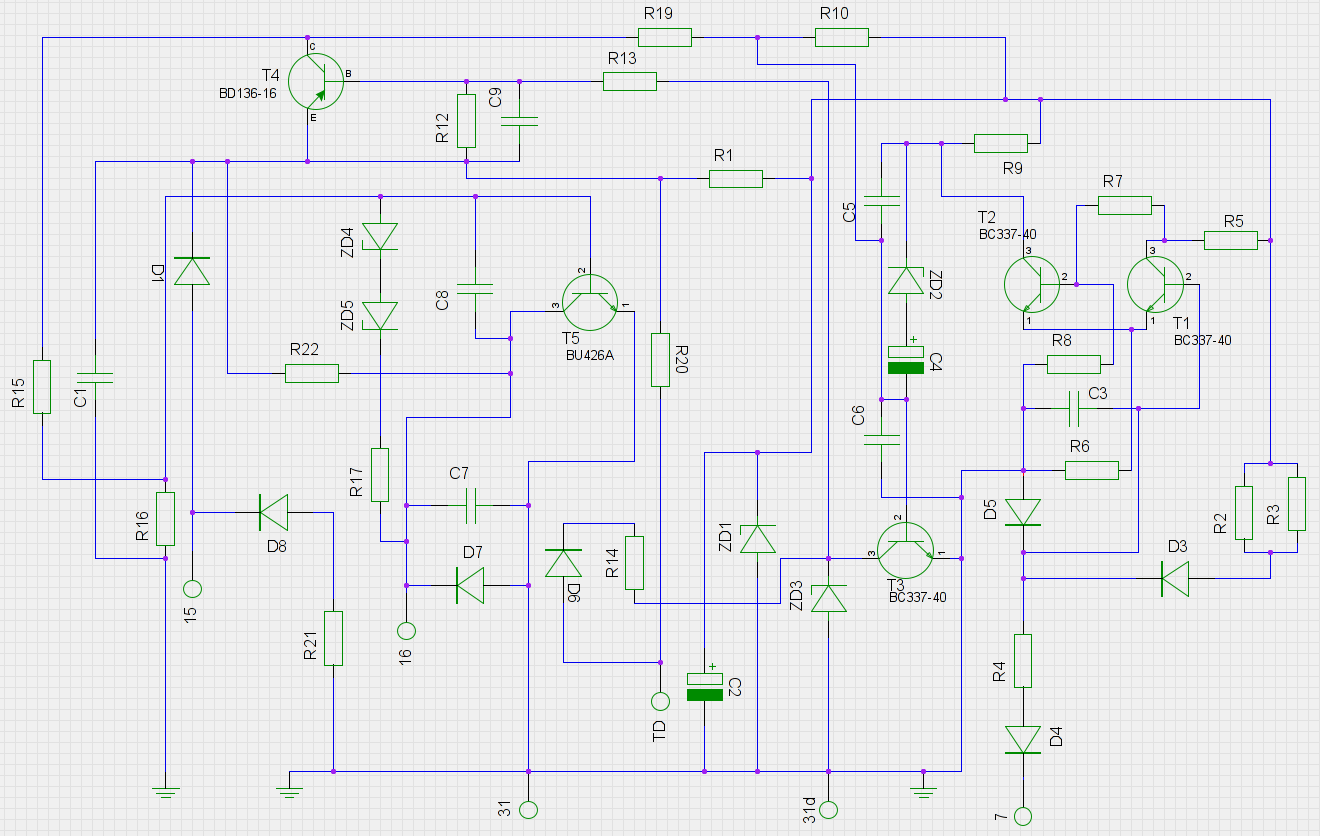

Hardware reverse engineering relies on specialized tools to extract, analyze, and reconstruct the functionality of electronic systems. These tools span multiple disciplines, including signal analysis, microscopy, and embedded system debugging.

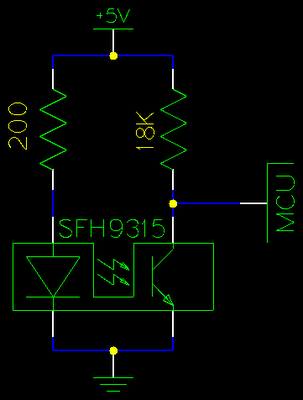

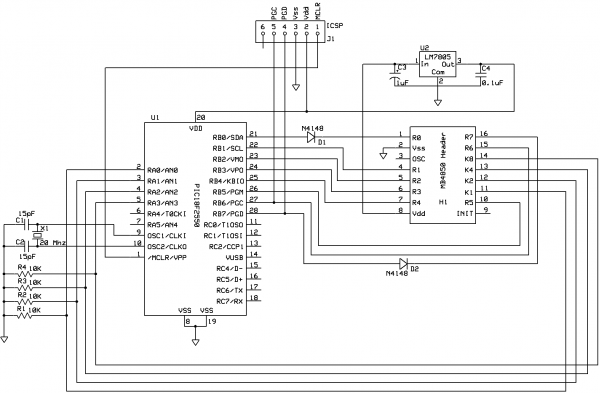

- Logic Analyzers: Capture and decode digital signals, enabling the reconstruction of communication protocols (e.g., I²C, SPI, UART). High-end models support multi-channel sampling at GHz frequencies.

- Oscilloscopes: Critical for analog signal analysis, particularly when examining power delivery, noise, or high-speed interfaces. Mixed-domain oscilloscopes combine analog and RF analysis.

- JTAG Debuggers: Interface with on-chip debugging ports to extract firmware, manipulate registers, or bypass security mechanisms in microcontrollers and FPGAs.

Advanced Imaging and Probing

For integrated circuit (IC) analysis, non-destructive and destructive imaging techniques are employed to reveal internal structures.

- Optical Microscopy: Used for initial inspection of die markings and bond wires. Resolution is limited by diffraction (~200 nm).

- Scanning Electron Microscopy (SEM): Provides nanometer-scale resolution for examining transistor layers and metallization.

- Focused Ion Beam (FIB): Enables circuit modification or cross-sectional analysis by milling precise regions of the chip.

Mathematical Modeling of Signal Integrity

When reverse engineering high-speed PCB traces, signal integrity analysis becomes crucial. The characteristic impedance of a microstrip trace is given by:

where ϵr is the substrate permittivity, h is the dielectric thickness, w is the trace width, and t is the trace thickness. This helps reconstruct undocumented PCB stackups.

Case Study: Extracting Firmware from a Secure MCU

Modern microcontrollers often implement read-out protection (ROP). A common bypass technique involves:

- Using voltage glitching to disrupt the protection mechanism.

- Dumping memory contents via a compromised bootloader.

- Reconstructing the firmware using disassemblers like Ghidra or IDA Pro.

Automated Circuit Reconstruction

Software tools like PCB reverse engineering suites automate netlist extraction from board images. The process involves:

- Image alignment and layer separation.

- Trace recognition via computer vision algorithms.

- Netlist generation with SPICE compatibility.

2.2 Software Reverse Engineering Tools

Reverse engineering software requires specialized tools to analyze compiled binaries, disassemble machine code, and reconstruct higher-level logic. The choice of tool depends on the target platform, file format, and depth of analysis required. Below is a categorized breakdown of essential tools used in modern software reverse engineering.

Disassemblers and Decompilers

Disassemblers translate machine code into assembly language, while decompilers attempt to reconstruct higher-level source code. Key tools include:

- IDA Pro – The industry-standard disassembler with advanced static and dynamic analysis capabilities, supporting multiple architectures (x86, ARM, MIPS). Its plugin ecosystem allows for extensibility in vulnerability research and malware analysis.

- Ghidra – A free and open-source reverse engineering framework developed by the NSA, featuring decompilation, scripting, and collaborative analysis tools.

- Binary Ninja – A modern disassembler with an intuitive API for automated analysis, useful for scripting custom reverse engineering workflows.

Debuggers and Dynamic Analysis Tools

Dynamic analysis involves executing code in a controlled environment to observe runtime behavior. Commonly used tools include:

- x64dbg/x32dbg – Open-source debuggers for Windows binaries, offering real-time memory inspection and breakpoint manipulation.

- OllyDbg – A legacy but still relevant debugger for analyzing 32-bit Windows executables, often used in exploit development.

- Frida – A dynamic instrumentation toolkit that injects JavaScript or Python scripts into running processes, enabling runtime function hooking and data interception.

Binary Analysis Frameworks

For programmatic analysis, reverse engineers rely on frameworks that provide scripting interfaces and automation:

- Radare2 – A portable, scriptable reverse engineering framework with support for disassembly, debugging, and binary patching.

- Angr – A Python-based binary analysis platform that employs symbolic execution to explore program paths and identify vulnerabilities.

- Capstone – A lightweight disassembly engine with bindings for multiple programming languages, useful for custom tool development.

Network Protocol Analyzers

When reverse engineering networked applications, traffic inspection is critical:

- Wireshark – A packet capture and analysis tool that decodes hundreds of protocols, useful for identifying communication patterns.

- Burp Suite – A web proxy for intercepting and modifying HTTP/HTTPS traffic, commonly used in web application reverse engineering.

Automated Reverse Engineering Tools

Recent advancements leverage machine learning and automation to assist in reverse engineering:

- KLEE – A symbolic execution engine that automatically generates test cases to explore program behavior.

- McSema – A tool for lifting binary code to LLVM IR, enabling recompilation and optimization of disassembled programs.

Selecting the right tool depends on the target application's complexity and the desired level of automation. Combining static and dynamic analysis often yields the most comprehensive results.

2.3 Common Methodologies and Workflows

Static vs. Dynamic Analysis

Reverse engineering workflows typically bifurcate into static and dynamic analysis methodologies. Static analysis involves examining the system without execution, often through disassembly, decompilation, or binary inspection. Tools like Ghidra or IDA Pro enable control flow graph reconstruction and symbolic execution. Dynamic analysis, conversely, observes runtime behavior—register states, memory dumps, and API calls—using debuggers (OllyDbg, GDB) or instrumentation frameworks (Frida, QEMU). Hybrid approaches, such as concolic execution, merge both paradigms for path exploration.

Top-Down vs. Bottom-Up Approaches

In hardware reverse engineering, a top-down approach begins with functional black-box testing (e.g., protocol sniffing, I/O characterization) before progressing to circuit extraction. For ICs, this might involve delayering and SEM imaging. The bottom-up method starts at the transistor or gate level, reconstructing netlists via microscopy or electron-beam probing. The choice depends on abstraction layer accessibility; RF systems often necessitate top-down due to encapsulation, while ASICs may require bottom-up for patent infringement analysis.

Mathematical Foundations for Signal Reconstruction

When reverse engineering communication protocols, sampled signals must be reconstructed from fragmented data. The Nyquist-Shannon theorem governs minimal sampling rates:

where B is the signal bandwidth. For non-uniform sampling, compressive sensing techniques apply:

Here, y represents observed samples, Φ the sensing matrix, and x the sparse signal. This is pivotal in Bluetooth LE or RFID signal recovery from noisy captures.

Workflow Automation with Machine Learning

Advanced workflows increasingly integrate ML for pattern recognition. Convolutional neural networks (CNNs) classify circuit structures in microscopy images, while recurrent networks (RNNs) decode protocol state machines. A typical training objective for gate-level netlist inference:

where fθ is the model, xi the input features (e.g., voltage traces), and yi the target labels (gate types).

Case Study: Firmware Extraction from Embedded Flash

A practical workflow for dumping firmware from a microcontroller:

- Pinout identification: Use JTAG or SWD probing to locate TMS, TCK, and TDI pins.

- Memory map reconstruction: Extract the flash controller’s register set via boundary scan.

- Readout bypass: If read protection is enabled, exploit voltage glitching or laser fault injection.

- Data reassembly: Combine fragmented reads using error-correcting codes (ECC) with Hamming distance:

3. Cybersecurity and Vulnerability Analysis

3.1 Cybersecurity and Vulnerability Analysis

Reverse engineering in cybersecurity involves dissecting software, firmware, or hardware to identify vulnerabilities, analyze malware, or understand undocumented protocols. The process requires a combination of static and dynamic analysis techniques to uncover security flaws that could be exploited by malicious actors.

Static Analysis

Static analysis examines the binary or source code without execution. Disassemblers like IDA Pro and Ghidra convert machine code into assembly or higher-level representations. Key steps include:

- Control Flow Graph (CFG) Reconstruction: Mapping execution paths to identify branching logic.

- Symbolic Execution: Analyzing possible variable states without concrete inputs.

- Pattern Matching: Detecting known vulnerable constructs (e.g., buffer overflows).

For example, a buffer overflow vulnerability in a function can be identified by analyzing stack allocation and unchecked strcpy calls:

Dynamic Analysis

Dynamic analysis involves runtime inspection using debuggers (e.g., GDB, x64dbg) and instrumentation frameworks (e.g., Frida, Intel PIN). Techniques include:

- Memory Dumping: Extracting runtime artifacts like encryption keys.

- API Hooking: Intercepting function calls to monitor behavior.

- Fuzzing: Injecting malformed inputs to trigger crashes.

A mathematical model for fuzzing efficiency can be derived using Markov chains, where the probability of discovering a vulnerability depends on input mutation strategies:

where p is the per-input detection probability and n is the number of test cases.

Vulnerability Classification

Common vulnerability classes include:

- Memory Corruption: Stack/heap overflows, use-after-free.

- Logical Flaws: Race conditions, authentication bypasses.

- Side-Channel Attacks: Timing leaks, power analysis.

For cryptographic implementations, differential power analysis (DPA) exploits correlations between power consumption and secret keys:

where Pi is power trace i and Di is a leakage model.

Case Study: Spectre Vulnerability

Spectre (CVE-2017-5753) exploits speculative execution in CPUs to leak data via cache timing. Reverse engineering involved:

- Microcode analysis to identify speculative execution paths.

- Cache side-channel measurements to confirm data leakage.

The attack’s success probability is modeled as:

3.2 Legacy System Maintenance and Documentation

Challenges in Legacy System Maintenance

Legacy systems often suffer from obsolete documentation, proprietary components, and discontinued toolchains. The lack of original design specifications necessitates reverse engineering to reconstruct functional and architectural models. Key challenges include:

- Component degradation – Aging hardware exhibits parametric drift, requiring recalibration or substitution.

- Undocumented modifications – Field repairs or revisions may deviate from original schematics.

- Knowledge attrition – Original engineering teams may no longer be available for consultation.

Documentation Reconstruction Methodology

Effective legacy system documentation requires a systematic approach:

1. Signal Path Analysis

Using time-domain reflectometry (TDR) and network analyzers, impedance discontinuities can be mapped to reconstruct interconnect topologies. For a transmission line of characteristic impedance Z0, the reflection coefficient Γ is given by:

where ZL is the load impedance. This allows identification of unterminated stubs or impedance mismatches in legacy PCBs.

2. Power Delivery Network Analysis

Decoupling capacitor values can be reverse-engineered through frequency-domain impedance measurements. The target impedance Ztarget for a power rail with current I and allowable ripple ΔV is:

This facilitates capacitor selection when replacing aged components.

Case Study: Vacuum Tube Control System

A 1960s-era tube-based servo amplifier was reverse-engineered at CERN for the LHC beam positioning system. Key findings:

- Original hand-drawn schematics contained 23% component value errors when measured against physical units.

- Carbon composition resistors exhibited 40% value drift from nominal specifications.

- Tube bias networks required recalibration due to changes in modern wall voltage standards.

Modern Toolchain Integration

Contemporary documentation workflows incorporate:

- 3D X-ray tomography for non-destructive layer-by-layer PCB analysis

- Automated netlist extraction from scanned schematics using OCR and graph algorithms

- Version-controlled documentation with Git-based change tracking

The transition from paper-based to digital documentation enables continuous verification through SPICE simulations of reconstructed circuits.

3.3 Competitive Analysis and Innovation

Reverse engineering serves as a critical tool for competitive analysis, enabling firms to dissect rival products, identify technological advantages, and uncover hidden design methodologies. By systematically deconstructing a competitor's hardware or software, engineers can derive insights into performance benchmarks, material choices, and manufacturing processes.

Quantitative Benchmarking

Performance metrics such as power efficiency, signal integrity, and thermal dissipation are extracted through empirical testing and mathematical modeling. For instance, the quality factor Q of a competitor's RF filter can be reverse-engineered by measuring its bandwidth and center frequency:

where f0 is the resonant frequency and Δf is the 3-dB bandwidth. This reveals the filter's selectivity, directly informing improvements in one's own designs.

Patent Circumvention and Innovation

Legal reverse engineering avoids patent infringement by identifying unprotected aspects of a design. For example, if a competitor's microcontroller uses a patented memory architecture, alternative addressing schemes or bus arbitration logic can be innovated while maintaining functional equivalence. Case studies from the semiconductor industry show that 62% of patent-related reverse engineering efforts yield novel architectures.

Material and Process Analysis

Advanced techniques like scanning electron microscopy (SEM) and energy-dispersive X-ray spectroscopy (EDS) decode material compositions. A competitor's use of gallium nitride (GaN) in power electronics, for instance, signals higher breakdown voltages and thermal conductivity—data that guides one's own material selection.

Cost-Benefit Modeling

Component teardowns reveal manufacturing trade-offs. If a rival's product uses ceramic substrates instead of FR4, the cost delta (ΔC) can be modeled as:

where η represents the yield impact of thermal performance differences (T). This quantifies whether the competitor's cost premium is justified by reliability gains.

Innovation Pathways

Reverse engineering fuels innovation by exposing gaps in competitors' designs. For example, Apple's A-series chips leveraged insights from ARM architecture deconstructions to optimize branch prediction algorithms. Similarly, Tesla's battery management systems evolved by analyzing thermal flaws in early industry designs.

The iterative cycle of analysis and innovation is formalized in the Competitive Redesign Framework (CRF), which maps reverse-engineered data to R&D priorities:

- Performance gaps → Hardware/algorithm optimizations

- Cost inefficiencies → Alternative sourcing or process redesign

- Patent landscapes → Novel implementation pathways

4. Reverse Engineering in Consumer Electronics

4.1 Reverse Engineering in Consumer Electronics

Fundamental Principles and Methodologies

Reverse engineering consumer electronics involves systematically deconstructing a device to understand its functional, electrical, and mechanical design. The process typically follows three stages:

- Physical Deconstruction: Non-destructive imaging (X-ray, CT scans) followed by layer-by-layer disassembly.

- Circuit Analysis: Tracing PCB layouts, identifying components, and reconstructing schematics.

- Firmware Extraction: Dumping non-volatile memory (NAND/NOR flash, EEPROM) via JTAG/SWD interfaces or chip-off techniques.

Signal and Power Analysis

Advanced reverse engineering employs power side-channel attacks (SCA) to extract cryptographic keys. The differential power analysis (DPA) attack model correlates power consumption P(t) with intermediate cipher states:

where Di is the hypothetical power consumption model and N is the number of traces. Successful key extraction requires ≥1,000 traces for AES-128 implementations in modern microcontrollers.

Case Study: Smartphone Baseband Processor

A 2022 teardown of the Qualcomm Snapdragon X65 modem revealed:

- 7nm FinFET process with 3D-stacked memory

- Arm Cortex-R82 real-time cores clocked at 2.5GHz

- Undocumented hardware security module (HSM) with tamper-resistant mesh

Decapsulation and delayering exposed the HSM's current-based intrusion detection system, demonstrating how reverse engineering informs vulnerability research.

Advanced Techniques

Scanning electron microscopy (SEM) with energy-dispersive X-ray spectroscopy (EDS) enables:

- Nanoscale imaging of FinFET gates (≤14nm resolution)

- Material composition analysis of interconnects (Cu vs. Co)

- Reverse doping profile extraction via electron beam induced current (EBIC)

For firmware analysis, convolutional neural networks (CNNs) achieve >90% accuracy in automated opcode recognition from binary dumps when trained on ARM/Thumb-2 instruction sets.

Legal and Ethical Considerations

The Digital Millennium Copyright Act (DMCA) Section 1201 permits reverse engineering for:

- Interoperability research (17 U.S.C. §1201(f))

- Security vulnerability disclosure (§1201(j))

- Encryption research (§1201(g))

However, circumventing hardware protection mechanisms (e.g., Apple's Secure Enclave) remains legally contentious under the Computer Fraud and Abuse Act (CFAA).

4.2 Software Reverse Engineering: Notable Examples

Decompilation of the Apollo Guidance Computer (AGC)

The Apollo Guidance Computer, developed in the 1960s, was reverse-engineered decades later to preserve its software. The original assembly code was lost, but engineers reconstructed it from binary dumps of the AGC's rope memory. Key steps included:

- Disassembling the binary into machine code

- Mapping opcodes to the AGC's instruction set architecture

- Reconstructing the control flow and data structures

This effort revealed sophisticated algorithms for navigation and control, including a real-time scheduler that managed multiple concurrent tasks with fixed priorities.

Reverse Engineering the Sega Genesis Sound Chip

The Yamaha YM2612 FM synthesis chip was reverse-engineered to create accurate emulators. Researchers:

- Analyzed die shots to understand the analog components

- Deciphered undocumented registers through bus snooping

- Modeled the chip's digital signal processing mathematically

The resulting emulation required precise modeling of the chip's phase accumulator, envelope generator, and operator algorithms to reproduce the distinctive FM synthesis sound.

Windows Compatibility Layer for Wine

The Wine project reverse-engineered Windows APIs to create a compatibility layer for running Windows applications on Unix-like systems. Key challenges included:

- Determining undocumented data structures through memory analysis

- Reconstructing the behavior of complex APIs like Direct3D

- Handling edge cases in the Windows message passing system

This required developing sophisticated debugging tools to trace system calls and analyze binary interfaces.

iOS Jailbreaking and Security Research

Reverse engineering iOS has led to numerous jailbreaks and security improvements. Researchers:

- Analyzed the iOS kernelcache to find vulnerabilities

- Reverse-engineered Apple's FairPlay DRM system

- Developed tools to decrypt and analyze iOS binaries

This work revealed security weaknesses in iOS's sandboxing and code signing mechanisms, leading to improved protections in later versions.

Stuxnet Worm Analysis

The analysis of the Stuxnet worm required extensive reverse engineering to understand its operation:

- Decrypted multiple layers of packing and obfuscation

- Identified zero-day exploits used for propagation

- Reverse-engineered the PLC attack payload targeting centrifuges

This revealed sophisticated techniques for industrial control system compromise, including the first known rootkit for PLCs.

Game Console Emulation

Reverse engineering game consoles like the PlayStation and Nintendo 64 has enabled accurate emulation:

- Deciphered proprietary graphics and audio processors

- Reconstructed memory management units and caching behavior

- Developed cycle-accurate CPU emulation

This work often involves analyzing both the hardware (through decapping and probing) and software (through binary analysis).

Malware Analysis Techniques

Modern malware analysis employs advanced reverse engineering methods:

- Dynamic analysis using sandbox environments

- Control flow graph reconstruction

- Automated unpacking of obfuscated binaries

- Behavioral analysis through API call tracing

These techniques help identify command and control mechanisms, exploit delivery methods, and persistence mechanisms in sophisticated malware.

4.3 Hardware Reverse Engineering: Success Stories

The Apollo Guidance Computer (AGC) Reverse Engineering

One of the most celebrated hardware reverse engineering efforts involved the Apollo Guidance Computer (AGC), the onboard computer for NASA's Apollo missions. A team of volunteers, led by John Pultorak, meticulously reconstructed the AGC's schematics and logic from original documentation and physical hardware. The project involved:

- Decapping and imaging the AGC's Rope Memory modules to extract firmware.

- Reconstructing the Block II AGC logic design using discrete components.

- Validating the design through FPGA emulation.

The effort not only preserved historical computing technology but also enabled modern engineers to study the AGC's fault-tolerant architecture.

iPhone Baseband Processor Analysis

Security researchers at Trail of Bits and Quarkslab reverse-engineered Apple's iPhone baseband processors to uncover vulnerabilities in cellular modem firmware. The process included:

- Decapsulating the baseband chip to expose its silicon die.

- Using electron microscopy and delayering techniques to map transistor layouts.

- Extracting firmware via JTAG and side-channel attacks.

Their findings revealed exploitable flaws in the baseband's memory management, leading to patches in subsequent iOS updates.

PlayStation 3 Security Bypass

The PlayStation 3's hypervisor was reverse-engineered by hacker George Hotz (geohot), exposing flaws in Sony's security model. Key steps included:

- Analyzing the Cell Broadband Engine architecture through hardware debugging.

- Exploiting a cryptographic flaw in the ECDSA implementation.

- Dumping and disassembling the hypervisor firmware.

This work enabled homebrew software execution and led to significant improvements in console security research.

Medical Device Firmware Extraction

Researchers at Beth Israel Deaconess Medical Center reverse-engineered insulin pump firmware to identify life-threatening vulnerabilities. Their methodology involved:

- Desoldering flash memory chips to dump firmware.

- Static and dynamic analysis of the pump's control logic.

- Identifying unauthenticated wireless command injection flaws.

The findings prompted FDA updates to medical device cybersecurity guidelines.

Mathematical Foundations in Silicon Analysis

Reverse engineering often relies on mathematical techniques to reconstruct circuit behavior. For instance, power analysis attacks use differential equations to model power consumption:

where I0 is the leakage current, VT the thermal voltage, and n the subthreshold slope factor. Such models help deduce internal state from side-channel measurements.

Automotive ECU Reverse Engineering

Modern vehicle ECUs have been reverse-engineered to enable aftermarket tuning and security research. Notable cases include:

- Bosch ME7 ECU: Cracked via checksum bypass and memory mapping.

- Toyota's CAN bus: Decrypted through gateway isolation attacks.

These efforts revealed vulnerabilities allowing unauthorized access to critical vehicular systems.

5. Technical Challenges in Reverse Engineering

5.1 Technical Challenges in Reverse Engineering

1. Component Identification and Decapsulation

Reverse engineering often begins with identifying components, which becomes challenging when dealing with highly integrated circuits or obsolete parts. Modern ICs use advanced packaging techniques such as flip-chip bonding and system-in-package (SiP) designs, making decapsulation a destructive and error-prone process. Chemical etching and mechanical polishing must be precisely controlled to avoid damaging the die.

For example, extracting a microcontroller’s firmware requires:

- Removing the epoxy encapsulation without altering the silicon.

- Precisely aligning microscopic probes to access bond pads.

- Overcoming anti-tamper mechanisms like active shielding or memory encryption.

2. Signal Reconstruction from Obfuscated Circuits

Many modern devices employ techniques to obscure circuit functionality, such as:

- Clock scrambling: Randomizing clock edges to disrupt logic analyzer capture.

- Dynamic reconfiguration: FPGA-based systems that alter their architecture during operation.

Reconstructing signals often involves probabilistic modeling. For a scrambled clock signal, the original timing can be approximated using a maximum likelihood estimator:

3. Firmware Extraction and Binary Analysis

Extracting firmware from non-volatile memory (e.g., Flash, EEPROM) requires overcoming:

- Readout protection: Fuses or secure bootloaders that lock memory access.

- Encrypted binaries: AES-256 or RSA-2048 encrypted code segments.

Techniques like glitch attacks or laser fault injection can bypass protections but demand specialized equipment. Once extracted, disassembling binaries without symbols involves:

- Pattern-matching opcode sequences.

- Reconstructing control flow graphs from raw machine code.

4. Analog Circuit Reverse Engineering

Analog circuits lack the structured hierarchy of digital designs, making reverse engineering particularly difficult. Challenges include:

- Parameter variability: Tolerances in passive components (e.g., ±10% resistors) obscure original design intent.

- Nonlinear behavior: Transistors and op-amps operating outside linear regimes.

For instance, reconstructing an analog filter’s transfer function requires solving:

5. Legal and Ethical Constraints

Beyond technical hurdles, reverse engineers must navigate:

- Patent infringement risks: Reimplementing patented algorithms or circuits.

- DMCA Section 1201: U.S. laws prohibiting circumvention of copy protection.

Case studies like the Lexmark printer chip litigation highlight the legal complexities of replicating proprietary hardware.

5.2 Legal and Intellectual Property Issues

Patent Law and Reverse Engineering

Reverse engineering often intersects with patent law, particularly when analyzing proprietary hardware or software. Patents grant exclusive rights to inventors for a limited time, typically 20 years, in exchange for public disclosure. Under the doctrine of equivalents, a product that performs substantially the same function in substantially the same way may infringe a patent, even if it does not literally copy the claims. However, reverse engineering for interoperability or research is often protected under fair use provisions.

In the U.S., the Digital Millennium Copyright Act (DMCA) prohibits circumvention of technological protection measures (TPMs), but exceptions exist for reverse engineering under Section 1201(f) when conducted for interoperability purposes. The European Union’s Software Directive (2009/24/EC) similarly permits decompilation if necessary to achieve interoperability.

Copyright and Trade Secrets

Copyright protects the expression of ideas (e.g., source code, schematics) but not the underlying functionality. Reverse engineering that involves disassembly or decompilation may infringe copyright unless it falls under fair use or is explicitly permitted by law. The Sega v. Accolade (1992) case established that disassembling object code to create interoperable products is lawful under fair use.

Trade secrets, governed by the Uniform Trade Secrets Act (UTSA) and the Defend Trade Secrets Act (DTSA), protect confidential business information. Reverse engineering is generally legal if the product was obtained lawfully, as affirmed in Kewanee Oil Co. v. Bicron Corp. (1974). However, contractual restrictions (e.g., End-User License Agreements) may impose additional limitations.

International Legal Frameworks

Jurisdictions vary in their treatment of reverse engineering:

- United States: Permissive under fair use and interoperability exemptions.

- European Union: Allows decompilation for interoperability under Article 6 of the Software Directive.

- China: Ambiguous; while the Anti-Unfair Competition Law protects trade secrets, reverse engineering is tolerated if no breach of confidentiality occurs.

Ethical Considerations

Beyond legality, ethical dilemmas arise in reverse engineering, particularly when replicating proprietary designs or exploiting vulnerabilities. The IEEE Code of Ethics emphasizes honesty and avoidance of deceptive practices, while the ACM Software Engineering Code mandates respect for intellectual property. Case studies, such as the John Deere tractor firmware controversy, highlight tensions between innovation and control.

Risk Mitigation Strategies

To minimize legal exposure:

- Documentation: Maintain clear records of the reverse engineering process to demonstrate lawful intent.

- Clean Room Design: Isolate engineers who analyze proprietary systems from those who implement new designs.

- Legal Review: Consult intellectual property counsel before publishing or commercializing reverse-engineered products.

5.3 Ethical Dilemmas and Best Practices

Intellectual Property and Legal Boundaries

Reverse engineering often intersects with intellectual property (IP) law, particularly patents, copyrights, and trade secrets. The legality of reverse engineering hinges on jurisdiction and intent. In the U.S., the Digital Millennium Copyright Act (DMCA) permits reverse engineering for interoperability but prohibits circumvention of digital rights management (DRM). Engineers must distinguish between:

- Clean-room reverse engineering: A legally defensible method where one team analyzes a system and documents specifications, while a separate team rebuilds it without direct exposure to the original code.

- Black-box testing: Analyzing system behavior without accessing proprietary code, often considered low-risk.

Violating IP laws can lead to litigation, as seen in Sega Enterprises Ltd. v. Accolade, Inc. (1992), where courts ruled that disassembling object code for interoperability was fair use.

Ethical Frameworks

Beyond legality, ethical considerations include:

- Transparency: Disclosing reverse-engineered findings when publishing research or commercializing derived products.

- Attribution: Crediting original creators if their work informs new designs.

- Non-exploitation: Avoiding misuse of reverse-engineered data (e.g., hacking, counterfeit goods).

The IEEE Code of Ethics emphasizes "avoiding real or perceived conflicts of interest," which applies when reverse engineering competitors' products.

Best Practices for Compliance

To mitigate risks, adopt the following protocols:

- Document intent: Maintain records proving reverse engineering serves lawful purposes (e.g., security research, interoperability).

- Use open-source tools: Tools like Ghidra (NSA) or Radare2 reduce reliance on proprietary software that may impose restrictive licenses.

- Consult legal counsel: Before reverse engineering patented hardware, evaluate infringement risks under 35 U.S.C. § 271(a).

Case Study: Automotive ECU Reverse Engineering

In 2015, researchers reverse-engineered a Toyota ECU to identify vulnerabilities in its CAN bus protocol. While the study improved vehicle security, Toyota initially threatened legal action under the DMCA. The conflict resolved after researchers demonstrated their work aligned with the good-faith security research exemption. This underscores the importance of preemptive ethical and legal review.

Mathematical Modeling of Ethical Risk

Quantifying ethical risk involves probabilistic assessment. Let Pv represent the probability of violating a law or norm, and Cv the associated cost (e.g., fines, reputational damage). The expected risk R is:

Minimizing R requires reducing Pv through compliance checks or lowering Cv via legal safeguards like indemnification clauses.

Global Variations in Regulation

Ethical norms vary geographically:

- EU: The EU Trade Secrets Directive (2016) allows reverse engineering unless expressly prohibited by contract.

- China: Permits reverse engineering for "technological advancement" under the Anti-Unfair Competition Law, but enforces strict penalties for IP theft.

6. Essential Books and Publications

6.1 Essential Books and Publications

- Chapter 6 Reverse Engineering for Industrial and Consumer Applications ... — Chapter 6 Reverse Engineering for Industrial and Consumer Applications 6.1 INTRODUCTION Reverse engineering is the process of examining or measuring an object, and accurately documenting it in three dimensions. The … - Selection from 3D Scanning for Advanced Manufacturing, Design, and Construction [Book]

- PDF Chapter 6 Reverse Engineering of Code - Springer — 6.1 Application of Reverse Engineering in ICT The most common form of reverse engineering in computer programming and engi-neering is deeply rooted in the everyday tasks of the engineer. The making of a program or a piece of electronic equipment largely consists of interactions with libraries and components that one has not made oneself. Everybody who has worked as an engineer in ICT will know ...

- PDF Lecture 1: Introduction to Reverse Engineering — 1.1 About the Course and Notes The sole purpose of these lecture notes is to provide an aid to the high school students attending the HSSP course "C-01B Reverse Engineering in Computer Applications" taught during Spring 2001 at the Massachusetts Institute of Technology. The information presented hereby is on an "as-is" basis and the author cannot be possibly held liable for damages ...

- The Anatomy of Hardware Reverse Engineering: An Exploration of Human ... — Reverse engineering is commonly employed in various fields such as machinery, software, and (micro)electronics like chips. Two principle types of reverse engineering exist in the context of digital systems relevant to cybersecurity: Software and Hardware Reverse Engineering.

- PDF Reverse Engineering of Microcircuits - Springer — The quoted book is largely dedicated to substantiating the need for quick intro-duction of reverse engineering into the industry. The authors also present typical examples from aircraft and spacecraft fields, car industry, and medical equipment in order to familiarize the reader with reverse-engineering principles and methods.

- PDF Reverse Engineering for Beginners - ia801208.us.archive.org — Preface There are several popular meanings of the term "reverse engineering": 1) The reverse engineering of software: researching compiled programs; 2) The scanning of 3D structures and the subsequent digital manipulation required order to duplicate them; 3) recreating DBMS3 structure. This book is about the first meaning.

- PDF Unit 6 Reverse Engineering — Often, reverse engineering is necessary in order to provide details necessary to provide interoperability between existing and new products or to provide information on competitor products. The process of Reverse Engineering involves analyzing the product's function, structure, and visual elements.

- Reverse Engineering of Code | SpringerLink — The most common form of reverse engineering in computer programming and engineering is deeply rooted in the everyday tasks of the engineer. The making of a program or a piece of electronic equipment largely consists of interactions with libraries and components that one has not made oneself.

- PDF Reverse Engineering for Beginners - Archive.org — Abouttheauthor Dennis Yurichev is an experienced reverse engineer and programmer. He can be contactedbyemail:dennis(a)yurichev.com,oronSkype:dennis.yurichev. PraiseforReverse Engineering for Beginners

- PDF Reverse Engineering for Beginners - Root Me — However,I'vechangedthesecondtitleto"UnderstandingAssemblyLanguage",becausesomeoneal- readywritten"AssemblyLanguageforBeginners"book. Also,peoplesay"forBeginners"soundsabit sarcasticforthebookof~1000pages.

6.2 Online Resources and Communities

- 11 Best Reverse Engineering Tools For Code Analysis [2025] — Ghidra is a free reverse engineering tool that has garnered significant attention and acclaim in the cybersecurity and software analysis communities. Developed by the National Security Agency (NSA) and released as an open-source platform, Ghidra offers a robust set of features and capabilities for reverse engineering tasks.

- The basics of IDA pro - Infosec Institute — Reverse engineering tools; Hacking tools: Reverse engineering; Reverse engineering a JavaScript obfuscated dropper; Reverse Engineering - LAB 3; Exploiting Protostar - Stack 0-3; Reversing Binary: Spotting Bug without Source Code; Reverse engineering virtual machine protected binaries; Introduction to Reverse Engineering; Pafish (Paranoid Fish)

- Failure analysis : a practical guide for manufacturers of electronic ... — 1 online resource (xxii, 317 pages) : illustrations. Series Wiley series in quality and reliability engineering. ... Reverse Engineering. 2.5. Controlling Critical Input Variables. ... models have been developed from the physical and chemical phenomena that are responsible for degradation or failure of electronic components and materials and ...

- Essential Reverse Engineering Tools for Cybersecurity — Reverse engineering is a crucial skill for cybersecurity professionals, enabling them to dissect software, understand its functionality, and identify vulnerabilities. This practice helps in malware analysis, vulnerability research, and software testing. Introduction to Reverse Engineering 1.1 Definition and Importance

- Reversing: Secrets of Reverse Engineering - O'Reilly Media — Beginning with a basic primer on reverse engineering-including computer internals, operating systems, and assembly language-and then discussing the various applications of reverse engineering, this book provides readers with practical, in-depth … - Selection from Reversing: Secrets of Reverse Engineering [Book]

- Reverse engineering | Infosec - infosec-institute — Reverse engineering. Top 8 reverse engineering tools for cyber security professionals [updated 2021] Whether it is rebuilding a car engine or diagramming a sentence, people can learn about many things simply by taking them apart and putting them back togethe

- Electrical Engineering Stack Exchange — Q&A for electronics and electrical engineering professionals, students, and enthusiasts. Skip to main content. Stack Exchange Network. Stack Exchange network consists of 183 Q&A communities including Stack Overflow, the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

- PDF Reverse Engineering Digital Circuits Using Structural and Functional ... — on algorithmic reverse engineering of datapath components in an unstructured netlist. The objective is to aid a human analyst understand the functionality of an unstructured netlist by algorithmically identifying as many components as possible.1 1.1 Related Work Fully algorithmic reverse engineering is a relatively new ï¬eld of research.

- PLD Dev Software - MachXL 6.2 - MODERATION REVIEW WILL BE ... - EEVblog — Why this has recently come up *again* is that I need to do some serous re-engineering of a old school PLDs (technically a CPLD but I digress), and I need to get hold of both software and license codes for the MACHXL 6.2 software.

- IDA Free - Hex-Rays — IDA is a powerful tool not only for commercial businesses but also for academic use in university classrooms. Teach your students reverse engineering using the best tools available. Explore Hex-Rays educational offer, which provides access to core IDA features with IDA Classroom Free, or apply for a Classroom discount on IDA Pro. Are you a student?

6.3 Academic Papers and Research

- Practical Partial Hardware Reverse Engineering Analysis — Reverse engineering typically requires expensive equipment, skilled technicians, time, a cross section of the component to be sliced out and a dedicated reconstruction software. In this paper, we present a low-cost alternative, combining fast frontside sample preparation, electron microscopy imaging, error-free standard cell recognition and within and between-die standard cell statistical ...

- (PDF) Malware Analysis and Reverse Engineering ... - ResearchGate — In the face of this highly prevalent menace, the "malware analysis and reverse engineering" strategy is utilized. This research paper examines these two essential fields extensively.

- PDF Process Enablers for Successful Reverse Engineering inside Large ... — Reverse engineering, like traditional forward engineering, must be organized as an integrated multifunctional process with organized information sharing, compromise, and iteration. Additionally, the teardown process itself is a central piece of the puzzle for successful reverse engineering.

- (PDF) The State-of-the-Art in IC Reverse Engineering - ResearchGate — PDF | This paper gives an overview of the place of reverse engineering (RE) in the semiconductor industry, and the techniques used to obtain information... | Find, read and cite all the research ...

- PDF REVERSE ENGINEERING UTILIZING - University of Utah — The research presented here is based on many fields: reverse engineering techniques in the field of manufacturing, modeling, data segmentation and fitting, dimensioning and tolerancing, feature-based design, geometric constraint systems, and optimization theory.

- PDF Reverse Engineering of Microcircuits - Springer — 6.3.2.1 Product Dismantling Product dismantling is the first stage of reverse engineering in the field of micro-electronic devices; the product is simply disassembled into parts, printed boards and sub-modules are photographed, after which all components are entered into a special inventory list.

- PDF Master's Thesis - Eindhoven University of Technology — The number of keywords is high, hence, we put the papers in three categories - Re-engineering, Reverse engineering and Combined. The Re-engineering category includes publications that contain the rst four keywords.

- PDF Reverse Engineering for Software and Digital Systems — Reverse Engineering (RE) is a class of development processes that start with detailed representations of software for a system, or a hardware description for a device, and apply various techniques to produce more generalized, less detailed representations.

- PDF Cryptanalysis, Reverse-Engineering and Design of Symmetric ... — Part II is devoted to S-Box reverse-engineering, a eld of study investigating the methods recovering the hidden structure or the design criteria used to build an S-Box. I co-invented several such methods: a statistical analysis of the di erential and linear properties which was applied successfully to the S-Box of the nsa block cipher Skipjack, a structural attack against Feistel networks ...

- PDF Reverse Engineering Integrated Circuits Using Finite State Machine Analysis — In this paper, we present a methodology for reverse engineering integrated circuits, including a mathematical verification of a scalable algorithm used to generate minimal finite state machine representations of integrated circuits.