Tracking-adc

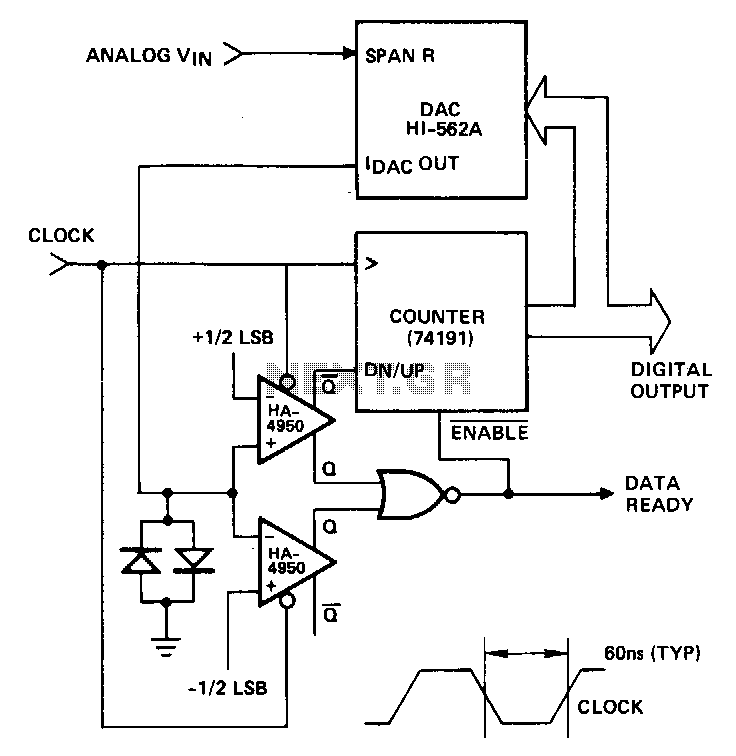

The analog input is connected to the span resistor of a Digital-to-Analog Converter (DAC). The voltage range of the analog input is selectable, mirroring the output voltage range of the DAC. The current flowing through the ladder termination resistance, which is 2 kΩ for the HI-562A model, generates an error voltage at the output of the DAC. This error voltage is compared with 1/z LSB by a comparator. When the error voltage remains within ±1/z LSB, the Q outputs of the comparators are both low, which halts the counter and provides a data ready signal to indicate that the digital output is accurate. If the error surpasses the ±1/z LSB range, the counter is activated and moves in either an upward or downward direction based on the polarity of the error voltage. The digital output only changes state when there is a significant alteration in the analog input. When observing a slowly varying input, it is crucial to read the digital output only after a change has occurred. The data ready signal can be utilized to trigger a flip-flop to indicate the condition and reset it after the readout. A primary drawback of the tracking ADC is the time required to initially acquire a signal; for a 12-bit ADC, this can take up to 4096 clock periods. The input signal typically needs to be filtered to ensure that its rate of change does not exceed the tracking range of the ADC, which is 1 LSB per clock period.

The circuit described involves a tracking Analog-to-Digital Converter (ADC) that utilizes a span resistor to manage the analog input voltage, allowing for flexible selection of both input and output voltage ranges. The critical component in this setup is the comparator, which plays a significant role in maintaining the accuracy of the digital output by continuously monitoring the error voltage generated from the DAC's output. The ladder termination resistance, specifically the 2 kΩ used in the HI-562A, is integral in defining the current flow and subsequently the error voltage that is compared against the defined LSB.

When the error voltage remains within acceptable limits, the system achieves a stable state where the counter halts, and a data ready signal is generated. This signal is essential for synchronizing the digital output readout with the analog input changes, ensuring that the data is only captured when significant alterations occur. The use of a flip-flop to latch the data ready signal enhances the reliability of the readout process, allowing for a clear indication of the data's readiness for further processing.

In scenarios where the error voltage exceeds the predefined limits, the counter is enabled to correct the output by adjusting in the appropriate direction, thus ensuring that the digital representation of the analog input remains as accurate as possible. This feedback mechanism is crucial for applications requiring high precision, especially when dealing with slowly varying signals, where timing and accuracy of the readout become paramount.

The system's design must account for the inherent limitations of the tracking ADC, particularly the initial acquisition time, which can be substantial for higher resolution ADCs. Filtering the input signal is a necessary precaution to prevent rapid changes that could lead to inaccuracies in the digital output, thereby ensuring that the ADC operates within its optimal tracking range of 1 LSB per clock period. This careful consideration of input signal characteristics and ADC response time is vital for achieving reliable performance in precision measurement applications.The analog input is fed into the span resistor of a DAC. The analog input voltage range is selectable in the same way as the output voltage range of the DAC. The net current flow through the ladder termination resistance; i.e., 2 KO for HI-562A; produces an error voltage at the DAC output.

This error voltage is compared with 1/z LSB by a comparator. When the error voltage is within ±1/z LSB range, the Q output of the comparators are both low, which stops the counter and gives a data ready signal to indicate that the digital output is correct. Ifthe error exceeds the ±1/z LSB range, the counter is enabled and driven in an up or down direction depending on the polarity of the error voltage. The digital output changes state only when there is a significant change in the analog input. When monitoring a slowly varying input, it is necessary to read the digital output only after a change has taken place.

The data ready signal could be used to trigger a flip-flop to indicate the condition and reset it after readout. The main disadvantage of the tracking ADC is the time reqnired to initially acquire a signal; for a 12-bit ADC, it could be up to 4096 clock periods.

The input signal usually must be filtered so that its rate of change does not exceed the tracking range of the ADC-1 LSB per clock period.

The circuit described involves a tracking Analog-to-Digital Converter (ADC) that utilizes a span resistor to manage the analog input voltage, allowing for flexible selection of both input and output voltage ranges. The critical component in this setup is the comparator, which plays a significant role in maintaining the accuracy of the digital output by continuously monitoring the error voltage generated from the DAC's output. The ladder termination resistance, specifically the 2 kΩ used in the HI-562A, is integral in defining the current flow and subsequently the error voltage that is compared against the defined LSB.

When the error voltage remains within acceptable limits, the system achieves a stable state where the counter halts, and a data ready signal is generated. This signal is essential for synchronizing the digital output readout with the analog input changes, ensuring that the data is only captured when significant alterations occur. The use of a flip-flop to latch the data ready signal enhances the reliability of the readout process, allowing for a clear indication of the data's readiness for further processing.

In scenarios where the error voltage exceeds the predefined limits, the counter is enabled to correct the output by adjusting in the appropriate direction, thus ensuring that the digital representation of the analog input remains as accurate as possible. This feedback mechanism is crucial for applications requiring high precision, especially when dealing with slowly varying signals, where timing and accuracy of the readout become paramount.

The system's design must account for the inherent limitations of the tracking ADC, particularly the initial acquisition time, which can be substantial for higher resolution ADCs. Filtering the input signal is a necessary precaution to prevent rapid changes that could lead to inaccuracies in the digital output, thereby ensuring that the ADC operates within its optimal tracking range of 1 LSB per clock period. This careful consideration of input signal characteristics and ADC response time is vital for achieving reliable performance in precision measurement applications.The analog input is fed into the span resistor of a DAC. The analog input voltage range is selectable in the same way as the output voltage range of the DAC. The net current flow through the ladder termination resistance; i.e., 2 KO for HI-562A; produces an error voltage at the DAC output.

This error voltage is compared with 1/z LSB by a comparator. When the error voltage is within ±1/z LSB range, the Q output of the comparators are both low, which stops the counter and gives a data ready signal to indicate that the digital output is correct. Ifthe error exceeds the ±1/z LSB range, the counter is enabled and driven in an up or down direction depending on the polarity of the error voltage. The digital output changes state only when there is a significant change in the analog input. When monitoring a slowly varying input, it is necessary to read the digital output only after a change has taken place.

The data ready signal could be used to trigger a flip-flop to indicate the condition and reset it after readout. The main disadvantage of the tracking ADC is the time reqnired to initially acquire a signal; for a 12-bit ADC, it could be up to 4096 clock periods.

The input signal usually must be filtered so that its rate of change does not exceed the tracking range of the ADC-1 LSB per clock period.