Triangle-generator

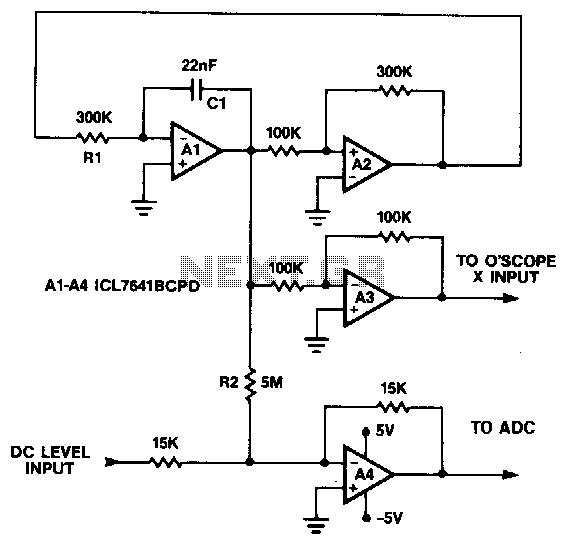

This circuit generates a symmetrical 10 mV peak-to-peak triangle waveform that is summed with a DC level and connected to the analog input for noise and DNL testing. The DC level input offsets the triangle waveform over the input range of the ADC. The 10 mV amplitude corresponds to an 8 LSB span for a 12-bit, 5 V full-scale ADC.

The circuit design incorporates a triangle waveform generator, which can be realized using an operational amplifier (op-amp) configured in an integrator and comparator configuration. The triangle waveform is characterized by its linear rise and fall times, providing a symmetrical output. The amplitude of the waveform is set to 10 mV peak-to-peak, which is critical for achieving the desired resolution in the subsequent analog-to-digital conversion process.

To offset the triangle waveform, a DC level is introduced via a voltage reference or a potentiometer, allowing for precise adjustment of the offset voltage. This summation occurs at the input stage of the ADC, ensuring that the triangle waveform is effectively centered within the ADC's input range. The use of a 12-bit ADC with a 5 V reference voltage results in a resolution of approximately 1.22 mV per LSB, which translates the 10 mV triangle waveform amplitude into an 8 LSB span. This configuration is essential for evaluating the noise performance and differential non-linearity (DNL) of the ADC under test.

The circuit should also include appropriate filtering and buffering stages to minimize noise and ensure signal integrity. A low-pass filter may be implemented to reduce high-frequency noise that could affect the triangle waveform's characteristics. Additionally, careful attention should be paid to the power supply decoupling and layout considerations to maintain the performance of the circuit during testing.

Overall, this circuit serves as a vital tool for testing the performance metrics of ADCs, particularly in assessing their noise characteristics and differential non-linearity across the specified input range.This circuit generates a symmetrical, 10-m V pk-pk triangle waveform which is summed with a de level and connected to the aid analog input for noise/DNL testing. The de level input offsets the triangle waveform over the input range of the ADC. The 10-mV amplitude amounts to an 8 LSB span for a 12-bit, 5-V, full-scale ADC.

The circuit design incorporates a triangle waveform generator, which can be realized using an operational amplifier (op-amp) configured in an integrator and comparator configuration. The triangle waveform is characterized by its linear rise and fall times, providing a symmetrical output. The amplitude of the waveform is set to 10 mV peak-to-peak, which is critical for achieving the desired resolution in the subsequent analog-to-digital conversion process.

To offset the triangle waveform, a DC level is introduced via a voltage reference or a potentiometer, allowing for precise adjustment of the offset voltage. This summation occurs at the input stage of the ADC, ensuring that the triangle waveform is effectively centered within the ADC's input range. The use of a 12-bit ADC with a 5 V reference voltage results in a resolution of approximately 1.22 mV per LSB, which translates the 10 mV triangle waveform amplitude into an 8 LSB span. This configuration is essential for evaluating the noise performance and differential non-linearity (DNL) of the ADC under test.

The circuit should also include appropriate filtering and buffering stages to minimize noise and ensure signal integrity. A low-pass filter may be implemented to reduce high-frequency noise that could affect the triangle waveform's characteristics. Additionally, careful attention should be paid to the power supply decoupling and layout considerations to maintain the performance of the circuit during testing.

Overall, this circuit serves as a vital tool for testing the performance metrics of ADCs, particularly in assessing their noise characteristics and differential non-linearity across the specified input range.This circuit generates a symmetrical, 10-m V pk-pk triangle waveform which is summed with a de level and connected to the aid analog input for noise/DNL testing. The de level input offsets the triangle waveform over the input range of the ADC. The 10-mV amplitude amounts to an 8 LSB span for a 12-bit, 5-V, full-scale ADC.