TTL oscillator

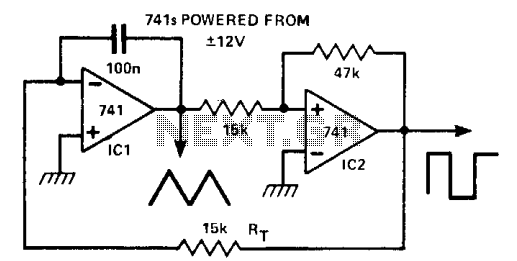

TTL inverter stages, U1 and U2, are cross-connected with a crystal Y1. A resistor in each stage biases the normally digital gates into a region where they operate as amplifiers. Inverter stage U3 is used as a buffer.

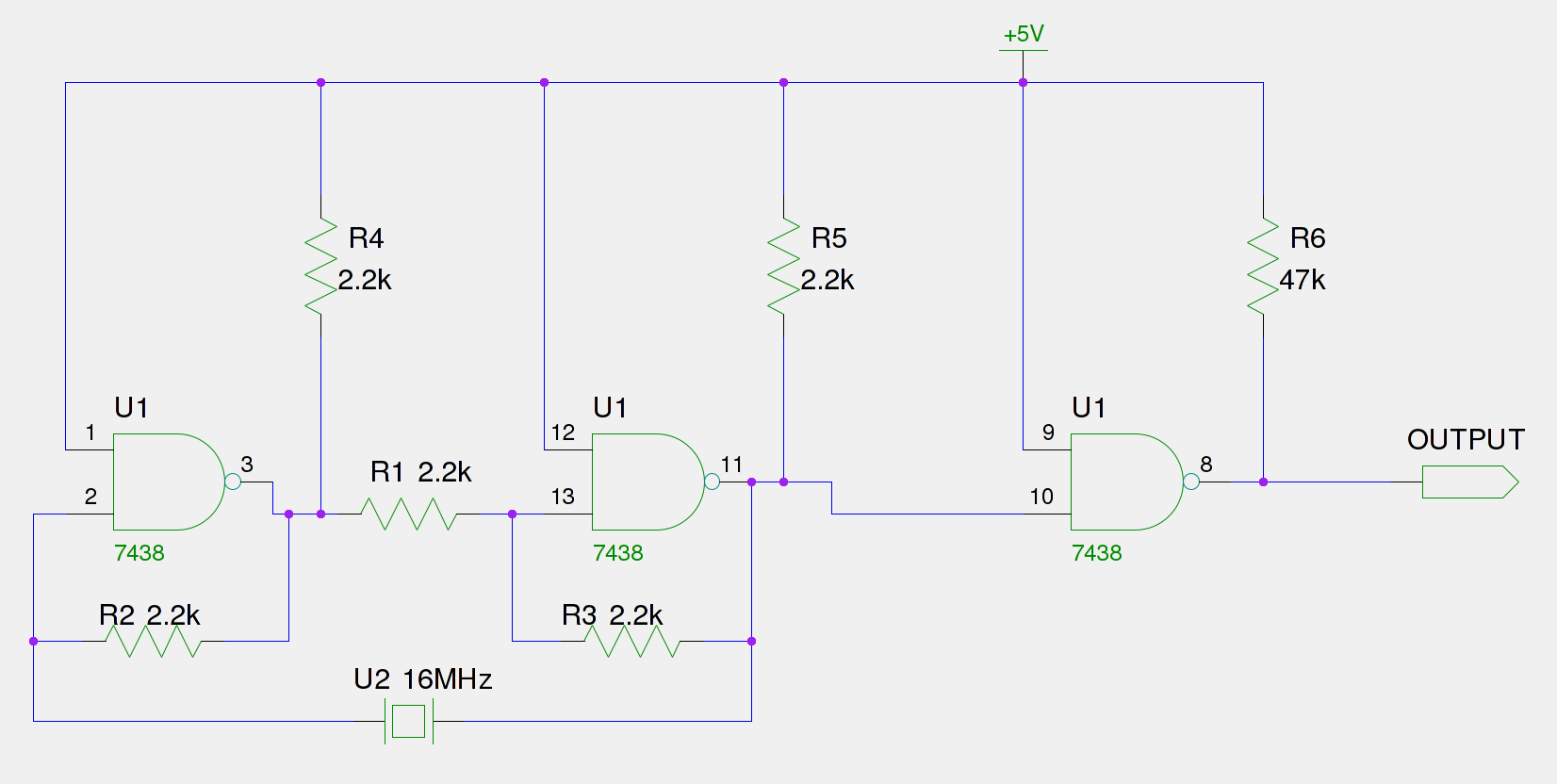

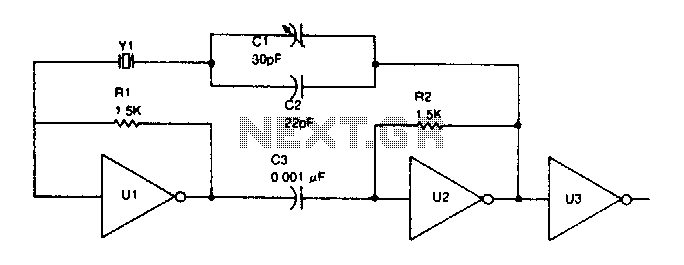

The circuit consists of two TTL inverter stages, U1 and U2, which are interconnected with a crystal oscillator component, Y1. The connection of the inverter stages through the crystal allows for the generation of a stable oscillation frequency, which is essential for various timing and clock applications in digital circuits. Each inverter stage incorporates a biasing resistor that modifies the operating point of the digital gates, enabling them to function in an analog region. This alteration allows the inverters to amplify weak signals, making them suitable for applications requiring signal conditioning.

The third inverter stage, U3, is designated as a buffer. Buffers are critical in digital circuits as they provide isolation between different circuit sections and prevent loading effects that can degrade signal integrity. The buffer stage ensures that the output from the previous stages can drive subsequent circuitry without significant signal loss or distortion. The use of a buffer also enhances the overall stability of the circuit, allowing it to maintain performance under varying load conditions.

In summary, this circuit design effectively utilizes TTL inverter stages to create a crystal-controlled oscillator while employing biasing resistors to enable amplification. The addition of a buffer stage further improves the circuit's performance by ensuring robust signal transmission. This configuration is beneficial in applications where precise timing and signal integrity are paramount.TTL inverter stages, Ul and U2, are cross-connected with a crystal Yl. A resistor in each stage biases the normally digital gates into a region where they operate as amplifiers Inverter stage U3 is used as a buffer. 🔗 External reference

The circuit consists of two TTL inverter stages, U1 and U2, which are interconnected with a crystal oscillator component, Y1. The connection of the inverter stages through the crystal allows for the generation of a stable oscillation frequency, which is essential for various timing and clock applications in digital circuits. Each inverter stage incorporates a biasing resistor that modifies the operating point of the digital gates, enabling them to function in an analog region. This alteration allows the inverters to amplify weak signals, making them suitable for applications requiring signal conditioning.

The third inverter stage, U3, is designated as a buffer. Buffers are critical in digital circuits as they provide isolation between different circuit sections and prevent loading effects that can degrade signal integrity. The buffer stage ensures that the output from the previous stages can drive subsequent circuitry without significant signal loss or distortion. The use of a buffer also enhances the overall stability of the circuit, allowing it to maintain performance under varying load conditions.

In summary, this circuit design effectively utilizes TTL inverter stages to create a crystal-controlled oscillator while employing biasing resistors to enable amplification. The addition of a buffer stage further improves the circuit's performance by ensuring robust signal transmission. This configuration is beneficial in applications where precise timing and signal integrity are paramount.TTL inverter stages, Ul and U2, are cross-connected with a crystal Yl. A resistor in each stage biases the normally digital gates into a region where they operate as amplifiers Inverter stage U3 is used as a buffer. 🔗 External reference