Voltage Multiplier

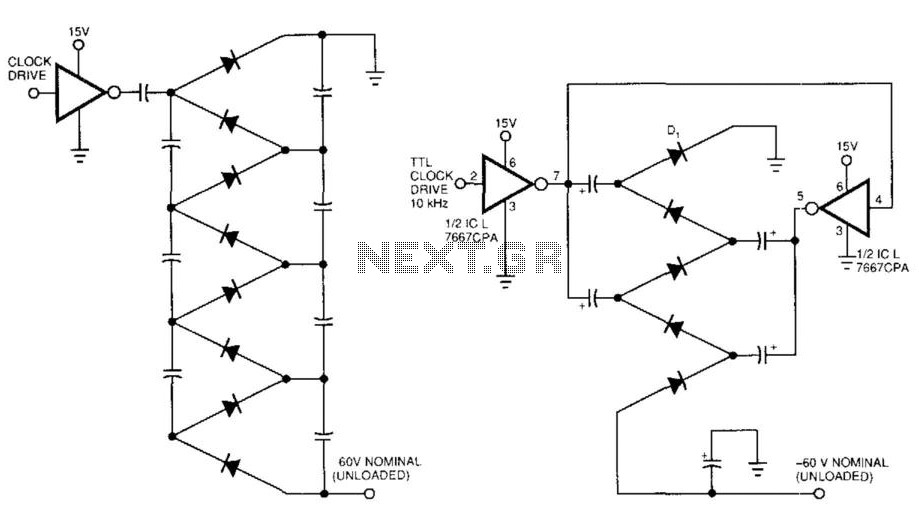

Figure 99-1(a)'s circuit exhibits a high output impedance due to the small effective capacitance of the series-connected capacitors, resulting in considerable voltage loss from the diode drops. This circuit requires two diodes and two capacitors to generate a DC output voltage approximately equal to multiple times the rail voltage. Conversely, Figure 99-1(b)'s circuit achieves more effective multiplication with fewer diodes and capacitors. The parallel arrangement of the capacitors allows for the use of smaller capacitors compared to those required in Figure 99-1(a). Alternatively, if the same capacitor values as in Figure 99-1(a) are used, the output impedance will be lower. In Figure 99-1(a), the clock source drives only one of the two strings of capacitors, while in Figure 99-1(b), the clock drives both strings in opposite phases, effectively doubling the voltage per stage of the two diodes. A final diode is required to extract the DC output voltage since both strings of capacitors now carry the AC input voltage waveform. The ICL7667 dual-FET driver accepts a TTL drive swing and provides a low-impedance push-pull drive to the diode string. This low impedance is particularly advantageous when utilizing a long string to elevate the output voltage to over 100 V, starting from a low rail voltage.

The circuit represented in Figure 99-1(a) demonstrates a high output impedance primarily due to the small effective capacitance of the series-connected capacitors. The design necessitates two diodes and two capacitors to achieve a DC output voltage that is a multiple of the rail voltage. However, this configuration suffers from significant voltage losses attributed to the forward voltage drops across the diodes.

In contrast, Figure 99-1(b) offers a more efficient approach by employing a parallel arrangement of capacitors, which allows for the utilization of smaller capacitors than those required in the series configuration of Figure 99-1(a). This parallel setup not only simplifies the component requirements but also reduces the output impedance when the same capacitor values are employed as in the previous design.

The operational dynamics of the clock source further differentiate the two circuits. In Figure 99-1(a), the clock source drives only one of the two capacitor strings, limiting the voltage multiplication effect. However, in Figure 99-1(b), the clock drives both capacitor strings in opposite phases, effectively doubling the voltage output per stage of the two diodes. This phase opposition is crucial as it enhances the overall efficiency of the voltage multiplication process.

To extract the DC output voltage, a final diode is included in the circuit, as both capacitor strings simultaneously carry the AC input voltage waveform. The inclusion of the ICL7667 dual-FET driver is significant as it accepts a TTL drive swing, providing a robust low-impedance push-pull drive to the diode string. This low impedance is particularly beneficial when leveraging a long string of diodes to elevate the output voltage beyond 100 V, starting from a low rail voltage, thereby making the circuit suitable for high-voltage applications. Figure 99-l(a)"s circuit exhibits a high-output impedance as a result of the small effective capacitance of the series-c onnected capacitors, and it exhibits considerable voltage loss due to all of the diode drops. Further, this circuit requires 2 diodes and 2 capacitors to produce a dc output voltage approximately times the rail voltage. Figure 99-1 (b)"s circuit multiplies more effectively using fewer diodes and capacitors. The parallel arrangement of the capacitors lets you use smaller capacitors than those required in Fig.

99-1(a). Alternatively, when using the same capacitor values of Fig. 99-1 (a), the output impedance will be lower. Whereas the clock source directly drives only one of the two strings of capacitors in Fig. 99-1(a), Fig. 99-l(b)"s clock drives both strings with opposite phases. This drive scheme doubles the voltage per stage of two diodes. A final diode is necessary to pick off the dc output voltage because both strings of capacitors now carry the - p ac input-voltage waveform. The ICL7667 dual-FET driver accepts a TTL drive swing and provides a low-impedance push-pull drive to the diode string.

This low impedance is particularly helpful when using a long string to raise output voltage to more than 100 V, starting from a low rail voltage. 🔗 External reference

The circuit represented in Figure 99-1(a) demonstrates a high output impedance primarily due to the small effective capacitance of the series-connected capacitors. The design necessitates two diodes and two capacitors to achieve a DC output voltage that is a multiple of the rail voltage. However, this configuration suffers from significant voltage losses attributed to the forward voltage drops across the diodes.

In contrast, Figure 99-1(b) offers a more efficient approach by employing a parallel arrangement of capacitors, which allows for the utilization of smaller capacitors than those required in the series configuration of Figure 99-1(a). This parallel setup not only simplifies the component requirements but also reduces the output impedance when the same capacitor values are employed as in the previous design.

The operational dynamics of the clock source further differentiate the two circuits. In Figure 99-1(a), the clock source drives only one of the two capacitor strings, limiting the voltage multiplication effect. However, in Figure 99-1(b), the clock drives both capacitor strings in opposite phases, effectively doubling the voltage output per stage of the two diodes. This phase opposition is crucial as it enhances the overall efficiency of the voltage multiplication process.

To extract the DC output voltage, a final diode is included in the circuit, as both capacitor strings simultaneously carry the AC input voltage waveform. The inclusion of the ICL7667 dual-FET driver is significant as it accepts a TTL drive swing, providing a robust low-impedance push-pull drive to the diode string. This low impedance is particularly beneficial when leveraging a long string of diodes to elevate the output voltage beyond 100 V, starting from a low rail voltage, thereby making the circuit suitable for high-voltage applications. Figure 99-l(a)"s circuit exhibits a high-output impedance as a result of the small effective capacitance of the series-c onnected capacitors, and it exhibits considerable voltage loss due to all of the diode drops. Further, this circuit requires 2 diodes and 2 capacitors to produce a dc output voltage approximately times the rail voltage. Figure 99-1 (b)"s circuit multiplies more effectively using fewer diodes and capacitors. The parallel arrangement of the capacitors lets you use smaller capacitors than those required in Fig.

99-1(a). Alternatively, when using the same capacitor values of Fig. 99-1 (a), the output impedance will be lower. Whereas the clock source directly drives only one of the two strings of capacitors in Fig. 99-1(a), Fig. 99-l(b)"s clock drives both strings with opposite phases. This drive scheme doubles the voltage per stage of two diodes. A final diode is necessary to pick off the dc output voltage because both strings of capacitors now carry the - p ac input-voltage waveform. The ICL7667 dual-FET driver accepts a TTL drive swing and provides a low-impedance push-pull drive to the diode string.

This low impedance is particularly helpful when using a long string to raise output voltage to more than 100 V, starting from a low rail voltage. 🔗 External reference