Wide Frequency Range 555 VCO

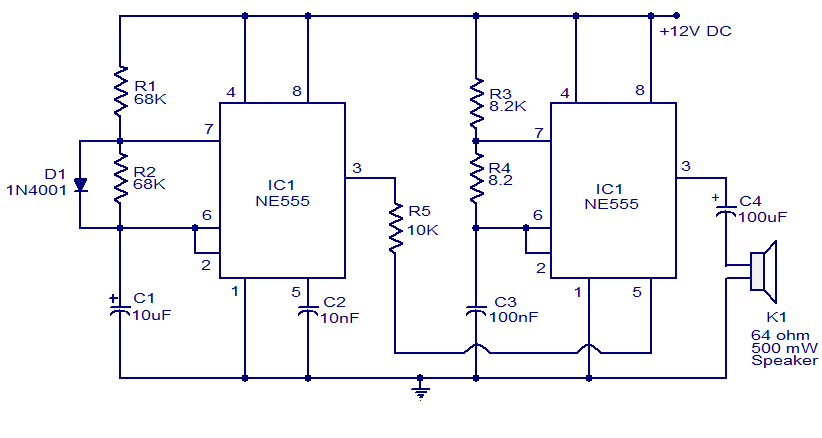

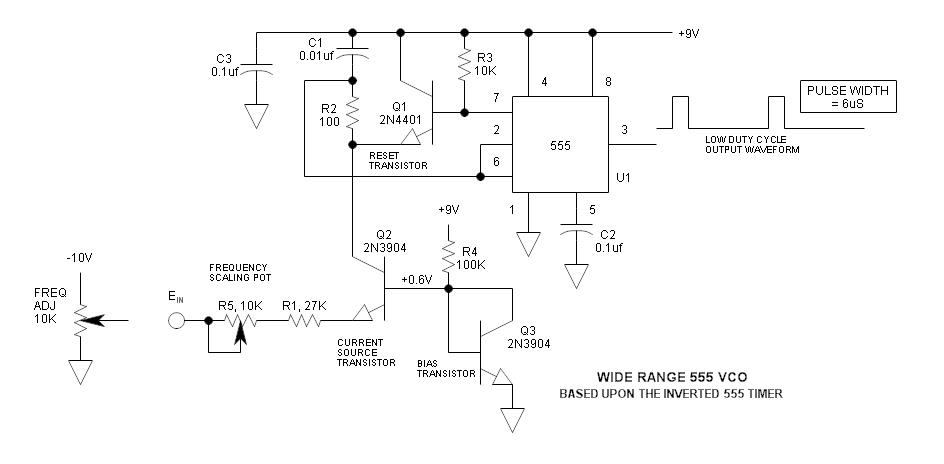

The frequency of the 555 timer can be adjusted by changing the voltage at pin 5. However, the range and linearity of this adjustment are quite limited. This can be significantly improved by using an inverted 555 timer circuit. In this configuration, Q2 is connected in a common base arrangement. In this mode, the collector current is determined by the emitter current, independent of the collector voltage, allowing for a linear charging function on capacitor C1. The emitter must be powered by a negative supply voltage. The frequency is scaled such that 10V corresponds to 10kHz through resistor R5, with a frequency range of 180Hz to 10kHz. Q3 is configured as a self-biasing transistor, where the base is connected to the collector and receives bias current through resistor R4. The voltage drop across Q3 is 0.6V. Initially, a 1N4148 diode was used, which had a voltage drop of 0.45V, introducing too much offset to the emitter of Q1. Ideally, the voltage drop across Q3 should match the base-emitter voltage (Vbe) of Q2. This configuration is a compromise, as they are only matched when the emitter current (Ie) is calculated as (9V - 0.6V) / R4 = 84µA. The emitter current can vary between approximately 3µA to 303µA. The lowest offset would occur with both transistors matched and R4 increased to 3MΩ; in this scenario, the hFE at 3µA must be greater than 100. This is theoretically feasible but would necessitate a different selection of transistors, which was not tested. Q1 is a 2N4401, differing from the 2N3904 in that its current gain (hFE) is optimized for higher currents. The reset current needs to be high due to the low duty cycle of the timer. Linearity is maintained over two orders of magnitude. Although not perfect, the circuit demonstrates its performance characteristics. The error at the low end is attributed to input offset voltage that cannot be perfectly nullified by the voltage drop across Q3, while the non-linearity at the high end is due to the finite reset time of the 555 timer, which is approximately 6% at 10kHz.

The described circuit utilizes the 555 timer in an inverted configuration to enhance frequency modulation capabilities. The inclusion of Q2 in a common base configuration allows for improved linearity in the charging process of capacitor C1. The choice of a negative supply voltage for the emitter is crucial, as it enables the circuit to maintain functionality across the specified frequency range. The scaling of frequency via R5 is a critical design aspect, ensuring that the output frequency remains within the desired parameters for practical applications.

The self-biasing arrangement of Q3 is an innovative approach that simplifies biasing requirements while maintaining stable operation. The calculated emitter current and the relationship between the resistances and voltage drops are fundamental to achieving the desired performance. The use of the 2N4401 transistor is particularly noteworthy, as it offers a higher current gain at elevated current levels, making it suitable for applications requiring robust performance.

The circuit's performance is characterized by its linearity and the potential for minimal offset errors, although practical limitations exist due to component tolerances and the inherent characteristics of the 555 timer. The careful selection of components, including the resistor values and transistor types, plays a significant role in optimizing the overall circuit behavior. This design exemplifies the balance between theoretical ideals and practical engineering considerations in electronic circuit design.The 555 frequency can be varied via adjusting the voltage at pin 5. However, the range and linearity of frequency adjustment is very limited. This is a way to greatly improve performance using the inverted 555 timer circuit that was previously posted. Q2 is connected in the common base configuration. In this mode of operation, the collector curren t is a function of emitter current regardless of the collector voltage. In this way, it can perform a linear charge function upon C1. The emitter must be driven from a negative supply voltage. Frequency is scaled to 10V = 10kHZ via R5. Frequency range in this set-up is 180 to 10kHZ. Q3 is wired as a self-biasing transistor by connecting the base to the collector and feeding it a bias current via R4. Voltage drop is 0. 6V. Originally, I had a 1N4148 diode and its voltage drop was 0. 45V that added too much offset to the emitter of Q1. Ideally, the voltage drop across Q3 should equal Vbe of Q2. This is a compromise because they are matched only under the condition of Ie = (9V 0. 6V) /R4 = 84uA. The emitter current varies from about 3 to 303uA. Lowest low end offset would occur with both transistors matched and R4 increased to 3M ”in that case, the hFE @ 3uA must >100 ”this looks practical, but would require a different transistor selection ”I did not experiment with this option.

Q1 is a 2N4401. It varies from the 2N3904 in that its current gain (hFE) is optimized at a higher current. The reset current must be high due to its low duty cycle. Linearity is shown over two orders of magnitude. While not perfect, it shows how the circuit performs. The error on the low end is caused by input offset voltage that is not perfectly nulled via the voltage drop of Q3. On the high end, non-linearity is caused by the finite reset time of the 555 that runs about 6% @ 10kHZ.

🔗 External reference

The described circuit utilizes the 555 timer in an inverted configuration to enhance frequency modulation capabilities. The inclusion of Q2 in a common base configuration allows for improved linearity in the charging process of capacitor C1. The choice of a negative supply voltage for the emitter is crucial, as it enables the circuit to maintain functionality across the specified frequency range. The scaling of frequency via R5 is a critical design aspect, ensuring that the output frequency remains within the desired parameters for practical applications.

The self-biasing arrangement of Q3 is an innovative approach that simplifies biasing requirements while maintaining stable operation. The calculated emitter current and the relationship between the resistances and voltage drops are fundamental to achieving the desired performance. The use of the 2N4401 transistor is particularly noteworthy, as it offers a higher current gain at elevated current levels, making it suitable for applications requiring robust performance.

The circuit's performance is characterized by its linearity and the potential for minimal offset errors, although practical limitations exist due to component tolerances and the inherent characteristics of the 555 timer. The careful selection of components, including the resistor values and transistor types, plays a significant role in optimizing the overall circuit behavior. This design exemplifies the balance between theoretical ideals and practical engineering considerations in electronic circuit design.The 555 frequency can be varied via adjusting the voltage at pin 5. However, the range and linearity of frequency adjustment is very limited. This is a way to greatly improve performance using the inverted 555 timer circuit that was previously posted. Q2 is connected in the common base configuration. In this mode of operation, the collector curren t is a function of emitter current regardless of the collector voltage. In this way, it can perform a linear charge function upon C1. The emitter must be driven from a negative supply voltage. Frequency is scaled to 10V = 10kHZ via R5. Frequency range in this set-up is 180 to 10kHZ. Q3 is wired as a self-biasing transistor by connecting the base to the collector and feeding it a bias current via R4. Voltage drop is 0. 6V. Originally, I had a 1N4148 diode and its voltage drop was 0. 45V that added too much offset to the emitter of Q1. Ideally, the voltage drop across Q3 should equal Vbe of Q2. This is a compromise because they are matched only under the condition of Ie = (9V 0. 6V) /R4 = 84uA. The emitter current varies from about 3 to 303uA. Lowest low end offset would occur with both transistors matched and R4 increased to 3M ”in that case, the hFE @ 3uA must >100 ”this looks practical, but would require a different transistor selection ”I did not experiment with this option.

Q1 is a 2N4401. It varies from the 2N3904 in that its current gain (hFE) is optimized at a higher current. The reset current must be high due to its low duty cycle. Linearity is shown over two orders of magnitude. While not perfect, it shows how the circuit performs. The error on the low end is caused by input offset voltage that is not perfectly nulled via the voltage drop of Q3. On the high end, non-linearity is caused by the finite reset time of the 555 that runs about 6% @ 10kHZ.

🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713