Z-80 Bus Monitor/Debugger

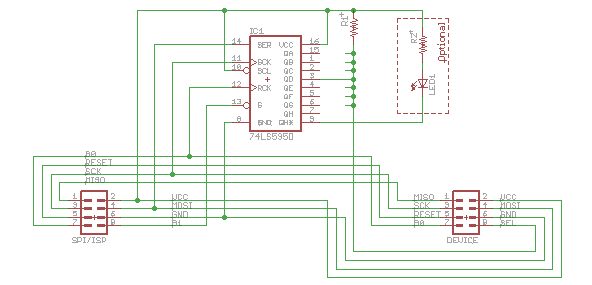

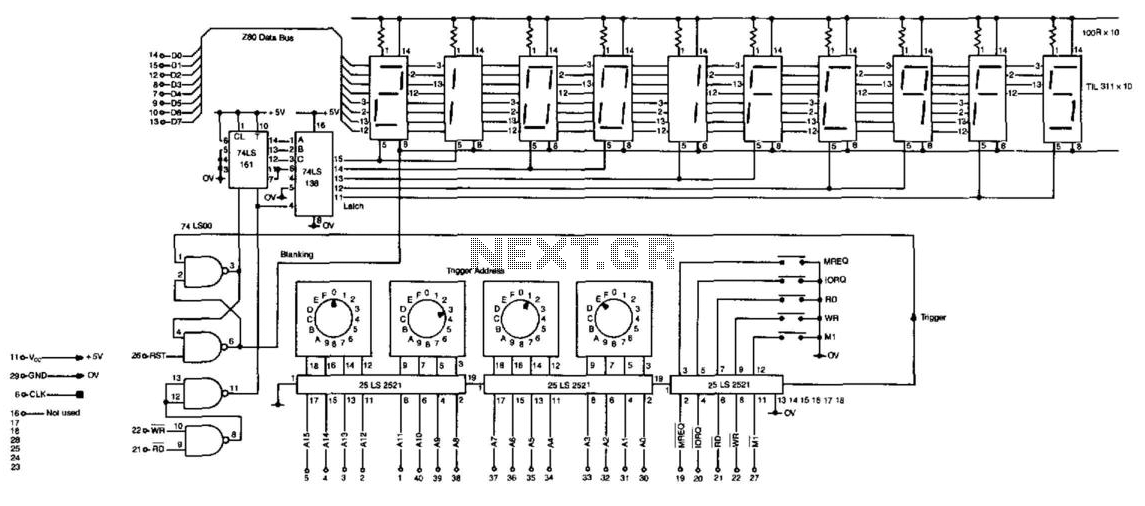

Getting microprocessor designs to function correctly is often challenging, particularly when both the software and hardware are unfamiliar. The typical method involves executing test routines that target memory and I/O without relying on their proper operation. However, any miswiring within the circuit can result in a confusing array of signals, potentially necessitating the use of a logic analyzer for interpretation. This straightforward circuit is designed to trace program execution and identify issues. While the circuit is configured for a Z-80 microprocessor, it can be easily modified for any 8-bit microprocessor or extended with additional circuitry for CPUs of varying bus widths. The circuit features a 5-byte hexadecimal display and comparator, which are connected to a 40-pin IC test clip. This test clip is placed over the microprocessor (in this instance, a Z-80), where it receives power and all necessary signals. The address bus and control lines are routed to the comparator, allowing a trigger condition to be set via switches. Following this trigger, the next five occurrences of either RD or WR will latch the data bus contents into the five hexadecimal displays sequentially. For instance, by selecting address 0000, performing a read operation, and resetting the CPU, the displays will reflect the first instruction fetch, its data, and any subsequent actions. Details such as stack writes and subroutine addresses are also captured. To trace longer segments of a program, the address switches can be adjusted to follow the execution path.

This circuit serves as a vital tool for debugging and verifying the functionality of microprocessor designs, particularly in the early stages of development when both hardware and software may be untested. The inclusion of a 5-byte hexadecimal display allows for real-time visualization of the data bus, which is crucial for understanding the behavior of the microprocessor during operation. The use of a comparator to set trigger conditions enhances the circuit's flexibility, enabling users to focus on specific events in the program execution.

The 40-pin IC test clip ensures a secure and reliable connection to the microprocessor, facilitating the acquisition of necessary signals without requiring extensive modifications to the existing hardware setup. This feature is particularly beneficial in prototyping environments where rapid iterations are common. By allowing the user to set trigger conditions, the circuit can be tailored to capture specific data transactions of interest, making it a versatile tool for a range of debugging scenarios.

Moreover, the adaptability of the circuit to various microprocessors and bus widths increases its utility across different platforms and applications. This capability is essential for engineers working with diverse microcontroller architectures, as it allows for consistent debugging methodologies regardless of the specific hardware being utilized.

In summary, this circuit not only simplifies the process of tracing program execution but also enhances the overall debugging experience by providing clear visibility into the operation of microprocessor designs. Its straightforward design, coupled with the ability to adapt to different architectures, makes it an indispensable resource for electronics engineers engaged in microprocessor development and testing. Getting microprocessor designs to work is notoriously difficult when both the software and hardware are new. The usual approach is to run test routines that address memory and I/O, but do not rely on their correct functioning. However, miswiring in any part of the circuit usually leads to a misleading jumble of signals that might require a logic analyzer to interpret.

This simple circuit will trace the program execution and help point to the problems. Although the circuit shows connections for a Z-80, the circuit can very easily be adapted for any 8-bit microprocessor or with additional circuitry for CPUs of any bus width. The circuit consists of a 5-byte hexadecimal display and comparator, which are wired to a 40-pin IC test clip.

The test clip sits over the microprocessor (in this case a Z-80), where it gets power and all the required signals. The address bus and control lines are fed to the comparator, where (by means of switches) a trigger condition can be set.

Following the trigger, the next 5 occurrences of either RD or WR will latch the contents of the data bus into the 5 hex displays, each in turn. For example, select address 0000 Ml Rd and reset the CPU. The displays will show the very first instruction fetch, followed by its data and any consequent action.

Even details, such as stack writes and subroutine addresses, are included. To trace longer portions of a program the address switches can be incremented to follow the execution path. 🔗 External reference

This circuit serves as a vital tool for debugging and verifying the functionality of microprocessor designs, particularly in the early stages of development when both hardware and software may be untested. The inclusion of a 5-byte hexadecimal display allows for real-time visualization of the data bus, which is crucial for understanding the behavior of the microprocessor during operation. The use of a comparator to set trigger conditions enhances the circuit's flexibility, enabling users to focus on specific events in the program execution.

The 40-pin IC test clip ensures a secure and reliable connection to the microprocessor, facilitating the acquisition of necessary signals without requiring extensive modifications to the existing hardware setup. This feature is particularly beneficial in prototyping environments where rapid iterations are common. By allowing the user to set trigger conditions, the circuit can be tailored to capture specific data transactions of interest, making it a versatile tool for a range of debugging scenarios.

Moreover, the adaptability of the circuit to various microprocessors and bus widths increases its utility across different platforms and applications. This capability is essential for engineers working with diverse microcontroller architectures, as it allows for consistent debugging methodologies regardless of the specific hardware being utilized.

In summary, this circuit not only simplifies the process of tracing program execution but also enhances the overall debugging experience by providing clear visibility into the operation of microprocessor designs. Its straightforward design, coupled with the ability to adapt to different architectures, makes it an indispensable resource for electronics engineers engaged in microprocessor development and testing. Getting microprocessor designs to work is notoriously difficult when both the software and hardware are new. The usual approach is to run test routines that address memory and I/O, but do not rely on their correct functioning. However, miswiring in any part of the circuit usually leads to a misleading jumble of signals that might require a logic analyzer to interpret.

This simple circuit will trace the program execution and help point to the problems. Although the circuit shows connections for a Z-80, the circuit can very easily be adapted for any 8-bit microprocessor or with additional circuitry for CPUs of any bus width. The circuit consists of a 5-byte hexadecimal display and comparator, which are wired to a 40-pin IC test clip.

The test clip sits over the microprocessor (in this case a Z-80), where it gets power and all the required signals. The address bus and control lines are fed to the comparator, where (by means of switches) a trigger condition can be set.

Following the trigger, the next 5 occurrences of either RD or WR will latch the contents of the data bus into the 5 hex displays, each in turn. For example, select address 0000 Ml Rd and reset the CPU. The displays will show the very first instruction fetch, followed by its data and any consequent action.

Even details, such as stack writes and subroutine addresses, are included. To trace longer portions of a program the address switches can be incremented to follow the execution path. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713