10Db-gain-amplifier

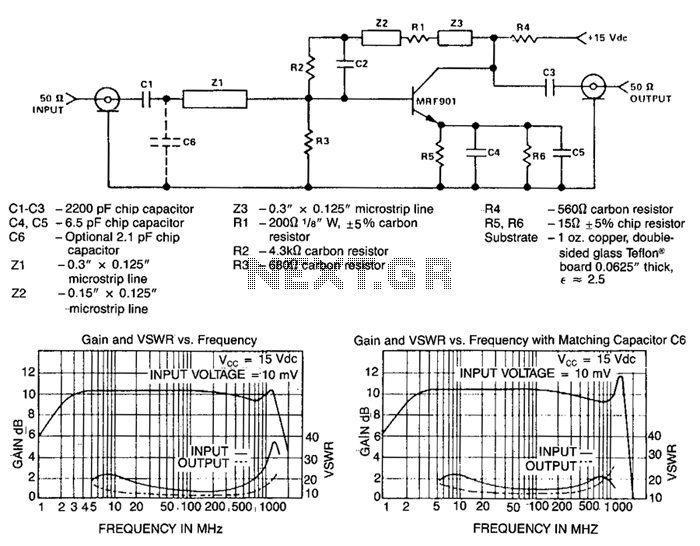

This circuit design is a Class A amplifier that utilizes both AC and DC feedback. The bias is stabilized at 15 mA of the collector current through the use of DC feedback from the collector. The AC feedback, which is directed from the collector to the base and in each of the partially bypassed emitter circuits, compensates for the increase in device gain as frequency decreases, resulting in a flat response across a maximum bandwidth. The amplifier achieves a nominal power gain of 10 dB from 3 MHz to 1.4 GHz. Additionally, with only a minimal matching network implemented at the amplifier input, the input Voltage Standing Wave Ratio (VSWR) remains below 2.5:1 up to approximately 1 GHz, while the output VSWR is maintained under 2:1. It should be noted that a slight degradation in gain flatness and output VSWR occurs with the addition of capacitor C6. A more complex network design could potentially optimize impedance matching while preserving gain flatness.

This Class A amplifier circuit is designed for high-frequency applications, leveraging both AC and DC feedback mechanisms to enhance performance. The stabilization of the bias current at 15 mA ensures consistent operation across varying conditions, which is critical for maintaining linearity and minimizing distortion. The use of DC feedback from the collector allows for effective stabilization of the collector current, which is essential for achieving the desired gain characteristics.

The AC feedback path, which connects the collector to the base, plays a vital role in flattening the gain response across the frequency spectrum. This feedback compensates for the natural tendency of transistors to exhibit increased gain at lower frequencies, thereby ensuring that the amplifier maintains a uniform response from 3 MHz to 1.4 GHz. The nominal power gain of 10 dB indicates that the amplifier is capable of providing significant amplification, making it suitable for various applications in RF and communication systems.

The input and output VSWR values are critical parameters in assessing the efficiency of the amplifier in terms of impedance matching. With an input VSWR of less than 2.5:1 up to 1 GHz, the circuit demonstrates good impedance matching, which minimizes reflection losses and maximizes power transfer. The output VSWR being under 2:1 further indicates that the amplifier can drive loads effectively without significant signal degradation.

The mention of capacitor C6 suggests that it is part of the feedback or bypass network. The observed degradation in gain flatness and output VSWR upon adding this component highlights the importance of careful component selection and network design in high-frequency amplifier circuits. A more intricate matching network could enhance performance further by improving impedance matching while maintaining the desired gain characteristics, thereby providing a more robust solution for high-frequency applications. Overall, this Class A amplifier design exemplifies effective use of feedback mechanisms to achieve stable and high-performance amplification across a broad frequency range.This circuit design is a class A amplifier employing both ac and de feedback. Bias is stabilized at 15 mA of the collector current using de feedback from the collector. The ac feedback, from collector to base, and in each of the partially bypassed emitter circuits, compensates for the increase in device gain with decreasing frequency, yielding a flat response over a maximum bandwidth. The amplifier shows a nominal 10-dB power gain from 3 MHz to 1.4 GHz. With only a minimum matching network used at the amplifier input, the input VSWR remains less than 2.5:1 to approximately 1 GHz, while the output VSWR stays under 2:1. Note that a slight degradation in gain flatness and output VSWR occurs with the addition of C6. A more elaborate network design would probably optimize impedance matching, while maintaining gain flatness.

This Class A amplifier circuit is designed for high-frequency applications, leveraging both AC and DC feedback mechanisms to enhance performance. The stabilization of the bias current at 15 mA ensures consistent operation across varying conditions, which is critical for maintaining linearity and minimizing distortion. The use of DC feedback from the collector allows for effective stabilization of the collector current, which is essential for achieving the desired gain characteristics.

The AC feedback path, which connects the collector to the base, plays a vital role in flattening the gain response across the frequency spectrum. This feedback compensates for the natural tendency of transistors to exhibit increased gain at lower frequencies, thereby ensuring that the amplifier maintains a uniform response from 3 MHz to 1.4 GHz. The nominal power gain of 10 dB indicates that the amplifier is capable of providing significant amplification, making it suitable for various applications in RF and communication systems.

The input and output VSWR values are critical parameters in assessing the efficiency of the amplifier in terms of impedance matching. With an input VSWR of less than 2.5:1 up to 1 GHz, the circuit demonstrates good impedance matching, which minimizes reflection losses and maximizes power transfer. The output VSWR being under 2:1 further indicates that the amplifier can drive loads effectively without significant signal degradation.

The mention of capacitor C6 suggests that it is part of the feedback or bypass network. The observed degradation in gain flatness and output VSWR upon adding this component highlights the importance of careful component selection and network design in high-frequency amplifier circuits. A more intricate matching network could enhance performance further by improving impedance matching while maintaining the desired gain characteristics, thereby providing a more robust solution for high-frequency applications. Overall, this Class A amplifier design exemplifies effective use of feedback mechanisms to achieve stable and high-performance amplification across a broad frequency range.This circuit design is a class A amplifier employing both ac and de feedback. Bias is stabilized at 15 mA of the collector current using de feedback from the collector. The ac feedback, from collector to base, and in each of the partially bypassed emitter circuits, compensates for the increase in device gain with decreasing frequency, yielding a flat response over a maximum bandwidth. The amplifier shows a nominal 10-dB power gain from 3 MHz to 1.4 GHz. With only a minimum matching network used at the amplifier input, the input VSWR remains less than 2.5:1 to approximately 1 GHz, while the output VSWR stays under 2:1. Note that a slight degradation in gain flatness and output VSWR occurs with the addition of C6. A more elaborate network design would probably optimize impedance matching, while maintaining gain flatness.