Adopt the two-dimentional bar-code scanner of DSP56F826 chip to introduce systematically

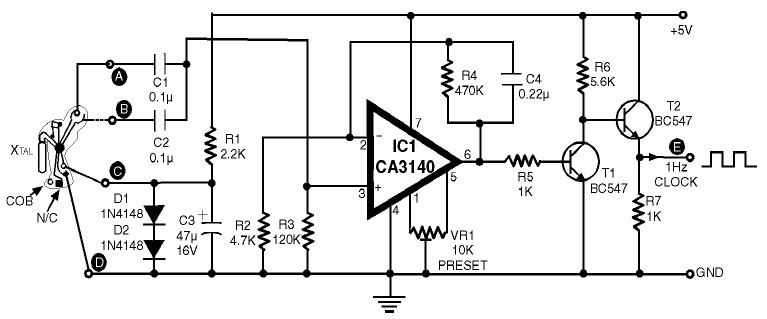

The system utilizes the DSP56F826 chip as the primary control module and incorporates a CMOS digital image sensor capable of capturing images with a resolution of 640 x 480 pixels. For applications requiring higher resolution, a chip supporting 1024 x 1024 pixels can be employed, albeit at a higher cost. The system exhibits high reliability, with a current bit error rate not exceeding 1 in 60,000, with expectations to improve this to 1 in 20 million. An RS-232 communication interface is used to upload two-dimensional barcode information to a computer for real-time display processing. The error correction level reaches eight grades, indicating strong correction capabilities. The two-dimensional barcode scanner system is illustrated in a block diagram. The CMOS image sensor acts as a photoelectric transducer, capturing the two-dimensional barcode image and outputting a digital signal. External SRAM is utilized to store this data before it is processed by the DSP, which performs image manipulation tasks including word segmentation, word recognition, and signal error correction. Upon completing the recognition of the two-dimensional barcode data, the I/O interface of the program control provides signals to halt the application, prompting the DSP to respond by stopping the application and entering the interrupt service routine. The decoded two-dimensional barcode data is transmitted from the I/O port to the computer via the SCI RS-232 interface and displayed on the screen. The software program and PDF417 codebook are stored in the FLASH memory of the DSP chip, while the dynamically captured two-dimensional barcode image data is stored in SRAM. The hardware circuit of the system consists of seven main components: the barcode image acquisition circuit, the DSP memory expansion circuit, the output interface circuit, the reset and clock circuit, the power control circuit, and the lighting control circuit. The OV7120 black-and-white image sensor serves as the core of this circuit, offering a resolution of 640 x 480 pixels and an imaging speed of 30 frames per second using a non-interlaced scanning mode, outputting digital signals. Although CCD sensors outperform CMOS sensors in terms of signal-to-noise ratio, sensitivity, and imaging quality, CMOS sensors are deemed more suitable for this system design due to their lower power consumption and cost-effectiveness. The barcode image acquisition circuit features digital outputs Y0-Y7 on the bus line, with HREF serving as the horizontal reference signal and VSYNC as the vertical synchronization signal. The PCLK signal provides the pixel clock. This circuit operates on a 5V DC power supply, provided by the power control circuit. While the chip operates at 5V, it interfaces with 3.3V for I/O connections, eliminating the need for level shifting. When the DSP receives the VSYNC signal, it indicates that the sensor chip is beginning to capture the first frame of barcode image data. Following the reception of the HREF signal, the chip commences data acquisition for the first line, requiring a PCLK signal each time to illuminate the pixel. As the DSP receives subsequent HREF signals, the chip continues to acquire data line by line until it has captured 640 lines, at which point it stops gathering data. Upon receiving the next VSYNC signal, the chip begins capturing data for the next frame. As depicted in the block diagram, the DSP56F826 chip serves as the core of the system. When the OV7120 image sensor is prepared to capture barcode image data, the DSP issues an initialization signal to control the SRAM address block, allowing the image sensor to begin data acquisition.

The system architecture integrates several key components and processes to ensure efficient operation and high-quality data capture for two-dimensional barcode scanning applications. The DSP56F826 chip plays a central role in processing the data captured by the OV7120 image sensor, which is designed to operate efficiently within the specified resolution and speed parameters. The RS-232 communication interface facilitates real-time data transfer to a computer, allowing for immediate processing and display of the captured barcode information. The use of external SRAM enhances the system's data handling capabilities, enabling the storage of image data prior to processing. The error correction mechanism is robust, ensuring high data integrity during transmission, which is critical for applications requiring reliable barcode scanning. The overall design emphasizes a balance between performance and cost, making it suitable for various applications in the field of barcode scanning and data acquisition.The system regards DSP56F826 chip as the key control module, uses the sensory chip of CMOS digital image, reachable 640* 480 picture element of definition that the picture is gathered. When needing the vision which carries on the high-resolution to be gathered, can use the chip cost will thereupon increase of 1024* 1024 picture element instead.

D ecipher reliability is high. The bit error rate got at present does not exceed 1/60, 000, and is updating, expect the bit error rate not to exceed 1/20 million. Adopt RS-232 communication interface, upload the two-dimentional bar code information obtained to the display processing of the computer in real time.

The grade of error correction reaches 8 grades, correction capability is strong. Two-dimentional bar-code scanner system block diagram such as Fig. 1 Shown. The sensory chip of CMOS picture is a photoelectric transition element, use and gather the two-dimentional bar code picture, direct output is a digital signal. Expanded SRAM by the outside and stored this data, and then send DSP, carry on image manipulation, one yard of word division, one yard of word recognition, signal error correction, etc.

, after the recognition of a series of two-dimentional bar code information is finished, serve the I/O interface of program control and provide and stop applying for signals, DSP responds to this and stops applying, enters the interrupt service routine. The two-dimentional bar code data after the decipher are conveyed from I/O mouth to the computer by SCI RS-232, and reveal on the screen.

Software program and PDF417 codebook are all stored in FLASH in DSP chip, and the two-dimentional bar code image data gathered dynamically is stored in SRAM. The system hardware circuit is mainly composed of seven parts: The bar code vision is gathered the circuit, circuit, expansion circuit of the memorizer of DSP top management, exporting the interface circuit, resetting with clock circuit, power controlling circuit, lighting controlling circuit.

This circuit regards sensory chip of OV7120 black-and-white image as the core, the definition of this chip reaches 640* 480 picture element, the imaging speed is frames per second 30, take the non-interlaced scanning mode, output it as the digital signal. The low power dissipation of this chip, the price is cheap, though CCD chip is superior to CMOS chip in such aspects as signal to noise ratio, degree of sensitivity, imaging quality, but in this system design, it is comparatively suitable to adopt CMOS chip.

The bar code picture is gathered the circuit Fig. 2 China, Y0-Y7 is the digital output of bus line, HREF is a horizontal reference signal, namely the scanning signal of walking; VSYN is a vertical sync signal, namely field synchronizing signal. PCLK exports for the picture element clock. This circuit uses 5V direct current, is offered by controlling circuit of the power. Though chip this use the intersection of 5V and working voltage, it offer the intersection of I/O and mouth of 3.

3V, so it can link with I/O voltage directly for DSP of 3. 3V, do not need level switch. When DSP receives VSYN signal, show the chip begins to gather the first frame bar code image data, receive HREF signal subsequently, the chip starts first lines of data acquisition, want a PCLK signal each time, gathers a signal that picture element is lighted with chip, as DSP receives the next HREF signal, the chip carries on second lines of data acquisition, until finishing gathering 640 lines of data, the chip stops gathering. When DSP receives the next VSYN signal, show that gathers the data of the next frame with chip. As shown in Fig. 1, this circuit regards DSP56F826 as the core. When the sensory chip of OV7120 picture plans to gather the image data of bar code, DSP sends out an initialization signal, control SRAM redistribution address block, the sensory chip of the picture begins to gather the image data of bar cod

🔗 External reference

The system architecture integrates several key components and processes to ensure efficient operation and high-quality data capture for two-dimensional barcode scanning applications. The DSP56F826 chip plays a central role in processing the data captured by the OV7120 image sensor, which is designed to operate efficiently within the specified resolution and speed parameters. The RS-232 communication interface facilitates real-time data transfer to a computer, allowing for immediate processing and display of the captured barcode information. The use of external SRAM enhances the system's data handling capabilities, enabling the storage of image data prior to processing. The error correction mechanism is robust, ensuring high data integrity during transmission, which is critical for applications requiring reliable barcode scanning. The overall design emphasizes a balance between performance and cost, making it suitable for various applications in the field of barcode scanning and data acquisition.The system regards DSP56F826 chip as the key control module, uses the sensory chip of CMOS digital image, reachable 640* 480 picture element of definition that the picture is gathered. When needing the vision which carries on the high-resolution to be gathered, can use the chip cost will thereupon increase of 1024* 1024 picture element instead.

D ecipher reliability is high. The bit error rate got at present does not exceed 1/60, 000, and is updating, expect the bit error rate not to exceed 1/20 million. Adopt RS-232 communication interface, upload the two-dimentional bar code information obtained to the display processing of the computer in real time.

The grade of error correction reaches 8 grades, correction capability is strong. Two-dimentional bar-code scanner system block diagram such as Fig. 1 Shown. The sensory chip of CMOS picture is a photoelectric transition element, use and gather the two-dimentional bar code picture, direct output is a digital signal. Expanded SRAM by the outside and stored this data, and then send DSP, carry on image manipulation, one yard of word division, one yard of word recognition, signal error correction, etc.

, after the recognition of a series of two-dimentional bar code information is finished, serve the I/O interface of program control and provide and stop applying for signals, DSP responds to this and stops applying, enters the interrupt service routine. The two-dimentional bar code data after the decipher are conveyed from I/O mouth to the computer by SCI RS-232, and reveal on the screen.

Software program and PDF417 codebook are all stored in FLASH in DSP chip, and the two-dimentional bar code image data gathered dynamically is stored in SRAM. The system hardware circuit is mainly composed of seven parts: The bar code vision is gathered the circuit, circuit, expansion circuit of the memorizer of DSP top management, exporting the interface circuit, resetting with clock circuit, power controlling circuit, lighting controlling circuit.

This circuit regards sensory chip of OV7120 black-and-white image as the core, the definition of this chip reaches 640* 480 picture element, the imaging speed is frames per second 30, take the non-interlaced scanning mode, output it as the digital signal. The low power dissipation of this chip, the price is cheap, though CCD chip is superior to CMOS chip in such aspects as signal to noise ratio, degree of sensitivity, imaging quality, but in this system design, it is comparatively suitable to adopt CMOS chip.

The bar code picture is gathered the circuit Fig. 2 China, Y0-Y7 is the digital output of bus line, HREF is a horizontal reference signal, namely the scanning signal of walking; VSYN is a vertical sync signal, namely field synchronizing signal. PCLK exports for the picture element clock. This circuit uses 5V direct current, is offered by controlling circuit of the power. Though chip this use the intersection of 5V and working voltage, it offer the intersection of I/O and mouth of 3.

3V, so it can link with I/O voltage directly for DSP of 3. 3V, do not need level switch. When DSP receives VSYN signal, show the chip begins to gather the first frame bar code image data, receive HREF signal subsequently, the chip starts first lines of data acquisition, want a PCLK signal each time, gathers a signal that picture element is lighted with chip, as DSP receives the next HREF signal, the chip carries on second lines of data acquisition, until finishing gathering 640 lines of data, the chip stops gathering. When DSP receives the next VSYN signal, show that gathers the data of the next frame with chip. As shown in Fig. 1, this circuit regards DSP56F826 as the core. When the sensory chip of OV7120 picture plans to gather the image data of bar code, DSP sends out an initialization signal, control SRAM redistribution address block, the sensory chip of the picture begins to gather the image data of bar cod

🔗 External reference