Debounced Counter Made From Off-The-Shelf Chips

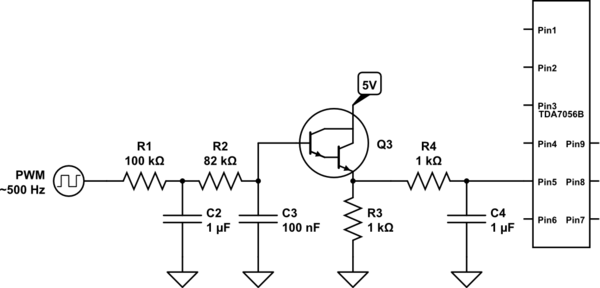

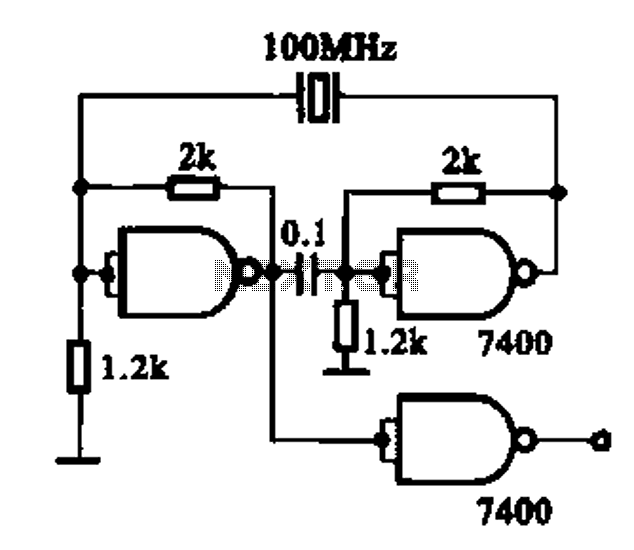

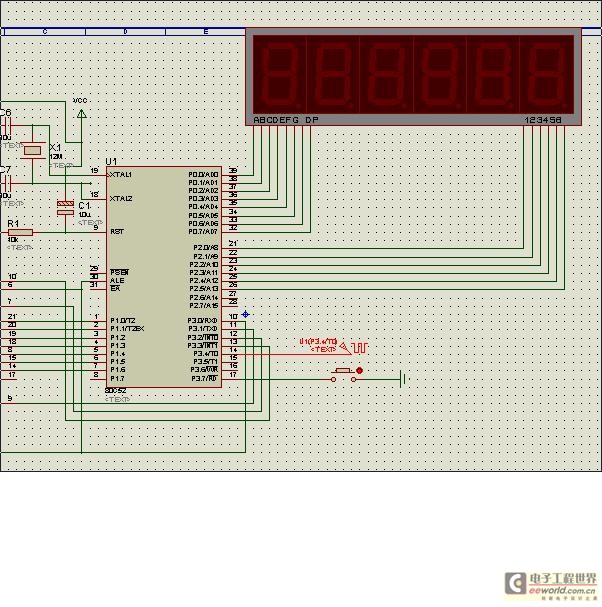

The true utility of the SR latch is evident during transitions of the input switch. Assume that the input switch is of the break-before-make type and starts in the up position. When the switch is up, the input values are low, low, high, high, resulting in a high output. As the switch is toggled, it first breaks the connection of the first input, changing it to high, low, high, high. These values assist in determining the output value. Even if the input switch signal experiences multiple bounces between low and high during the transition, the debounce output remains stable. This stability prevents the counter from incrementing erratically. Similarly, when the input switch starts in the down position and breaks contact while transitioning up, the output remains low. This behavior is desirable, explaining why a single-throw switch or pushbutton is ineffective. The circuit maintains a steady output state when only one input fluctuates. Pushbuttons and single-throw switches alter only one input, while double-throw switches provide additional information. By requiring two inputs to change states instead of just one, errors from either input can be disregarded at any moment. The timing for errors (bouncing) to settle is inconsequential, as the circuit can promptly change states again if needed. Software debouncing of pushbuttons relies on time as a secondary input, assuming a specific interval for the switch to stabilize before further input can be reliably accepted. This approach limits the maximum switching rate and remains susceptible to prolonged bounces. In the previous examples, it was assumed that the switch was of the break-before-make type. If the switch is of the make-before-break type, it will output two low values into the SR latch. A low input into a two-input NAND gate always results in a high output, irrespective of the other input value. Consequently, the prior state of the SR latch is irrelevant; the make-before-break switch will consistently yield a high output during input transitions. This behavior is undesirable when toggling from the down position, as bouncing will cause the input to the counter to fluctuate between low and high, leading to additional counts. Therefore, the switch must be a break-before-make double-throw type, not make-before-break. This requirement limits the circuit's applicability. However, in a microcontroller, a more complex algorithm can be implemented to accommodate either type of double-throw switch. Additionally, if a break-before-make switch is in the center position (neither up nor down) during power-up, the output state must be considered. From prior analysis of the up and down transition states, the SR latch will remain stable in its previous output state. If the individual NAND gate outputs power up as either high, low or low, high, they will remain stable (as these states correspond to the analyzed up/down transitions). However, if the individual NAND gate outputs initially power up as high, high or low, low, these values will feed into the center inputs of the SR latch circuit. Theoretically, this could cause the SR latch to oscillate between high and low outputs. In practice, slight variations in transistor characteristics will lead to one output triggering slightly earlier, resulting in a mismatch between the inputs and stabilizing the circuit. According to the first schematic in the book, after the input switch signal has been debounced and pulled up (if necessary), it is directed to a counter.

The SR latch is a fundamental bistable multivibrator circuit widely used in digital electronics for memory storage and state retention. The circuit typically consists of two cross-coupled NAND gates. The inputs to these gates are connected to the output of the other gate, creating a feedback loop that allows the circuit to maintain its last state until a new input is applied.

In practical applications, the SR latch can be used for debouncing mechanical switches, which are prone to noise and bouncing due to their physical contacts. The debounce circuit ensures that only clean transitions are registered, preventing erroneous counts in a connected counter or microcontroller. The design should include a double-throw switch that supports break-before-make operation, ensuring that only one input changes state at a time. This configuration allows the circuit to ignore transient states caused by bouncing.

When designing the debounce circuit, careful consideration must be given to the timing characteristics of the switch and the response time of the NAND gates. The propagation delay through the gates should be taken into account to ensure that the latch can respond quickly enough to valid input changes while filtering out noise.

In a microcontroller implementation, software debouncing can be employed alongside hardware solutions. The microcontroller can sample the input state at defined intervals, ignoring rapid changes within a specified debounce time. This hybrid approach can enhance reliability in environments with significant electrical noise.

In summary, the SR latch is an essential component in digital design, particularly for applications requiring stable state retention and noise immunity in switch transitions. The choice of switch type and circuit configuration directly influences the performance and reliability of the debounce mechanism.The real usefulness of the SR latch comes during input switch transitions. Let`s assume the input switch is a break-before-make and the switch starts in the up position. From the prior analysis, the inputs values when the switch is up are low, low, high, high, and the output is high. As the switch is toggled, it breaks the first input, changing it to high, low, high, high. Those values can be used to determine the output value. This means that even if the input switch signal bounces multiple times between low and high signals as it breaks the connection, the debounce output remains steady. Because the debounce output is steady, the counter doesn`t increment spuriously. Not surprisingly, the same steadiness occurs when the input switch starts in the down position and starts to break contact as it transitions up.

The output remains low. While this is exactly what we want, this also explains why a single-throw switch or pushbutton won`t work. This circuit keeps the output in a steady state when only one input is changing back and forth. Pushbuttons and single-throw switches only change one input. Double-throw switches provide more information. By requiring two inputs to change states, not just one, you can ignore all errors generated by either input at a given time.

You don`t care how long it takes for the errors (bouncing) to go away, but you`re ready to change states again right away if necessary. Software debouncing of pushbuttons relies on time as the second input. That is, the software assumes it takes a certain amount of time for the switch to settle down before more input can be reliably accepted.

This slows down the maximum switching rate and the software method is still vulnerable to long bounces. In the previous two examples, it was assumed that the switch is a break-before-make type of switch. Instead, if the switch is make-before-break type, the switch will output two low values into the SR latch.

A low input into a two-input NAND gates always results in a high output, regardless of the other input value into that gate. As such, it doesn`t matter what the prior state of the SR latch was, the make-before-break input switch will always result in the debounce circuit outputting high during input switch transitions.

This is undesirable behavior when toggling from the down position, as the bouncing will flip the input to the counter between low and high, causing extra counts. Therefore, the switch must be break-before-make double-throw, not make-before-break. Admittedly, this further reduces the occasions when the circuit may be useful to you. However, this is a limitation of using only two logic gates. In a microcontroller, you can write a slightly more complex algorithm that will work with either type of double-throw switch: There is one last pair of cases to consider that are classic for an SR latch.

If a break-before-make switch is in the center position (neither up nor down) during power up, what is the output From the prior analysis of the up and down transition states, we know that the SR latch will remain stable in its prior output state. If the individual NAND gate outputs happen to power up as either high, low or low, high , they will remain that way (because that`s identical to the already analyzed up/down transition states).

But what if the individual NAND gate outputs initially power up as high, high or low, low , feeding those value into the center inputs of the SR latch circuit Theoretically, the SR latch will repeatedly oscillate between a high output and a low output. In reality, the slight differences between transistors will cause one output to trip slightly sooner, causing the center inputs to no longer match each other, causing the circuit to stabilize.

According to the first schematic in the book, after the input switch signal is debounced and pulled-up (if necessary), it is fed into a counter. Because the first schematic does not p 🔗 External reference

The SR latch is a fundamental bistable multivibrator circuit widely used in digital electronics for memory storage and state retention. The circuit typically consists of two cross-coupled NAND gates. The inputs to these gates are connected to the output of the other gate, creating a feedback loop that allows the circuit to maintain its last state until a new input is applied.

In practical applications, the SR latch can be used for debouncing mechanical switches, which are prone to noise and bouncing due to their physical contacts. The debounce circuit ensures that only clean transitions are registered, preventing erroneous counts in a connected counter or microcontroller. The design should include a double-throw switch that supports break-before-make operation, ensuring that only one input changes state at a time. This configuration allows the circuit to ignore transient states caused by bouncing.

When designing the debounce circuit, careful consideration must be given to the timing characteristics of the switch and the response time of the NAND gates. The propagation delay through the gates should be taken into account to ensure that the latch can respond quickly enough to valid input changes while filtering out noise.

In a microcontroller implementation, software debouncing can be employed alongside hardware solutions. The microcontroller can sample the input state at defined intervals, ignoring rapid changes within a specified debounce time. This hybrid approach can enhance reliability in environments with significant electrical noise.

In summary, the SR latch is an essential component in digital design, particularly for applications requiring stable state retention and noise immunity in switch transitions. The choice of switch type and circuit configuration directly influences the performance and reliability of the debounce mechanism.The real usefulness of the SR latch comes during input switch transitions. Let`s assume the input switch is a break-before-make and the switch starts in the up position. From the prior analysis, the inputs values when the switch is up are low, low, high, high, and the output is high. As the switch is toggled, it breaks the first input, changing it to high, low, high, high. Those values can be used to determine the output value. This means that even if the input switch signal bounces multiple times between low and high signals as it breaks the connection, the debounce output remains steady. Because the debounce output is steady, the counter doesn`t increment spuriously. Not surprisingly, the same steadiness occurs when the input switch starts in the down position and starts to break contact as it transitions up.

The output remains low. While this is exactly what we want, this also explains why a single-throw switch or pushbutton won`t work. This circuit keeps the output in a steady state when only one input is changing back and forth. Pushbuttons and single-throw switches only change one input. Double-throw switches provide more information. By requiring two inputs to change states, not just one, you can ignore all errors generated by either input at a given time.

You don`t care how long it takes for the errors (bouncing) to go away, but you`re ready to change states again right away if necessary. Software debouncing of pushbuttons relies on time as the second input. That is, the software assumes it takes a certain amount of time for the switch to settle down before more input can be reliably accepted.

This slows down the maximum switching rate and the software method is still vulnerable to long bounces. In the previous two examples, it was assumed that the switch is a break-before-make type of switch. Instead, if the switch is make-before-break type, the switch will output two low values into the SR latch.

A low input into a two-input NAND gates always results in a high output, regardless of the other input value into that gate. As such, it doesn`t matter what the prior state of the SR latch was, the make-before-break input switch will always result in the debounce circuit outputting high during input switch transitions.

This is undesirable behavior when toggling from the down position, as the bouncing will flip the input to the counter between low and high, causing extra counts. Therefore, the switch must be break-before-make double-throw, not make-before-break. Admittedly, this further reduces the occasions when the circuit may be useful to you. However, this is a limitation of using only two logic gates. In a microcontroller, you can write a slightly more complex algorithm that will work with either type of double-throw switch: There is one last pair of cases to consider that are classic for an SR latch.

If a break-before-make switch is in the center position (neither up nor down) during power up, what is the output From the prior analysis of the up and down transition states, we know that the SR latch will remain stable in its prior output state. If the individual NAND gate outputs happen to power up as either high, low or low, high , they will remain that way (because that`s identical to the already analyzed up/down transition states).

But what if the individual NAND gate outputs initially power up as high, high or low, low , feeding those value into the center inputs of the SR latch circuit Theoretically, the SR latch will repeatedly oscillate between a high output and a low output. In reality, the slight differences between transistors will cause one output to trip slightly sooner, causing the center inputs to no longer match each other, causing the circuit to stabilize.

According to the first schematic in the book, after the input switch signal is debounced and pulled-up (if necessary), it is fed into a counter. Because the first schematic does not p 🔗 External reference