Digital-tach-dwell-meter

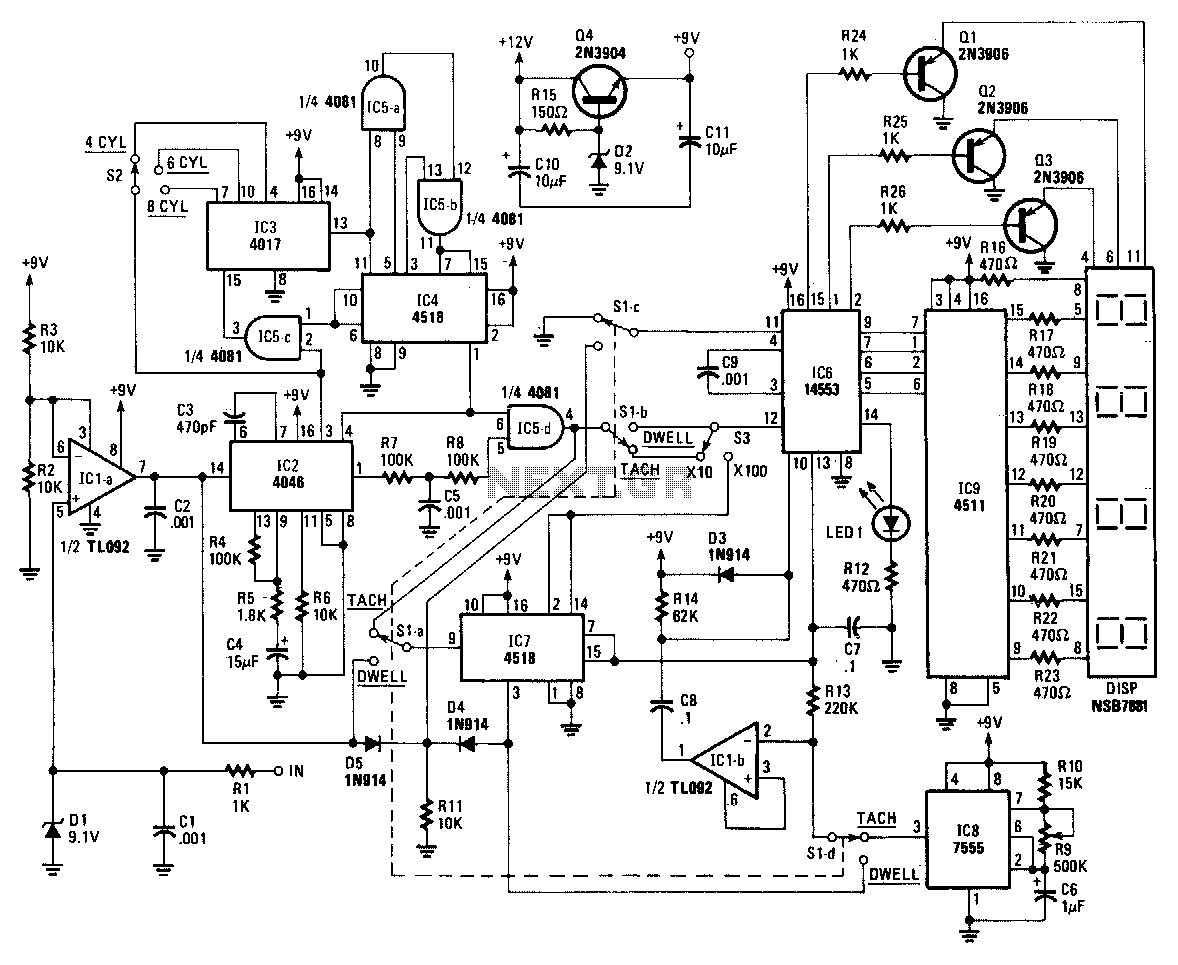

The core component of the circuit is ICZ, a 4046 micropower phase-locked loop (PLL). The incoming signals are processed through a buffer, IC1a, and its associated components before being fed into the PLL. The frequency of the incoming signal is multiplied by factors of 90, 60, or 45, depending on the position of the cylinder select switch, SZ. This switch selects the appropriate output from counters IC3 and IC4, which are configured to divide the output frequency of the PLL by the corresponding factors. The divided output is then sent back to the comparator within the PLL to maintain synchronization with the input signal. The phase pulses output from pin 4 of ICZ are directed through an AND gate, IC5d, which only allows signals to pass when the PLL is locked onto the input signal, thereby preventing erroneous readings. These signals are then routed to the input of IC6.

In tachometer mode, IC6 counts the number of pulses present at pin 12 during a timing interval generated by IC8 and the associated circuitry of IC1b. Due to the varying multiplication rates for different cylinder selections—90 for 4 cylinders, 60 for 6 cylinders, and 45 for 8 cylinders—the time interval remains constant at 1/3 of a second. This time interval can be adjusted using R9, a 500K potentiometer, which serves as the only adjustment in the circuit. In the high-tach (TACH 1 or x 100) range of 0-9990 RPM, the output from ICZ is routed through switches S1a and S3 to IC7, a divide-by-ten counter, effectively increasing the count range tenfold. In the low-tach (TACH 2 or x 10) range of 0-999 RPM, the counter is bypassed.

The 4046 PLL circuit serves as a robust solution for precise frequency multiplication and phase locking, essential for accurate tachometer readings in applications where engine speed monitoring is critical. The selection of multiplication factors based on cylinder count ensures that the system can accommodate a variety of engine configurations, making it versatile for automotive and industrial applications. The design leverages the PLL's inherent ability to maintain synchronization with the input frequency, which is critical for reliable operation. The inclusion of an AND gate further enhances the system's accuracy by filtering out noise and ensuring that only valid signals are counted. The adjustable timing interval allows for fine-tuning to adapt to specific operational requirements, enhancing the circuit's flexibility. Overall, this circuit design exemplifies a well-thought-out approach to frequency measurement and control, integrating multiple components to achieve a high level of performance.The heart of the circuit is ICZ, a 4046 micropower phase-locked loop (PLL). The incoming signals are fed to the PLL after being buffered by IC1a and its associated components. The frequency of the incoming signal is multiplied by either 90, 60, or 45, depending on the setting of the cylinder select switch, SZ. That switch selects the proper output from counters IC3 and IC4, which are set to divide the output frequency of the PLL by those amounts, and then send the divided output back to the comparator to the PLL to keep it locked on to the input signal.

The phase pulses output at pin 4 of ICZ, then go through an AND gate IC5d-which only passes the signals if the PLL is locked on to an input signal, preventing stray readingsand then to the input of IC6. When in the tach mode, IC6 counts the number of pulses present at pin 12, during the timing interval generated by IC8 and the associated circuitry of IClb. Because of the varied multiplication rate for the different cylinder selections-90, 60, and 45 for 4, 6, and 8 cylinders, respectively, the time interval is always constant at 113 of a second.

The time interval is adjusted with R9, a 500K! l potentiometer; it is the only adjustment in the circuit. In the high-tach (TACH 1 or x 100) range of 0-9990 rpm, the output oUCZ is routed by switches S1a and S3 through IC7, a divide-by-ten counter, which increases the count range tenfold. In the low-tach (TACH 2 or x 10) range of 0-999 rpm, the counter is bypassed.

In tachometer mode, IC6 counts the number of pulses present at pin 12 during a timing interval generated by IC8 and the associated circuitry of IC1b. Due to the varying multiplication rates for different cylinder selections—90 for 4 cylinders, 60 for 6 cylinders, and 45 for 8 cylinders—the time interval remains constant at 1/3 of a second. This time interval can be adjusted using R9, a 500K potentiometer, which serves as the only adjustment in the circuit. In the high-tach (TACH 1 or x 100) range of 0-9990 RPM, the output from ICZ is routed through switches S1a and S3 to IC7, a divide-by-ten counter, effectively increasing the count range tenfold. In the low-tach (TACH 2 or x 10) range of 0-999 RPM, the counter is bypassed.

The 4046 PLL circuit serves as a robust solution for precise frequency multiplication and phase locking, essential for accurate tachometer readings in applications where engine speed monitoring is critical. The selection of multiplication factors based on cylinder count ensures that the system can accommodate a variety of engine configurations, making it versatile for automotive and industrial applications. The design leverages the PLL's inherent ability to maintain synchronization with the input frequency, which is critical for reliable operation. The inclusion of an AND gate further enhances the system's accuracy by filtering out noise and ensuring that only valid signals are counted. The adjustable timing interval allows for fine-tuning to adapt to specific operational requirements, enhancing the circuit's flexibility. Overall, this circuit design exemplifies a well-thought-out approach to frequency measurement and control, integrating multiple components to achieve a high level of performance.The heart of the circuit is ICZ, a 4046 micropower phase-locked loop (PLL). The incoming signals are fed to the PLL after being buffered by IC1a and its associated components. The frequency of the incoming signal is multiplied by either 90, 60, or 45, depending on the setting of the cylinder select switch, SZ. That switch selects the proper output from counters IC3 and IC4, which are set to divide the output frequency of the PLL by those amounts, and then send the divided output back to the comparator to the PLL to keep it locked on to the input signal.

The phase pulses output at pin 4 of ICZ, then go through an AND gate IC5d-which only passes the signals if the PLL is locked on to an input signal, preventing stray readingsand then to the input of IC6. When in the tach mode, IC6 counts the number of pulses present at pin 12, during the timing interval generated by IC8 and the associated circuitry of IClb. Because of the varied multiplication rate for the different cylinder selections-90, 60, and 45 for 4, 6, and 8 cylinders, respectively, the time interval is always constant at 113 of a second.

The time interval is adjusted with R9, a 500K! l potentiometer; it is the only adjustment in the circuit. In the high-tach (TACH 1 or x 100) range of 0-9990 rpm, the output oUCZ is routed by switches S1a and S3 through IC7, a divide-by-ten counter, which increases the count range tenfold. In the low-tach (TACH 2 or x 10) range of 0-999 rpm, the counter is bypassed.