Digitally-programmable-attenuator

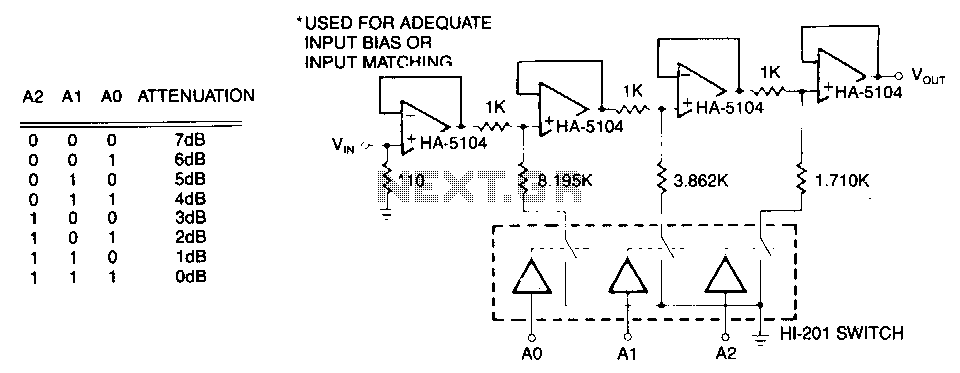

The first stage is a simple buffer used to isolate the signal source from the following attenuator stages. Each subsequent stage is preceded by a voltage divider formed by two resistors and a CMOS switch. When the CMOS switch for each stage is closed, the drive signal will be attenuated according to the basic voltage divider relationship at each stage. If a switch is open, nearly all of the signal strength will be passed to the next stage through a 1 kΩ resistor. The amplifiers serve as buffers for the divider networks and reduce the interaction between stages. Eight levels of attenuation are possible with the circuit as illustrated, but additional stages could be added. Each divider network must be closely matched to the resistor ratios shown; otherwise, the level of attenuation will not align with the levels in the logic chart.

The circuit described features a multi-stage attenuation system designed to provide precise control over signal levels while minimizing interaction between stages. The initial buffer stage is crucial for isolating the input signal from subsequent components, ensuring that the signal integrity is maintained throughout the attenuation process.

Each stage of attenuation is implemented using a voltage divider configuration, which consists of two resistors in series, along with a CMOS switch that determines whether the signal is passed through or blocked. When the CMOS switch is closed, the voltage divider effectively reduces the signal amplitude according to the established resistor values, adhering to the voltage divider formula \( V_{out} = V_{in} \times \frac{R2}{R1 + R2} \). This allows for precise control over the attenuation level at each stage.

In instances where the CMOS switch is open, the design incorporates a 1 kΩ resistor that allows the majority of the signal to bypass the divider network, ensuring that signal strength is preserved for subsequent stages. This feature is particularly useful in applications where certain attenuation levels are not required, allowing for flexibility in signal processing.

The amplifiers included in the circuit play a dual role: they act as buffers to prevent loading effects between the voltage divider networks and enhance the overall signal quality. By isolating the output of each divider from the input of the next, the amplifiers help to mitigate any potential interactions that could affect the performance of the circuit.

The design supports up to eight levels of attenuation, providing a versatile solution for various signal processing needs. However, the architecture is scalable, allowing for the addition of more stages if necessary. It is essential to maintain the specified resistor ratios within each divider network to ensure that the attenuation levels correspond accurately to the intended logic chart. Deviations from these ratios could lead to discrepancies in the expected output, potentially affecting the overall functionality of the circuit. Thus, careful design and component selection are critical for achieving the desired performance in this attenuation system.The first stage is a simple buffer used to isolate the signal source from the attenuator stages to follow. Each of the subsequent stages is preceded by a voltage divider formed by two resistors and CMOS switch.

Provided that the CMOS switch for each stage is closed, the drive signal will be attenuated according to the basic voltage divider relationship at each stage. In the event a switch is open, nearly all of the signal strength will be passed to the next stage through the 1-K!l resistor.

The amplifiers act as buffers for divider networks and reduce the interaction between stages. Eight levels of attenuation are possible with the circuit as illust..rated, but more stages could be added. Each divider network must be closely matched to the resistor ratios shown or the level of attenuation will not match the levels in the logic chart.

The circuit described features a multi-stage attenuation system designed to provide precise control over signal levels while minimizing interaction between stages. The initial buffer stage is crucial for isolating the input signal from subsequent components, ensuring that the signal integrity is maintained throughout the attenuation process.

Each stage of attenuation is implemented using a voltage divider configuration, which consists of two resistors in series, along with a CMOS switch that determines whether the signal is passed through or blocked. When the CMOS switch is closed, the voltage divider effectively reduces the signal amplitude according to the established resistor values, adhering to the voltage divider formula \( V_{out} = V_{in} \times \frac{R2}{R1 + R2} \). This allows for precise control over the attenuation level at each stage.

In instances where the CMOS switch is open, the design incorporates a 1 kΩ resistor that allows the majority of the signal to bypass the divider network, ensuring that signal strength is preserved for subsequent stages. This feature is particularly useful in applications where certain attenuation levels are not required, allowing for flexibility in signal processing.

The amplifiers included in the circuit play a dual role: they act as buffers to prevent loading effects between the voltage divider networks and enhance the overall signal quality. By isolating the output of each divider from the input of the next, the amplifiers help to mitigate any potential interactions that could affect the performance of the circuit.

The design supports up to eight levels of attenuation, providing a versatile solution for various signal processing needs. However, the architecture is scalable, allowing for the addition of more stages if necessary. It is essential to maintain the specified resistor ratios within each divider network to ensure that the attenuation levels correspond accurately to the intended logic chart. Deviations from these ratios could lead to discrepancies in the expected output, potentially affecting the overall functionality of the circuit. Thus, careful design and component selection are critical for achieving the desired performance in this attenuation system.The first stage is a simple buffer used to isolate the signal source from the attenuator stages to follow. Each of the subsequent stages is preceded by a voltage divider formed by two resistors and CMOS switch.

Provided that the CMOS switch for each stage is closed, the drive signal will be attenuated according to the basic voltage divider relationship at each stage. In the event a switch is open, nearly all of the signal strength will be passed to the next stage through the 1-K!l resistor.

The amplifiers act as buffers for divider networks and reduce the interaction between stages. Eight levels of attenuation are possible with the circuit as illust..rated, but more stages could be added. Each divider network must be closely matched to the resistor ratios shown or the level of attenuation will not match the levels in the logic chart.