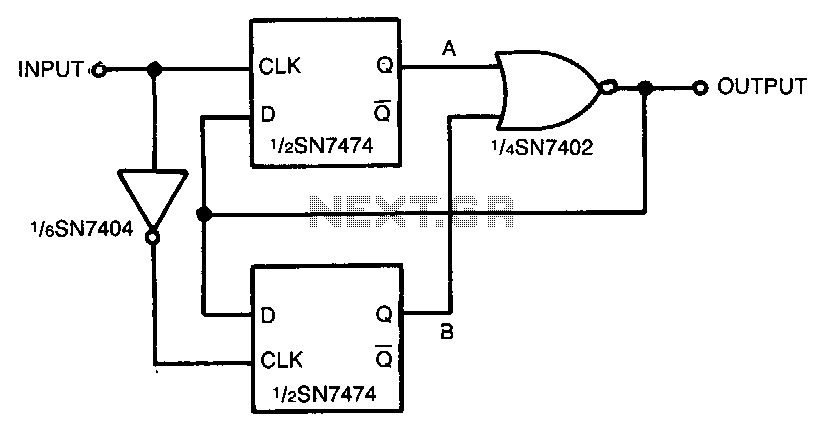

Divide-circuit

An input signal drives both SN74 D-type flip-flops, which are positive edge-triggered devices. A low-to-high input signal transition triggers the A flip-flop, while a high-to-low input signal transition triggers the B flip-flop via the SN7404 inverter. Either flip-flop in the high state will cause the output to decrease via the SN7402 NOR gate. This, in turn, disables the opposite flip-flop from going to the high state. The flip-flop in the high state remains there for one clock period, then it is clocked low. With both flip-flops low, the output increases, enabling the opposite flip-flop to be clocked high one-half clock cycle later. This alternate enabling and disabling action of the flip-flops results in a divide-by-1112 function. That is, three clock pulses in produce two evenly spaced clock pulses out. The circuit has no lock-up states and no inherent glitches. Replacing the NOR gate with an SN7400 NAND gate inverts the A, B, and output signals. By adding simple binary or BCD counters, counting chains such as divide-by-3, -6, -12, -24, -15, -30, etc., can be generated using the divide-by-11/2 circuit as a basis.

The circuit described utilizes two SN74 D-type flip-flops configured in a manner that allows for the division of input clock pulses. The positive edge-triggered nature of the flip-flops means that they respond to transitions in the input signal, specifically a low-to-high transition for the A flip-flop and a high-to-low transition for the B flip-flop, which is facilitated by the SN7404 inverter.

When the A flip-flop is triggered and enters a high state, it causes a decrease in the output through the SN7402 NOR gate. This decrease effectively disables the B flip-flop from transitioning to the high state, thereby creating a feedback loop that regulates the states of the two flip-flops. The high state of either flip-flop is maintained for one clock period before transitioning to low. During this time, when both flip-flops are low, the output will increase, allowing the opposite flip-flop to be clocked into a high state after a half clock cycle.

This sequential toggling of the flip-flops leads to the desired divide-by-11/2 functionality, where three input clock pulses yield two output clock pulses that are evenly spaced. The design is robust, exhibiting no lock-up states or glitches, which are common issues in digital circuits. Furthermore, the option to replace the NOR gate with an SN7400 NAND gate introduces signal inversion, allowing for greater flexibility in circuit design.

Additionally, the circuit can be expanded by integrating simple binary or BCD counters to create versatile counting chains such as divide-by-3, -6, -12, -24, -15, and -30. This modularity enhances the utility of the divide-by-11/2 circuit, making it an effective building block for more complex digital systems. The careful arrangement of components and the inherent feedback mechanisms ensure reliable operation across various applications in digital electronics.An input signal drives both SN74 74 D-type flip-flops, which are positive edge-triggered devices. A low-to-high input signal transition triggers tbe A flip-flop, while a high-to-low input signal transition triggers the B flip-flop via tbe SN7404 inverter. Either flip-flop in tbe high state will cause the output to decrease via the SN7402 NOR gate. This in turn disables the opposite flip-flop from going to tbe high state. The flipflop in the high state remains there for one clock period, then it is clocked low. Witb both flip-flops low, the output increases, enabling the opposite flip-flop to be clocked high one-half clock cycle later.

This alternate enabling and disabling action of the flip-flops results in a divide-by-1112 function. That is, three clock pulses in, produce two evenly spaced clock pulses out. The circuit has no lock-up states and no inherent glitches. Replacing the NOR gate with an SN7400 NAND gate inverts the A, B, and output signals. By adding simple binary or BCD counters, counting chains, such as divide-by-3, -6, -12, -24, -15, -30, etc., can be generated using the divide-by-11/z circuit as a basis.

The circuit described utilizes two SN74 D-type flip-flops configured in a manner that allows for the division of input clock pulses. The positive edge-triggered nature of the flip-flops means that they respond to transitions in the input signal, specifically a low-to-high transition for the A flip-flop and a high-to-low transition for the B flip-flop, which is facilitated by the SN7404 inverter.

When the A flip-flop is triggered and enters a high state, it causes a decrease in the output through the SN7402 NOR gate. This decrease effectively disables the B flip-flop from transitioning to the high state, thereby creating a feedback loop that regulates the states of the two flip-flops. The high state of either flip-flop is maintained for one clock period before transitioning to low. During this time, when both flip-flops are low, the output will increase, allowing the opposite flip-flop to be clocked into a high state after a half clock cycle.

This sequential toggling of the flip-flops leads to the desired divide-by-11/2 functionality, where three input clock pulses yield two output clock pulses that are evenly spaced. The design is robust, exhibiting no lock-up states or glitches, which are common issues in digital circuits. Furthermore, the option to replace the NOR gate with an SN7400 NAND gate introduces signal inversion, allowing for greater flexibility in circuit design.

Additionally, the circuit can be expanded by integrating simple binary or BCD counters to create versatile counting chains such as divide-by-3, -6, -12, -24, -15, and -30. This modularity enhances the utility of the divide-by-11/2 circuit, making it an effective building block for more complex digital systems. The careful arrangement of components and the inherent feedback mechanisms ensure reliable operation across various applications in digital electronics.An input signal drives both SN74 74 D-type flip-flops, which are positive edge-triggered devices. A low-to-high input signal transition triggers tbe A flip-flop, while a high-to-low input signal transition triggers the B flip-flop via tbe SN7404 inverter. Either flip-flop in tbe high state will cause the output to decrease via the SN7402 NOR gate. This in turn disables the opposite flip-flop from going to tbe high state. The flipflop in the high state remains there for one clock period, then it is clocked low. Witb both flip-flops low, the output increases, enabling the opposite flip-flop to be clocked high one-half clock cycle later.

This alternate enabling and disabling action of the flip-flops results in a divide-by-1112 function. That is, three clock pulses in, produce two evenly spaced clock pulses out. The circuit has no lock-up states and no inherent glitches. Replacing the NOR gate with an SN7400 NAND gate inverts the A, B, and output signals. By adding simple binary or BCD counters, counting chains, such as divide-by-3, -6, -12, -24, -15, -30, etc., can be generated using the divide-by-11/z circuit as a basis.