Duty-cycle-monitor

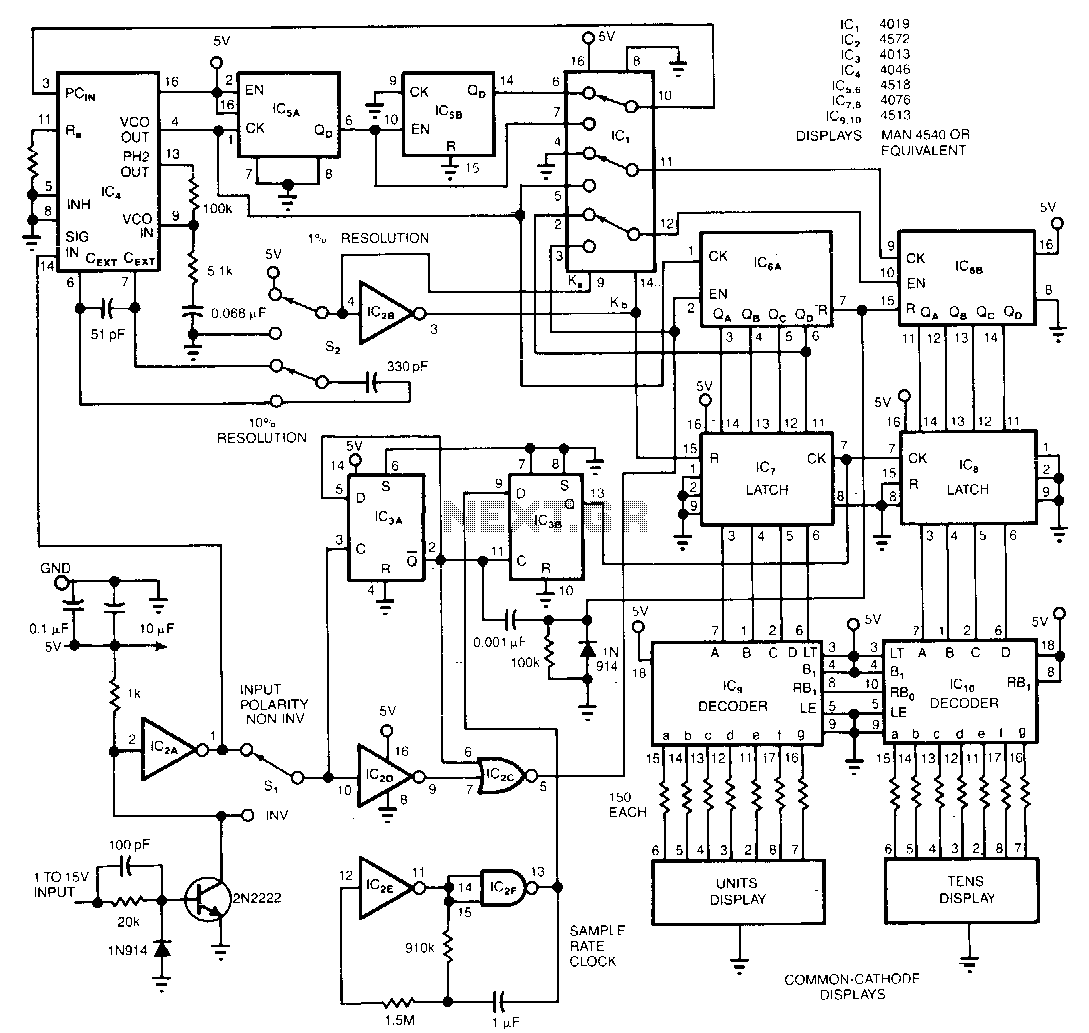

The circuit monitors and displays a digital signal's duty cycle with an accuracy of ±1%. By using switch S2, users can select a frequency range of either 250 Hz to 2.5 kHz with ±1% accuracy or 2 kHz to 50 kHz with ±10% accuracy. A common-cathode display indicates the duty cycle percentage of the signal. The phase-locked loop (PLL) and counters Ie5A and Ie5B multiply the input frequency by a factor of either 10 or 100, depending on the setting of switch S2. Counters re6A and re6B count the multiplied frequency during the mark interval of the incoming signal. Counters re7 and re5 then latch this count and display it at the clock's sample rate. For instance, if a 1% resolution is selected and the signal's mark period is 40% of the total period, the circuit enables the counter composed of re6A and re6B for 40 counts. To achieve space-interval sampling, the input polarity can be reversed using switch S1. Counter re2A samples the input signal's period and enables gate re2E to reset the counter. Counters Ie2E and re2F create the sample-rate clock, while counter re3B synchronizes the clock's output with the input, allowing the circuit to update latches re7 and re5.

The circuit design incorporates several key components to accurately monitor and display the duty cycle of a digital signal. The use of a phase-locked loop (PLL) facilitates frequency multiplication, which is essential for precise duty cycle measurements. The PLL captures the incoming frequency and, through counters Ie5A and Ie5B, multiplies it by a factor of 10 or 100 based on the selection made via switch S2. This multiplication is critical for enhancing the resolution of the duty cycle measurement, especially at higher frequencies.

The common-cathode display serves as the output interface, providing a clear visual representation of the duty cycle percentage. The counters re6A and re6B play a vital role in counting the pulses during the mark interval of the incoming signal, which is indicative of the active state. The latching of these counts by re7 and re5 ensures that the displayed value remains stable during the clock's sampling period, allowing for accurate reading.

The circuit's flexibility is further enhanced by the ability to reverse the input polarity using switch S1, which is beneficial for applications requiring space-interval sampling. The sampling process is managed by counter re2A, which captures the period of the input signal. This action triggers gate re2E to reset the counter, ensuring that the measurement cycle begins anew with each signal period.

Additionally, the sample-rate clock generated by counters Ie2E and re2F is synchronized with the input signal by counter re3B. This synchronization is crucial for maintaining measurement accuracy, as it aligns the sampling instances with the actual signal transitions, thereby allowing the circuit to update the latches re7 and re5 with the most current data.

Overall, the circuit's architecture is designed for high-precision duty cycle measurement across a range of frequencies, making it suitable for various applications in digital signal processing and electronic testing.The circuit monitors and displays a digital signal"s duty cycle and provides accuracy as high as ±1%. Using switch S2, you can choose a frequency range of either 250 Hz to 2. 5 kHz at ±1% accuracy or 2 kHz to 50 kHz at ±10% accuracy. The common-cathode display gives the signal"s duty-cycle percentage. Phase-locked loop re4 and counters Ie5A and re5B multiply the input frequency by a factor of either 10 or 100, depending on switch S2"s setting.

re6A and re6B count this multiplied frequency during the incoming signal"s mark interval. re7 and res then latch this count and display it at the clock"s sample rate. For example, ifyou select a 1 % resolution, when the signal"s mark periodis 40% of the total period, the circuit will enable the counter comprising re6A and re6B for 40 counts. To obtain space-interval sampling, you can reverse the input polarity using switch Sl. re2A samples the input signal"s period and enables gate reze and resets the counter. Ie2E and re2F form the sample-rate clock; re3B synchronizes the clock"s output with the input, so that the circuit can update latches re7 and res.

The circuit design incorporates several key components to accurately monitor and display the duty cycle of a digital signal. The use of a phase-locked loop (PLL) facilitates frequency multiplication, which is essential for precise duty cycle measurements. The PLL captures the incoming frequency and, through counters Ie5A and Ie5B, multiplies it by a factor of 10 or 100 based on the selection made via switch S2. This multiplication is critical for enhancing the resolution of the duty cycle measurement, especially at higher frequencies.

The common-cathode display serves as the output interface, providing a clear visual representation of the duty cycle percentage. The counters re6A and re6B play a vital role in counting the pulses during the mark interval of the incoming signal, which is indicative of the active state. The latching of these counts by re7 and re5 ensures that the displayed value remains stable during the clock's sampling period, allowing for accurate reading.

The circuit's flexibility is further enhanced by the ability to reverse the input polarity using switch S1, which is beneficial for applications requiring space-interval sampling. The sampling process is managed by counter re2A, which captures the period of the input signal. This action triggers gate re2E to reset the counter, ensuring that the measurement cycle begins anew with each signal period.

Additionally, the sample-rate clock generated by counters Ie2E and re2F is synchronized with the input signal by counter re3B. This synchronization is crucial for maintaining measurement accuracy, as it aligns the sampling instances with the actual signal transitions, thereby allowing the circuit to update the latches re7 and re5 with the most current data.

Overall, the circuit's architecture is designed for high-precision duty cycle measurement across a range of frequencies, making it suitable for various applications in digital signal processing and electronic testing.The circuit monitors and displays a digital signal"s duty cycle and provides accuracy as high as ±1%. Using switch S2, you can choose a frequency range of either 250 Hz to 2. 5 kHz at ±1% accuracy or 2 kHz to 50 kHz at ±10% accuracy. The common-cathode display gives the signal"s duty-cycle percentage. Phase-locked loop re4 and counters Ie5A and re5B multiply the input frequency by a factor of either 10 or 100, depending on switch S2"s setting.

re6A and re6B count this multiplied frequency during the incoming signal"s mark interval. re7 and res then latch this count and display it at the clock"s sample rate. For example, ifyou select a 1 % resolution, when the signal"s mark periodis 40% of the total period, the circuit will enable the counter comprising re6A and re6B for 40 counts. To obtain space-interval sampling, you can reverse the input polarity using switch Sl. re2A samples the input signal"s period and enables gate reze and resets the counter. Ie2E and re2F form the sample-rate clock; re3B synchronizes the clock"s output with the input, so that the circuit can update latches re7 and res.