Leading-edge-delay

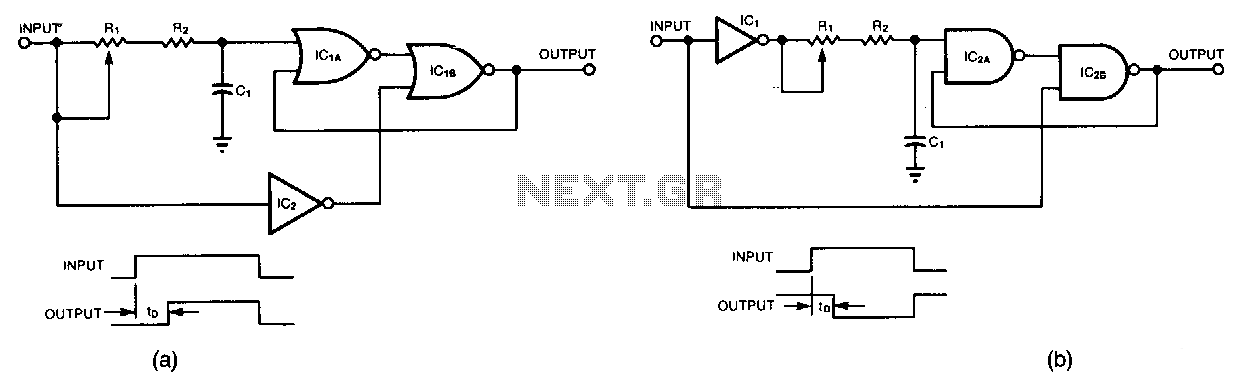

Circuit (a) delays the leading edge of a positive pulse while leaving the trailing edge nearly unaffected. A positive input transition, inverted by IC2, does not impact IC1B. However, when the positive transition reaches IC1A, delayed by the adjustable network consisting of R1, R2, and C1, it toggles both NOR gates, initiating the output pulse. When the input decreases, IC1B follows suit, only delayed by its propagation through itself and IC2. Circuit (b) produces an inverted output pulse. Inverter IC1 serves as a buffer for the signal source, which is advantageous when driving a low-impedance (short-delay) network. Furthermore, only the propagation delay of IC2B separates the output's trailing edge from that of the input. Circuit (a) can be configured to handle negative pulses by using NAND gates instead of NOR gates. Similarly, circuit (b) will produce a delayed positive pulse in response to a negative input pulse if NOR gates are substituted for NAND gates.

Circuit (a) employs a combination of NOR gates and an adjustable RC network to achieve a delayed leading edge of a positive pulse. The input signal first passes through IC2, which inverts the signal, but this inversion does not affect the behavior of IC1B. The adjustable network made up of resistors R1 and R2, along with capacitor C1, introduces a delay to the positive transition at IC1A. This delay is crucial as it allows for the toggling of both NOR gates, thereby initiating the output pulse at a specific time after the input transition occurs. The trailing edge of the output pulse remains largely unaffected due to the inherent characteristics of the NOR gate configuration.

In the case of input signal decrease, IC1B responds with a similar decrease, albeit with a slight delay attributed to the propagation time through IC2. This design allows for precise control over the timing characteristics of the output pulse, making it suitable for applications where pulse timing is critical.

Circuit (b) functions as an inverter, producing an inverted output pulse. The inverter IC1 acts as a buffer for the signal source, which is particularly beneficial when interfacing with low-impedance networks that require minimal delay. The only delay present at the output's trailing edge, relative to the input, is introduced by the propagation delay of IC2B.

For applications requiring the handling of negative pulses, circuit (a) can be modified by replacing the NOR gates with NAND gates. This modification allows the circuit to respond appropriately to negative input pulses while maintaining the desired delay characteristics. Similarly, circuit (b) can be adapted to generate a delayed positive pulse in response to a negative input pulse by substituting NAND gates for NOR gates, further enhancing the versatility of the design. This adaptability makes both circuits valuable in various electronic applications where pulse shaping and timing are essential.Circuit (a) lets you delay the leading edge of a positive pulse while leaving the trailing edge almost unaffected. A positive input transition, inverted hy IC2, has no effect on IC1B. However, when the positive transition reaches IC1A, (delayed hy the adjustable network of R1, R2, and C1), it toggles both NOR gates, initiating the output pulse.

When the input decreases IC1B follows suit, delayed only by the propagation through itself and IC2. Circuit (b) produces~an inverted output pulse. Inverter IC1 serves as a buffer for the signal source-an advantage when driving a low-impedance (short-delay) network. Moreover, only the propagation delay of IC2B separates the output"s trailing edge from that of the input.

You can configure circuit (a) to handle negative pulses hy using NAND instead of NOR gates. Similarly, circuit (b) will produce a delayed positive pulse in response to negative input pulse, if you substitute NOR gates for NAND gates.

Circuit (a) employs a combination of NOR gates and an adjustable RC network to achieve a delayed leading edge of a positive pulse. The input signal first passes through IC2, which inverts the signal, but this inversion does not affect the behavior of IC1B. The adjustable network made up of resistors R1 and R2, along with capacitor C1, introduces a delay to the positive transition at IC1A. This delay is crucial as it allows for the toggling of both NOR gates, thereby initiating the output pulse at a specific time after the input transition occurs. The trailing edge of the output pulse remains largely unaffected due to the inherent characteristics of the NOR gate configuration.

In the case of input signal decrease, IC1B responds with a similar decrease, albeit with a slight delay attributed to the propagation time through IC2. This design allows for precise control over the timing characteristics of the output pulse, making it suitable for applications where pulse timing is critical.

Circuit (b) functions as an inverter, producing an inverted output pulse. The inverter IC1 acts as a buffer for the signal source, which is particularly beneficial when interfacing with low-impedance networks that require minimal delay. The only delay present at the output's trailing edge, relative to the input, is introduced by the propagation delay of IC2B.

For applications requiring the handling of negative pulses, circuit (a) can be modified by replacing the NOR gates with NAND gates. This modification allows the circuit to respond appropriately to negative input pulses while maintaining the desired delay characteristics. Similarly, circuit (b) can be adapted to generate a delayed positive pulse in response to a negative input pulse by substituting NAND gates for NOR gates, further enhancing the versatility of the design. This adaptability makes both circuits valuable in various electronic applications where pulse shaping and timing are essential.Circuit (a) lets you delay the leading edge of a positive pulse while leaving the trailing edge almost unaffected. A positive input transition, inverted hy IC2, has no effect on IC1B. However, when the positive transition reaches IC1A, (delayed hy the adjustable network of R1, R2, and C1), it toggles both NOR gates, initiating the output pulse.

When the input decreases IC1B follows suit, delayed only by the propagation through itself and IC2. Circuit (b) produces~an inverted output pulse. Inverter IC1 serves as a buffer for the signal source-an advantage when driving a low-impedance (short-delay) network. Moreover, only the propagation delay of IC2B separates the output"s trailing edge from that of the input.

You can configure circuit (a) to handle negative pulses hy using NAND instead of NOR gates. Similarly, circuit (b) will produce a delayed positive pulse in response to negative input pulse, if you substitute NOR gates for NAND gates.