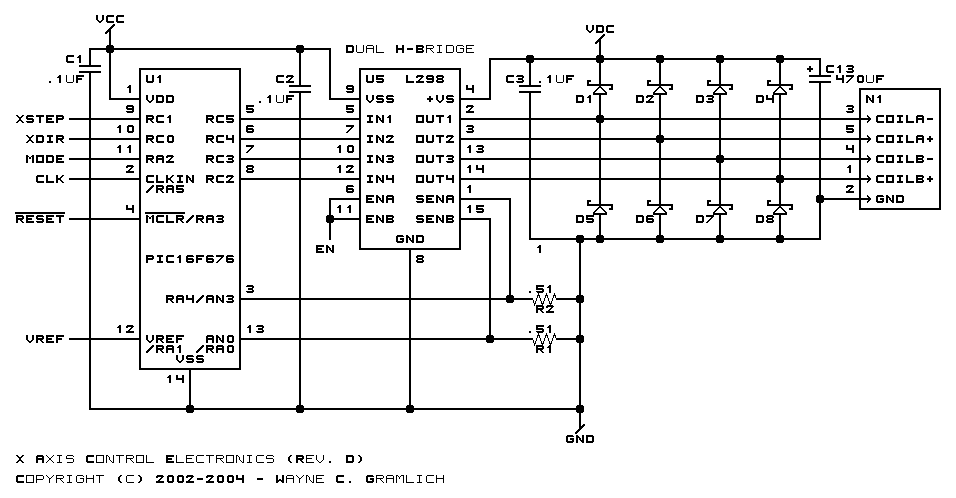

Mk1 Schematics

This software is highly effective, user-friendly, and enjoyable to utilize. It features an extensive library of symbols and includes a library editor for creating custom symbols. All drawings were completed before any soldering commenced, instilling confidence that all elements were accounted for. Connections were verified systematically, making the wiring process straightforward and stress-free. Each connection was checked with a continuity test, confirming functionality. The original diagrams are available in vector format, allowing for scalable adjustments. When converting to GIF for web use, a width of 1000 pixels was selected. The original high-resolution schematics can be downloaded. The circuit employs 28-pin sockets for RAM chips, with a jumper to select between the 6116 or 6264 chips. The 6116 was chosen for installation, but support for both types was included due to the scarcity of the 6116. The cards incorporate LS157 Quad 1-of-2 multiplexers for control inputs, with a jumper allowing configuration as either W or IP through the LS157 common select input. The I/O card was constructed and tested prior to the ALU. A hex tri-state inverter (U4) was intended to gate the RXRDY signal onto D0 for conditional testing; however, this approach was deemed ineffective as inputs to the conditional multiplexer must remain stable during a skip. Consequently, the LS368 was mounted on a header with a transparent latch until the ALU was completed. The connections to D0 and D1 have since been severed. The initial plan was to operate the UART in x1 clock mode, providing options for 38K4, 19K2, or 9600 baud rates. However, reliable reception was only achieved in x16 and x64 modes. The maximum baud rate attainable in x16 mode, using the Q4 output of the 4060 divider, is 9600 from a 2.4576 MHz crystal.

The described circuit encompasses a sophisticated design tailored for a microcontroller system, integrating various components to facilitate efficient data processing and communication. The use of 28-pin sockets for RAM chips allows for flexibility in memory selection, accommodating both the 6116 and 6264 RAM types. The LS157 multiplexers play a crucial role in managing control signals, enabling the system to switch configurations as needed. The jumper settings provide versatility, allowing the system to adapt to different operational requirements.

The design emphasizes systematic testing and verification, with a focus on ensuring that each connection is functional before final assembly. The choice of using a hex tri-state inverter for gating signals demonstrates a thoughtful approach to managing data flow, although adjustments were necessary to accommodate the stability requirements of the multiplexer inputs.

The transition from x1 to x16 and x64 modes for UART operation highlights the importance of signal integrity in high-speed communication. The decision to limit the operational modes to those that ensure reliable reception underscores the necessity of robust design practices in electronic circuit development. The use of a 2.4576 MHz crystal to achieve the desired baud rate reflects an understanding of frequency selection in relation to communication protocols.

Overall, this circuit design showcases a blend of innovative engineering and practical problem-solving, resulting in a reliable and efficient system for data handling and transmission.This is an excellent piece of software. It is very easy and enjoyable to use. It comes with a huge library of symbols and also has a library editor for creating your own. I completed all the drawing before a single joint was soldered. This gave me confidence that everything was covered. Ticking off the connections as I went, wiringwas a stress-free no-brainer. Afterwards, I buzzed-out every connection and, again, ticked them off as I went. The original diagrams are in vector format and can thus be scaled to any desired size. In converting them to GIF for the web, I selected a width of 1000 pixels. Download the original hi-res schematics here. I used 28 pin sockets for the RAM chips with a jumper to select 6116 or 6264. I fitted the former but thought it best to support both because the 6116 is hard to source now. The cards also have LS157 Quad 1-of-2 multiplexers for the control inputs. A jumper configures the cards as either W or IP via the LS157 common select input. The I/O card was built and tested before the ALU. I planned to use U4, a hex tri-state inverter, to gate the RXRDY signal onto D0 for conditional tests. Unfortunately, this wouldn`t have worked because inputs to the conditional multiplexer must be stable throughout a skip.

I had to mount the LS368 on a header with a transparent latch until the ALU was ready! The links to D0 and D1 have now been broken. I originally hoped to operate the UART in the x1 clock mode giving the option of 38K4, 19K2 or 9600 baud. Unfortunately, reception is only reliable in the x16 and x64 modes. The maximum attainable baud rate, using the x16 mode and the Q4 output of the 4060 divider, is 9600 from a 2.

4576MHz crystal. 🔗 External reference

The described circuit encompasses a sophisticated design tailored for a microcontroller system, integrating various components to facilitate efficient data processing and communication. The use of 28-pin sockets for RAM chips allows for flexibility in memory selection, accommodating both the 6116 and 6264 RAM types. The LS157 multiplexers play a crucial role in managing control signals, enabling the system to switch configurations as needed. The jumper settings provide versatility, allowing the system to adapt to different operational requirements.

The design emphasizes systematic testing and verification, with a focus on ensuring that each connection is functional before final assembly. The choice of using a hex tri-state inverter for gating signals demonstrates a thoughtful approach to managing data flow, although adjustments were necessary to accommodate the stability requirements of the multiplexer inputs.

The transition from x1 to x16 and x64 modes for UART operation highlights the importance of signal integrity in high-speed communication. The decision to limit the operational modes to those that ensure reliable reception underscores the necessity of robust design practices in electronic circuit development. The use of a 2.4576 MHz crystal to achieve the desired baud rate reflects an understanding of frequency selection in relation to communication protocols.

Overall, this circuit design showcases a blend of innovative engineering and practical problem-solving, resulting in a reliable and efficient system for data handling and transmission.This is an excellent piece of software. It is very easy and enjoyable to use. It comes with a huge library of symbols and also has a library editor for creating your own. I completed all the drawing before a single joint was soldered. This gave me confidence that everything was covered. Ticking off the connections as I went, wiringwas a stress-free no-brainer. Afterwards, I buzzed-out every connection and, again, ticked them off as I went. The original diagrams are in vector format and can thus be scaled to any desired size. In converting them to GIF for the web, I selected a width of 1000 pixels. Download the original hi-res schematics here. I used 28 pin sockets for the RAM chips with a jumper to select 6116 or 6264. I fitted the former but thought it best to support both because the 6116 is hard to source now. The cards also have LS157 Quad 1-of-2 multiplexers for the control inputs. A jumper configures the cards as either W or IP via the LS157 common select input. The I/O card was built and tested before the ALU. I planned to use U4, a hex tri-state inverter, to gate the RXRDY signal onto D0 for conditional tests. Unfortunately, this wouldn`t have worked because inputs to the conditional multiplexer must be stable throughout a skip.

I had to mount the LS368 on a header with a transparent latch until the ALU was ready! The links to D0 and D1 have now been broken. I originally hoped to operate the UART in the x1 clock mode giving the option of 38K4, 19K2 or 9600 baud. Unfortunately, reception is only reliable in the x16 and x64 modes. The maximum attainable baud rate, using the x16 mode and the Q4 output of the 4060 divider, is 9600 from a 2.

4576MHz crystal. 🔗 External reference