Positive-triggered-monostable

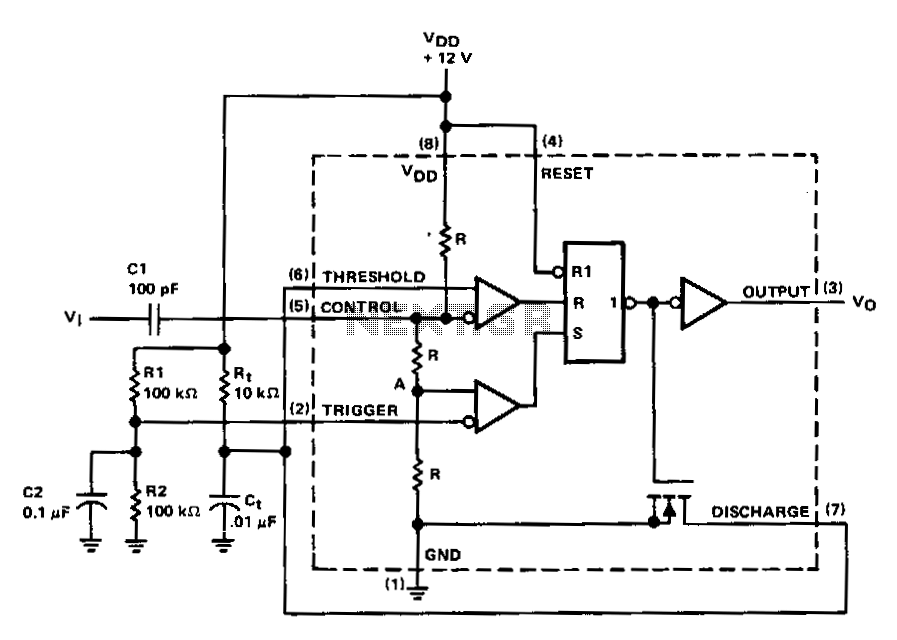

A positive-going trigger pulse can be used to initiate the timing cycle with the circuit shown. In this design, trigger input pin 2 is biased to 6V by divider R1 and R2. Control input pin 5 is biased to 8V by the internal divider circuit. With no trigger voltage applied, point A is at 4V. To activate the timer, the voltage at point A must exceed the 6V present on pin 2. A positive 5V trigger pulse applied to control input pin 5 is AC coupled through capacitor C1, which adds the trigger voltage to the 8V already present on pin 5, resulting in 13V with respect to ground. The output pulse width is determined by the values of R1 and C1. When the voltage at point A is increased to 6.5V, which is greater than the 6V on pin 2, the timer cycle is initiated. The output of timer pin 3 increases, turning off the discharge transistor at pin 7 and allowing C1 to charge through resistor R1. When capacitor C1 charges to the upper threshold voltage of 8V, the flip-flop is reset and output pin 3 decreases. Capacitor C1 then discharges through the discharge transistor. The timer cannot be triggered again until another trigger pulse is applied to control input pin 5.

The circuit design involves a timing mechanism that utilizes a positive-going trigger pulse to initiate its operation. The input pins are strategically biased using resistor dividers to establish reference voltages critical for the timer's functionality. Specifically, trigger input pin 2 is set to 6V, while control input pin 5 is maintained at 8V. This configuration ensures that the timer remains inactive until a trigger pulse is received.

The voltage at point A serves as a critical threshold for initiating the timing cycle. Initially set at 4V, point A must exceed 6V to activate the timer. The application of a 5V trigger pulse to control input pin 5 is facilitated through an AC coupling capacitor, C1. This coupling allows the trigger pulse to add to the existing 8V, resulting in a total of 13V at pin 5, which is sufficient to activate the timing cycle.

The duration of the output pulse is governed by the values of resistor R1 and capacitor C1. As point A's voltage reaches 6.5V, surpassing the 6V threshold on pin 2, the timer cycle begins. The output at timer pin 3 transitions high, which deactivates the discharge transistor connected to pin 7, thereby permitting capacitor C1 to charge through resistor R1.

Once capacitor C1 reaches the upper threshold voltage of 8V, the internal flip-flop of the timer resets, causing the output at pin 3 to drop. Following this, capacitor C1 discharges through the discharge transistor, effectively completing the timing cycle. It is important to note that the timer will not respond to further trigger pulses until the cycle has fully completed and another trigger pulse is applied to control input pin 5. This design ensures precise control over timing applications, making it suitable for various electronic timing tasks.A positive-going trigger pulse can be used to start the timing cycle with the circuit shown. In this design, trigger input pin 2 is biased to 6V (1/z Vvv) by divider Rl and R2. Control input pin 5 is biased to 8 V (213 Vvvl by the internal divider circuit. With no trigger voltage applied, point A is at 4 V (1/3 Vvv). To tum the timer on, the voltage at point A has to be greater than the 6 V present on pin 2. Positive 5-V trigger pulse V, applied to the control input pin 5 is ac coupled through capacitor Cl, adding the trigger voltage to the 8 V already on pin 5; this results in 13 V with respect to ground. The output pulse width is determined by the values of R, and C,. When voltage at point A is increased to 6.5 V, which is greater than the 6 V on pin 2, the timer cycle is initialized. The output of timer pin 3 increases, turning off discharge transistor pin 7 and allowing C, to charge through resistor R,.

When capacitor C, charges to the upper threshold voltage of 8 V (2/3 Vvv), the flip-flop is reset and output pin 3 decreases. Capacitor C, then discharges through the discharge transistor. The timer is not triggered again until another trigger pulse is applied to contrgl input pin 5.

The circuit design involves a timing mechanism that utilizes a positive-going trigger pulse to initiate its operation. The input pins are strategically biased using resistor dividers to establish reference voltages critical for the timer's functionality. Specifically, trigger input pin 2 is set to 6V, while control input pin 5 is maintained at 8V. This configuration ensures that the timer remains inactive until a trigger pulse is received.

The voltage at point A serves as a critical threshold for initiating the timing cycle. Initially set at 4V, point A must exceed 6V to activate the timer. The application of a 5V trigger pulse to control input pin 5 is facilitated through an AC coupling capacitor, C1. This coupling allows the trigger pulse to add to the existing 8V, resulting in a total of 13V at pin 5, which is sufficient to activate the timing cycle.

The duration of the output pulse is governed by the values of resistor R1 and capacitor C1. As point A's voltage reaches 6.5V, surpassing the 6V threshold on pin 2, the timer cycle begins. The output at timer pin 3 transitions high, which deactivates the discharge transistor connected to pin 7, thereby permitting capacitor C1 to charge through resistor R1.

Once capacitor C1 reaches the upper threshold voltage of 8V, the internal flip-flop of the timer resets, causing the output at pin 3 to drop. Following this, capacitor C1 discharges through the discharge transistor, effectively completing the timing cycle. It is important to note that the timer will not respond to further trigger pulses until the cycle has fully completed and another trigger pulse is applied to control input pin 5. This design ensures precise control over timing applications, making it suitable for various electronic timing tasks.A positive-going trigger pulse can be used to start the timing cycle with the circuit shown. In this design, trigger input pin 2 is biased to 6V (1/z Vvv) by divider Rl and R2. Control input pin 5 is biased to 8 V (213 Vvvl by the internal divider circuit. With no trigger voltage applied, point A is at 4 V (1/3 Vvv). To tum the timer on, the voltage at point A has to be greater than the 6 V present on pin 2. Positive 5-V trigger pulse V, applied to the control input pin 5 is ac coupled through capacitor Cl, adding the trigger voltage to the 8 V already on pin 5; this results in 13 V with respect to ground. The output pulse width is determined by the values of R, and C,. When voltage at point A is increased to 6.5 V, which is greater than the 6 V on pin 2, the timer cycle is initialized. The output of timer pin 3 increases, turning off discharge transistor pin 7 and allowing C, to charge through resistor R,.

When capacitor C, charges to the upper threshold voltage of 8 V (2/3 Vvv), the flip-flop is reset and output pin 3 decreases. Capacitor C, then discharges through the discharge transistor. The timer is not triggered again until another trigger pulse is applied to contrgl input pin 5.