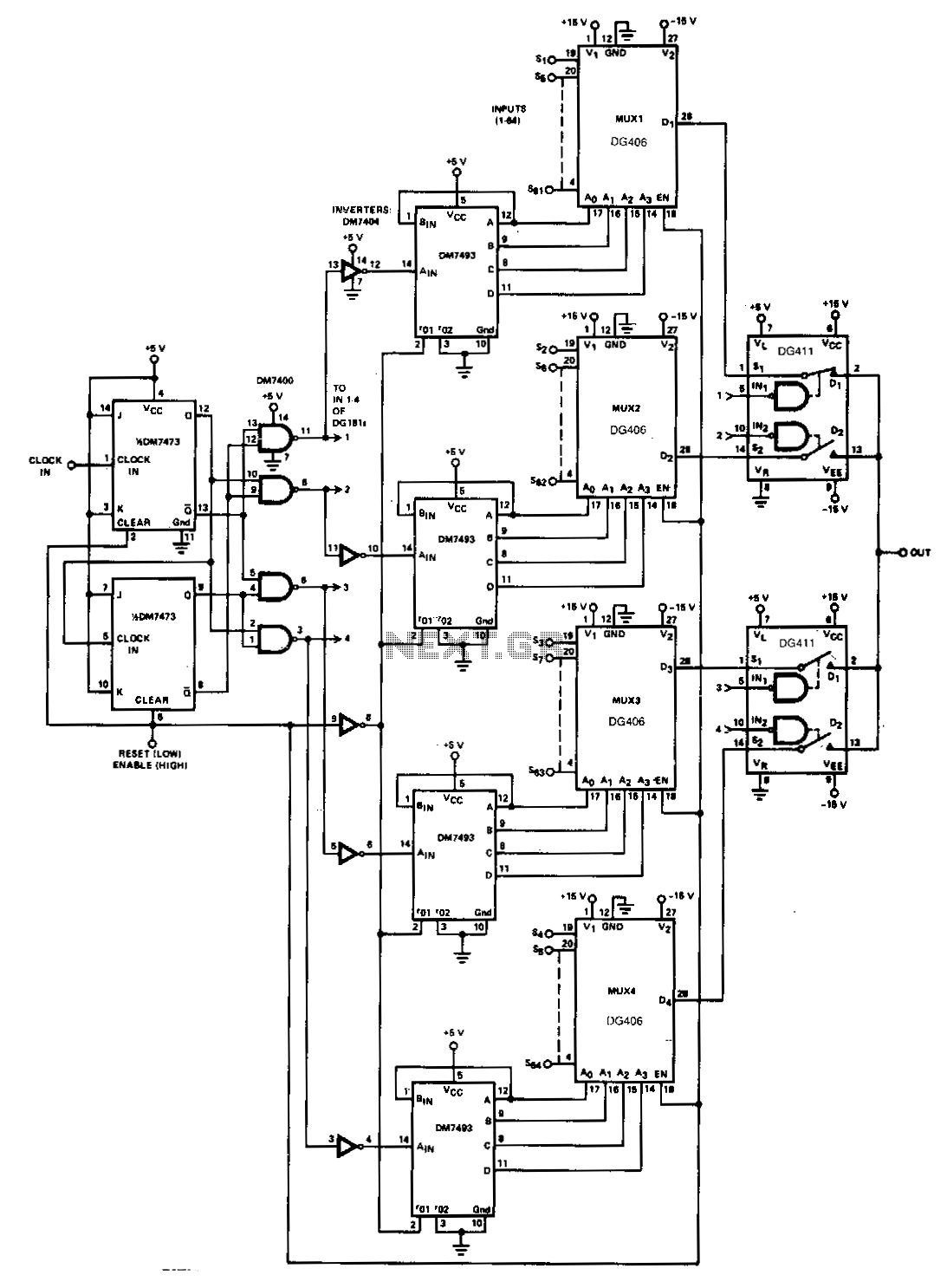

Two-level-multiplexer

When a large number of channels are multiplexed, the outputs of two or more multiplexers can be connected together, and each multiplexer can be enabled sequentially. In the inhibit mode, the multiplexer consumes less power, and its output and inputs behave as open circuits. Theoretically, an infinite number of channels can be accommodated in this manner; however, in practice, the accumulated output capacitance and leakage from multiple paralleled multiplexers restrict the speed and accuracy of the system. A more effective approach is the two-level multiplex system. The two-level system features a bank of high-speed switches at the output, which sequentially switch between the four DG406 multiplexers. Each DG406 is capable of switching while the other three are being interrogated. The DG406s contribute leakage and capacitance at the output only when they are activated by the DG411 for one-fourth of the time. The two-level multiplex system is particularly advantageous in communication links, high-speed interfacing with comparators, or any application requiring the multiplexing of a large number of channels at high speeds.

The two-level multiplex system represents a significant advancement in the design of multiplexing circuits, particularly in applications that demand high-speed data transmission and minimal signal degradation. In this architecture, the integration of high-speed switches enhances the overall performance by allowing for rapid channel selection without the drawbacks associated with traditional multiplexing methods.

The DG406 multiplexers serve as the primary switching elements within the two-level system. Each DG406 is designed to handle multiple input channels and can effectively route the selected signal to the output. The design ensures that while one DG406 is activated, the others remain in a low-power state, thus minimizing power consumption and reducing the potential for crosstalk between channels. This selective activation is crucial for maintaining signal integrity, particularly in high-frequency applications where even minor leakage or capacitance can lead to significant performance issues.

The role of the DG411 in this system is to control the timing of the multiplexers. By enabling each DG406 for a fraction of the total time, the DG411 ensures that only one multiplexer is active at any given moment, thereby reducing the overall output capacitance and leakage effects. This controlled switching mechanism allows for higher data throughput and improved accuracy in signal processing.

In communication systems, where bandwidth and speed are critical, the two-level multiplex system provides an efficient solution for managing multiple data channels. This design is also applicable in various interfacing scenarios, such as connecting sensors to microcontrollers or facilitating communication between different components in a digital system. The ability to handle a large number of channels effectively while maintaining high performance makes this multiplexing approach a valuable asset in modern electronic circuit design.When a large number of channels are multiplexed, the outputs of two or more multiplexers can be connected together and each multiplexer sequentially enabled. In the inhibit mode. the multiplexer draws less power and its output and inputs act as open circuits. Theoretically, an infinite number of channels can be accommodated in this way; in practice, the accumulated output capacitance and leakage of many paralleled multiplexers limits the speed and accuracy of the system.

A much better method is the two-level multiplex system. The two-level system has a bank of high-speed switches at the output which sequentially switch between the four DG406s. Each DG406 is able to switch during the time the other three are being interrogated. The DG406s contribute leakage and capacitance at the output only, when they are switched on by the DG411-1/4 of the time.

The two-level multiplex system is very useful in communications links, high-speed interfacing with comparators, or wherever a large number of channels must be multiplexed at high speeds.

The two-level multiplex system represents a significant advancement in the design of multiplexing circuits, particularly in applications that demand high-speed data transmission and minimal signal degradation. In this architecture, the integration of high-speed switches enhances the overall performance by allowing for rapid channel selection without the drawbacks associated with traditional multiplexing methods.

The DG406 multiplexers serve as the primary switching elements within the two-level system. Each DG406 is designed to handle multiple input channels and can effectively route the selected signal to the output. The design ensures that while one DG406 is activated, the others remain in a low-power state, thus minimizing power consumption and reducing the potential for crosstalk between channels. This selective activation is crucial for maintaining signal integrity, particularly in high-frequency applications where even minor leakage or capacitance can lead to significant performance issues.

The role of the DG411 in this system is to control the timing of the multiplexers. By enabling each DG406 for a fraction of the total time, the DG411 ensures that only one multiplexer is active at any given moment, thereby reducing the overall output capacitance and leakage effects. This controlled switching mechanism allows for higher data throughput and improved accuracy in signal processing.

In communication systems, where bandwidth and speed are critical, the two-level multiplex system provides an efficient solution for managing multiple data channels. This design is also applicable in various interfacing scenarios, such as connecting sensors to microcontrollers or facilitating communication between different components in a digital system. The ability to handle a large number of channels effectively while maintaining high performance makes this multiplexing approach a valuable asset in modern electronic circuit design.When a large number of channels are multiplexed, the outputs of two or more multiplexers can be connected together and each multiplexer sequentially enabled. In the inhibit mode. the multiplexer draws less power and its output and inputs act as open circuits. Theoretically, an infinite number of channels can be accommodated in this way; in practice, the accumulated output capacitance and leakage of many paralleled multiplexers limits the speed and accuracy of the system.

A much better method is the two-level multiplex system. The two-level system has a bank of high-speed switches at the output which sequentially switch between the four DG406s. Each DG406 is able to switch during the time the other three are being interrogated. The DG406s contribute leakage and capacitance at the output only, when they are switched on by the DG411-1/4 of the time.

The two-level multiplex system is very useful in communications links, high-speed interfacing with comparators, or wherever a large number of channels must be multiplexed at high speeds.