Xor-gate-complementary-signals-generator

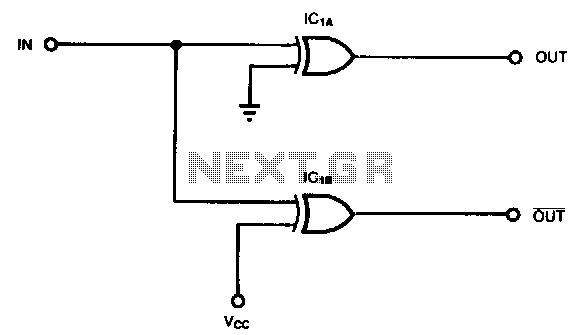

Some applications, such as driving three-state buffers for data multiplexers or for biphase clocks in high-speed systems, require complementary signals with minimal time skew and nearly simultaneous transitions. In this context, XOR gates serve as both inverting and non-inverting gates. For CMOS systems, virtually any type of XOR gate is suitable. However, the advanced-CMOS logic (ACL) families offer the highest drive capability, the shortest gate delays, and the most precise manufacturing tolerances. In TTL systems, compatible CMOS types such as the ACT or S/AS86 families are recommended. Avoid using low-power TTL versions (LS or ALS), as they exhibit significant propagation delay differences when one XOR gate is inverting and the other is non-inverting.

In high-speed digital circuits, the requirement for complementary signals with minimal skew and nearly simultaneous transitions is critical for maintaining signal integrity and performance. The use of XOR gates in this scenario is advantageous, as they can function as both inverting and non-inverting logic elements, providing flexibility in circuit design.

For CMOS systems, the variety of available XOR gates allows for compatibility across different designs, but selecting advanced-CMOS logic (ACL) families is particularly beneficial due to their superior characteristics. ACL families are designed to handle higher drive currents, which is essential for driving loads in high-speed applications. Additionally, their reduced gate delays contribute to improved overall system performance, making them ideal for applications where timing is crucial.

When working with TTL systems, it is important to choose CMOS types that are compatible with TTL logic levels, such as the ACT or S/AS86 families. These families are optimized for interfacing with TTL and ensure that the performance of the XOR gates aligns with the requirements of the surrounding circuitry. Caution should be exercised when considering low-power TTL versions like LS or ALS, as their inherent propagation delays can lead to timing issues, particularly when different types of XOR gates are used in the same circuit. The disparities in delay can result in signal misalignment, which is detrimental to the operation of high-speed systems.

In conclusion, the choice of XOR gates and their configuration is paramount in applications requiring precise signal timing and integrity. Selecting the appropriate logic family based on the specific requirements of the system will enhance performance and reliability in high-speed digital applications.Some applications, such as driving three-state buffers for data multiplexers or for biphase clocks in high-speed systems, require complementary signals having a small-time skew and nearly simultaneous transitions. Here, XOR gates function as both inverting and noninverting gates. For CMOS systems, practically any type of XOR gate will work. However, the advanced-CMOS logic (ACL) families have the greatest drive capability, the shortest gate delays, and the tightest manufacturing tolerances. For TTL systems, compatible CMOS types such as the ACT or S/AS86 families are preferable. Do not use low-power TTL versions (LS or ALS), because they have large propagation delay differences when one XOR gate is inverting and the other is noninverting.

In high-speed digital circuits, the requirement for complementary signals with minimal skew and nearly simultaneous transitions is critical for maintaining signal integrity and performance. The use of XOR gates in this scenario is advantageous, as they can function as both inverting and non-inverting logic elements, providing flexibility in circuit design.

For CMOS systems, the variety of available XOR gates allows for compatibility across different designs, but selecting advanced-CMOS logic (ACL) families is particularly beneficial due to their superior characteristics. ACL families are designed to handle higher drive currents, which is essential for driving loads in high-speed applications. Additionally, their reduced gate delays contribute to improved overall system performance, making them ideal for applications where timing is crucial.

When working with TTL systems, it is important to choose CMOS types that are compatible with TTL logic levels, such as the ACT or S/AS86 families. These families are optimized for interfacing with TTL and ensure that the performance of the XOR gates aligns with the requirements of the surrounding circuitry. Caution should be exercised when considering low-power TTL versions like LS or ALS, as their inherent propagation delays can lead to timing issues, particularly when different types of XOR gates are used in the same circuit. The disparities in delay can result in signal misalignment, which is detrimental to the operation of high-speed systems.

In conclusion, the choice of XOR gates and their configuration is paramount in applications requiring precise signal timing and integrity. Selecting the appropriate logic family based on the specific requirements of the system will enhance performance and reliability in high-speed digital applications.Some applications, such as driving three-state buffers for data multiplexers or for biphase clocks in high-speed systems, require complementary signals having a small-time skew and nearly simultaneous transitions. Here, XOR gates function as both inverting and noninverting gates. For CMOS systems, practically any type of XOR gate will work. However, the advanced-CMOS logic (ACL) families have the greatest drive capability, the shortest gate delays, and the tightest manufacturing tolerances. For TTL systems, compatible CMOS types such as the ACT or S/AS86 families are preferable. Do not use low-power TTL versions (LS or ALS), because they have large propagation delay differences when one XOR gate is inverting and the other is noninverting.