13.8V 20A power supply

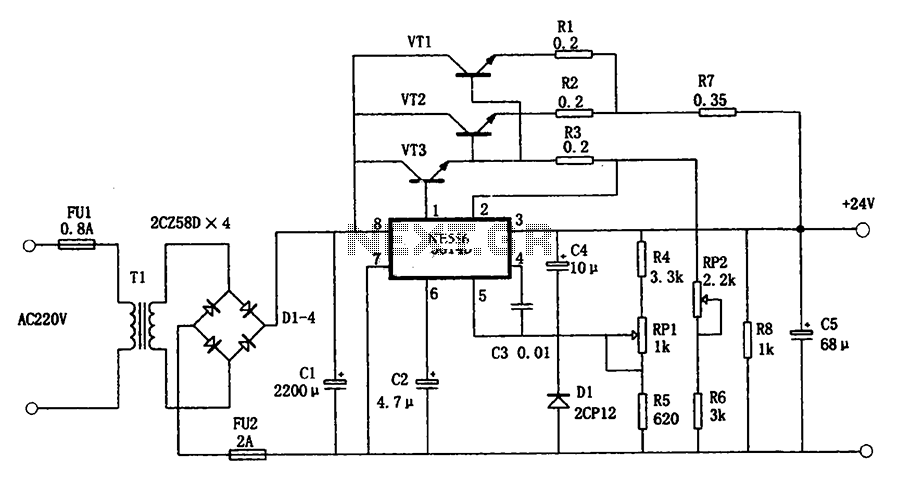

The circuit safely delivers approximately 20 Amps at 13.8V. For lower current applications, a separate current limiting output capable of 15mA up to a total of 20A has been included. The power transformer should be able to supply at least 25A at a voltage range of 17.5V to 20V. Lowering the voltage reduces power dissipation. The rectified current will be smoothed by capacitor C1, which should have a capacitance of no less than 40,000μF (a general guideline is around 2000μF per Amp), although a value up to 50,000μF is recommended. This capacitance can be achieved by paralleling several smaller capacitors. The core of this design is a standard 12V regulator (7812). The output voltage can be adjusted to the desired level (in this case, 13.8V) using two external resistors (R5 and R6) according to a specific formula. Low currents (15mA) will maintain the 7812 in its normal operation. When the current exceeds 15mA, the voltage drop across resistor R4 will activate transistor Q3, which is responsible for managing the high output current. Q3 is a PNP transistor (Ic > 25) with a current gain of at least 20; the tested model is the 2N5683. The current limiting resistor RL, designed for a maximum output of 20 Amps, should be 0.03 Ohms and rated for at least 15W. This can be constructed using resistance wire or by connecting multiple resistors in parallel to achieve the desired resistance and power ratings. For different current levels, values can be calculated based on established rules. RL and Q2 (a 3A PNP transistor such as BD330) function as an automatic fuse. When the current reaches 20 Amps, the voltage drop across RL will turn on Q2, limiting the base-emitter current of Q3. Parallel to Q2 is Q1, which activates LED1 whenever the current limiting circuit is engaged. When the fuse is active, Q2 bypasses R3, allowing full current to flow through IC1, which could cause damage. R4 is included to limit the current to IC1 to 15mA, enabling it to operate without additional cooling. LED2 illuminates whenever the power supply unit (PSU) is powered on. This circuit is straightforward, and there is no explicit current sensing resistor; instead, the Rds-on resistance of the N-channel FET serves this purpose, controlling load disconnection from the source. The operation of the FET is illustrated in diagram 2. As the current Id increases, the voltage Uds across the Rds resistance initially rises slowly but accelerates rapidly after a certain threshold. Before this threshold, the FET behaves like a resistor; beyond it, it acts as a constant current source. The components D2, R3, and the base-emitter connection of Q4 detect the Uds voltage of FET1. When the voltage surpasses a critical level, Q4 will ground the gate of FET1, interrupting current flow. A specific gate voltage is required to turn FET1 on, established by the voltage divider formed by R8, Z1, P1, and R9. The maximum gate voltage corresponds to Z1's voltage, while the minimum is approximately 3.6V. The Z1 voltage (Uz1) thus dictates the maximum current through FET1. Diagram 2 indicates that for 5 Amps, Uz1 should be 5.6V, and for 20 Amps, it should be around 9.6V. Capacitor C4 influences the response time of the limiter; a value of 100μF results in a reaction time of about 100ms, while 1nF leads to a response time of 1μs. Within the designed parameters, P1 will regulate the output current between 15mA and 20A. Both outputs can be utilized simultaneously, but the total output current will be constrained by the value of RL. This power supply unit can be scaled for higher outputs, provided the transformer can accommodate the current demands and adequate cooling is supplied for Q3.It delivers safely around 20Amps at 13. 8V. For lower currents, a separate current limiting output, capable of 15ma up to a total of 20A has been added. Let us see what we have got here. The power transformer should be capable to deliver at least 25A at 17. 5 to 20V. Th e lower the voltage, the lower power dissipation. The rectified current will be ironed by the C1, whose capacity should not be less than 40. 000uF, (a golden rule of around 2000uF/A), but we recommend up to 50. 000uF. This capacity can be built up by several smaller capacitors in parallel. The base of this design is a simple 12V regulator (7812). The output voltage can be brought to desired value (here 13. 8V) by two external resistors (R5 and R6) using this formula: The low currents (here 15mA) will keep the 7812 in its regular function. As soon as the current rises over 15ma, the voltage drop on R4 will open the Q3, actually handling the high output current.

This is a PNP transistor (Ic>25) and current amplification factor of at least 20. The one that has been tested and proven here is the 2N5683. The current limiting resistance RL, for the maximum output of 20 Amps should be 0. 03 Ohms, rated at least 15W. You can use the resistance wire or switch several resistors in parallel, totaling the resistance/power values. Values for other currents can be calculated by the rule: The RL and Q2 (3A PNP such as BD330) form a short circuit automatic fuse .

As soon as the maximum current reaches 20Amps, the voltage drop over the resistor RL will open Q2, and thus limit the B-E Current of Q3. Parallel to Q2 is Q1, which lights the LED 1 whenever the current limiting circuit is active. When the fuse is active, the Q2 bridges the R3, so the full current would flow through the IC1, and damage it.

Therefore the R4 is inserted, as to limit the IC1 current to 15mA. This makes it possible to run the IC1 without any cooling aid. The LED 2 will light up every time the PSU is switched on. This circuit is very simple too. You will notice that there is no current sensing resistor. But it is really there, in a form of the Rds-on resistance of the N-channel FET, which actually handles the load cutoff from the source. The function of the FET is shown in the diagram 2. When the current Id is rising, the tension Uds over the resistance Rds rises very slowly in the beginning, but very fast after the knick.

This means, that before the knick the FET behaves as a resistor but after it, works as constant current source. The D2, R3 and B-E connection of the Q4 will sense the Uds voltage of the FET1. When the voltage rises enough, the Q4 will shortcut the FET1 gate to mass, and cut the current flow through the FET 1 off.

However, to enable the FET1 to open, there is certain gate voltage necessary, which in this case is brought up by the voltage divider consisting of R8, Z1, P1 and R9. So the maximum Gate voltage will be the one of the Z1, and the minimal will be around 3V6. The Z1 voltage (Uz1) will thus determine the max current flowing through the FET 1. The diagram 2 will show that for 5 Amps the Uz1 should be 5V6, and for 20Amps around 9V6. The Capacitor C4 will determine the velocity or the reaction time of the limiter. 100 uF will make the reaction time to be around 100ms, and 1n will make it 1us. Within the designed limits, the P1 will limit the current output in the range of 15mA to 20A. You can use both output simultaneously, but the total output current will be limited by the value of the RL.

This PSU can be built also for higher outputs, as long as the transformer will handle the current requirements, and you provide sufficient cooling for the Q3. 🔗 External reference

This is a PNP transistor (Ic>25) and current amplification factor of at least 20. The one that has been tested and proven here is the 2N5683. The current limiting resistance RL, for the maximum output of 20 Amps should be 0. 03 Ohms, rated at least 15W. You can use the resistance wire or switch several resistors in parallel, totaling the resistance/power values. Values for other currents can be calculated by the rule: The RL and Q2 (3A PNP such as BD330) form a short circuit automatic fuse .

As soon as the maximum current reaches 20Amps, the voltage drop over the resistor RL will open Q2, and thus limit the B-E Current of Q3. Parallel to Q2 is Q1, which lights the LED 1 whenever the current limiting circuit is active. When the fuse is active, the Q2 bridges the R3, so the full current would flow through the IC1, and damage it.

Therefore the R4 is inserted, as to limit the IC1 current to 15mA. This makes it possible to run the IC1 without any cooling aid. The LED 2 will light up every time the PSU is switched on. This circuit is very simple too. You will notice that there is no current sensing resistor. But it is really there, in a form of the Rds-on resistance of the N-channel FET, which actually handles the load cutoff from the source. The function of the FET is shown in the diagram 2. When the current Id is rising, the tension Uds over the resistance Rds rises very slowly in the beginning, but very fast after the knick.

This means, that before the knick the FET behaves as a resistor but after it, works as constant current source. The D2, R3 and B-E connection of the Q4 will sense the Uds voltage of the FET1. When the voltage rises enough, the Q4 will shortcut the FET1 gate to mass, and cut the current flow through the FET 1 off.

However, to enable the FET1 to open, there is certain gate voltage necessary, which in this case is brought up by the voltage divider consisting of R8, Z1, P1 and R9. So the maximum Gate voltage will be the one of the Z1, and the minimal will be around 3V6. The Z1 voltage (Uz1) will thus determine the max current flowing through the FET 1. The diagram 2 will show that for 5 Amps the Uz1 should be 5V6, and for 20Amps around 9V6. The Capacitor C4 will determine the velocity or the reaction time of the limiter. 100 uF will make the reaction time to be around 100ms, and 1n will make it 1us. Within the designed limits, the P1 will limit the current output in the range of 15mA to 20A. You can use both output simultaneously, but the total output current will be limited by the value of the RL.

This PSU can be built also for higher outputs, as long as the transformer will handle the current requirements, and you provide sufficient cooling for the Q3. 🔗 External reference