A simple way of phase locking microwave local oscillators

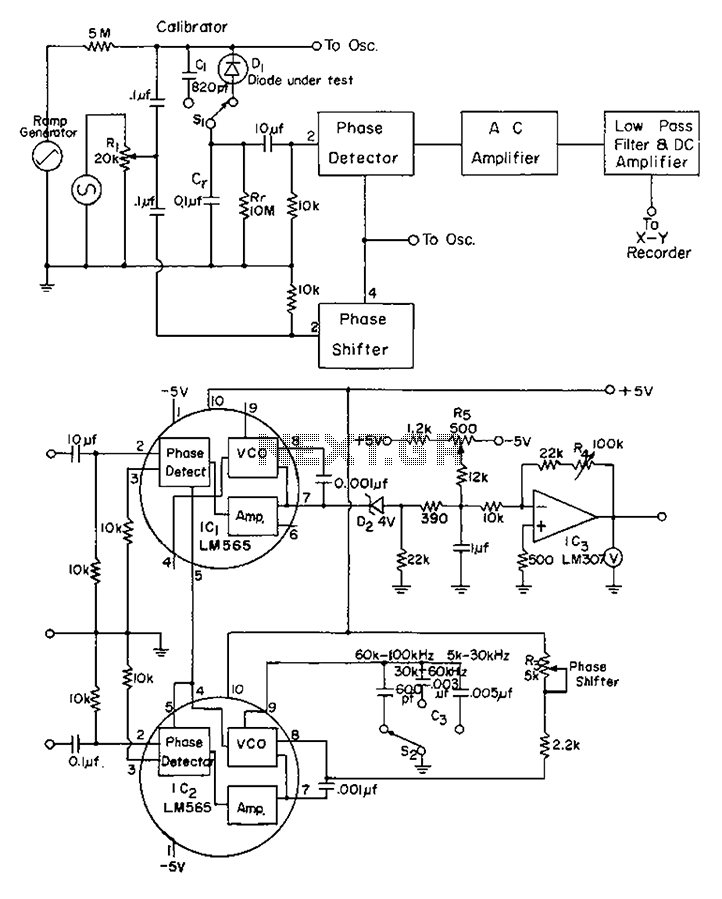

The circuit serves as a foundational design, requiring experimentation for specific applications. In popular microwave bands, local oscillators (LOs) are typically generated using overtone crystal oscillators followed by multipliers. A table presents the standard LO frequencies for narrowband segments, along with the corresponding crystal frequencies. The final columns indicate the highest frequency that is a submultiple of both the LO and a 10 MHz reference, the highest common factor (HCF), and the associated division. This HCF can serve as the comparison frequency in a phase-locked loop (PLL), representing the maximum frequency achievable in this context. All comparison frequencies can be derived from a 10 MHz reference using simple logic divider chips to implement the divide-by-R function (which could also originate from a 2 MHz signal). All comparison frequencies exceed 200 kHz, allowing for PLLs with wide loop bandwidths. For those marked with an asterisk, higher comparison frequencies are feasible, but the stated values maintain frequencies within a narrower design band. The primary challenge is providing the divide-by-N function from the crystal frequency. An off-the-shelf synthesizer chip, such as the MC145170 or alternatives from other manufacturers, can simplify this process, although a more straightforward solution exists with some additional adjustments and optimization. Those familiar with the brick range of microwave sources will recognize how a high-Q cavity oscillator is locked to a reference oscillator in the 100 MHz range using a sampling phase detector. This device integrates the functions of frequency multiplication and phase detection within a single network. In these designs, a snap varactor diode is driven by approximately 200 mW of reference signal, generating sharp sub-nanosecond pulses. These pulses are applied across a pair of microwave diodes, forming one input to a single balanced mixer, while a portion of the cavity oscillator signal is fed into the other RF port via a small probe. This sampling mixer approach simplifies PLL design by eliminating the need for a high-frequency divide-by-N circuit, albeit with two significant drawbacks. First, the voltage-controlled oscillator (VCO) can lock to any harmonic of the reference, which is mitigated in brick designs by limiting the electrical tuning range of the VCO to less than half the comparison frequency—sometimes allowing only a pull-in range of 5 to 10 MHz at the fundamental L-band frequency. Second, the output from the phase detector is at a low level, typically a few tens of millivolts per radian, compared to the 1.6 V/radian of standard logic. Consequently, the full voltage range available for drive power is distributed across all comb frequencies. However, a low-noise operational amplifier can easily provide the necessary DC gains, and a differential amplifier performing this function within the bricks is visible upon removing the side cover. This concept can also be applied at lower frequencies to lock a voltage-controlled crystal oscillator (VCXO), where the restricted tuning range of crystal oscillators mitigates the first drawback. The circuit in Figure 1 illustrates a two-chip R divider, programmable for any value from 1 to 256, generating the reference signal. This reference is then applied to an impulse generator utilizing the propagation delay inherent in three high-speed logic gates, along with an additional component.

The described circuit utilizes a combination of overtone crystal oscillators and multipliers to generate local oscillator frequencies suitable for microwave applications. The design emphasizes the use of a 10 MHz reference signal, which facilitates the derivation of various comparison frequencies through logic divider chips. The high common factor (HCF) derived from the LO and reference frequencies plays a crucial role in establishing the PLL's comparison frequency, ensuring that all operational frequencies remain above 200 kHz, thus allowing for robust PLL performance.

The implementation of a sampling phase detector within the circuit enables the integration of frequency multiplication and phase detection, streamlining the design process. By applying sharp pulses generated from a varactor diode to a balanced mixer, the circuit can effectively lock the VCO to the desired reference frequency. The design also addresses potential challenges related to harmonic locking by constraining the tuning range of the VCO, which is particularly advantageous when working with lower frequencies and VCXOs.

Furthermore, the use of operational amplifiers to amplify the low-level output from the phase detector ensures adequate drive power is available for the circuit's subsequent stages. The programmable R divider enhances flexibility, allowing for precise frequency adjustments to meet specific application requirements. Overall, this circuit exemplifies a sophisticated approach to microwave frequency generation and phase locking, suitable for various electronic applications.The circuit is presented as a starting point - there will be some experimentation needed for each individual case. For the popular microwave bands the LOs are usually generated from overtone crystal oscillators followed by multipliers, with the following table showing the usual LO frequencies for the narrowband segments along with the associated crystal frequency.

The final columns show the highest frequency that is a submultiple of both this and a 10MHz reference, the highest common factor or HCF, and the associated division. This HCF can become the comparison frequency in a phase locked loop, and is the highest frequency that is possible here.

All the comparison frequencies can be derived from a 10MHz reference by making use of simple logic divider chips to give the divide by R function (all could be derived from 2MHz in fact) All the comparison frequencies are over 200kHz, so phase locked loops can be made with wide loop bandwidths. For those marked with a *, an even higher comparison frequency is possible, but the values stated keep the frequencies within a narrower band for a common design.

So now the only difficulty is providing the divide by N from the crystal frequency. An off the shelf synthesiser chip such as the MC145170, or those from other manufacturers, would make an easy job of this but there is an even simpler solution providing you are prepared to do a bit more adjustment and optimisation. Anyone who has studied the brick` range of microwave sources will have seen how a high Q cavity oscillator is locked to a reference oscillator in the 100MHz region by a sampling phase detector.

This device combines the functions of frequency multiplier and phase in one network. In the bricks, a snap varactor diode is hit with about 200mW of reference signal and so generates sharp sub-nanosecond pulses at this rate. These pulses are applied across a pair of microwave diodes, forming one input to a single balanced mixer whose other RF ports is fed with a portion of the cavity oscillator signal picked off via a small probe.

This sampling mixer approach to PLL design makes for considerable simplicity as it inherently removes any need for a high frequency divide by N circuit - but has two major drawbacks. Firstly, the VCO can lock to ANY harmonic of the reference, and in the brick designs this is prevented by restricting the electrical tuning range of the VCO to less than half of the comparison frequency - sometimes a pull in range of only 5 - 10MHz (at the fundamental L-Band frequency) can be observed.

Secondly, the output from the phase detector is at a very low level - typically a few tens of millivolts per radian rather than the 1. 6V/radian of normal logic. In effect, the complete voltage range that would have been possible for the drive power is having to be shared over every one of the comb frequencies.

However, a low noise op-amp can easily provide DC gains of the hundred or so required here, and differential amp doing this job inside the bricks is clearly visible when the side cover is removed. So, lets try this idea at lower frequencies to lock a VCXO - the very restricted tuning range of crystal oscillators means that drawback 1 is not an issue.

Look at the circuit of Figure 1, a two chip R divider (programmable for any value from 1 to 256) generates the reference. This is applied to an impulse generator using the propagation delay inherent in three high speed logic gates plus an addit

🔗 External reference

The described circuit utilizes a combination of overtone crystal oscillators and multipliers to generate local oscillator frequencies suitable for microwave applications. The design emphasizes the use of a 10 MHz reference signal, which facilitates the derivation of various comparison frequencies through logic divider chips. The high common factor (HCF) derived from the LO and reference frequencies plays a crucial role in establishing the PLL's comparison frequency, ensuring that all operational frequencies remain above 200 kHz, thus allowing for robust PLL performance.

The implementation of a sampling phase detector within the circuit enables the integration of frequency multiplication and phase detection, streamlining the design process. By applying sharp pulses generated from a varactor diode to a balanced mixer, the circuit can effectively lock the VCO to the desired reference frequency. The design also addresses potential challenges related to harmonic locking by constraining the tuning range of the VCO, which is particularly advantageous when working with lower frequencies and VCXOs.

Furthermore, the use of operational amplifiers to amplify the low-level output from the phase detector ensures adequate drive power is available for the circuit's subsequent stages. The programmable R divider enhances flexibility, allowing for precise frequency adjustments to meet specific application requirements. Overall, this circuit exemplifies a sophisticated approach to microwave frequency generation and phase locking, suitable for various electronic applications.The circuit is presented as a starting point - there will be some experimentation needed for each individual case. For the popular microwave bands the LOs are usually generated from overtone crystal oscillators followed by multipliers, with the following table showing the usual LO frequencies for the narrowband segments along with the associated crystal frequency.

The final columns show the highest frequency that is a submultiple of both this and a 10MHz reference, the highest common factor or HCF, and the associated division. This HCF can become the comparison frequency in a phase locked loop, and is the highest frequency that is possible here.

All the comparison frequencies can be derived from a 10MHz reference by making use of simple logic divider chips to give the divide by R function (all could be derived from 2MHz in fact) All the comparison frequencies are over 200kHz, so phase locked loops can be made with wide loop bandwidths. For those marked with a *, an even higher comparison frequency is possible, but the values stated keep the frequencies within a narrower band for a common design.

So now the only difficulty is providing the divide by N from the crystal frequency. An off the shelf synthesiser chip such as the MC145170, or those from other manufacturers, would make an easy job of this but there is an even simpler solution providing you are prepared to do a bit more adjustment and optimisation. Anyone who has studied the brick` range of microwave sources will have seen how a high Q cavity oscillator is locked to a reference oscillator in the 100MHz region by a sampling phase detector.

This device combines the functions of frequency multiplier and phase in one network. In the bricks, a snap varactor diode is hit with about 200mW of reference signal and so generates sharp sub-nanosecond pulses at this rate. These pulses are applied across a pair of microwave diodes, forming one input to a single balanced mixer whose other RF ports is fed with a portion of the cavity oscillator signal picked off via a small probe.

This sampling mixer approach to PLL design makes for considerable simplicity as it inherently removes any need for a high frequency divide by N circuit - but has two major drawbacks. Firstly, the VCO can lock to ANY harmonic of the reference, and in the brick designs this is prevented by restricting the electrical tuning range of the VCO to less than half of the comparison frequency - sometimes a pull in range of only 5 - 10MHz (at the fundamental L-Band frequency) can be observed.

Secondly, the output from the phase detector is at a very low level - typically a few tens of millivolts per radian rather than the 1. 6V/radian of normal logic. In effect, the complete voltage range that would have been possible for the drive power is having to be shared over every one of the comb frequencies.

However, a low noise op-amp can easily provide DC gains of the hundred or so required here, and differential amp doing this job inside the bricks is clearly visible when the side cover is removed. So, lets try this idea at lower frequencies to lock a VCXO - the very restricted tuning range of crystal oscillators means that drawback 1 is not an issue.

Look at the circuit of Figure 1, a two chip R divider (programmable for any value from 1 to 256) generates the reference. This is applied to an impulse generator using the propagation delay inherent in three high speed logic gates plus an addit

🔗 External reference