AD1865 based audio DAC with I2S input and voltage output

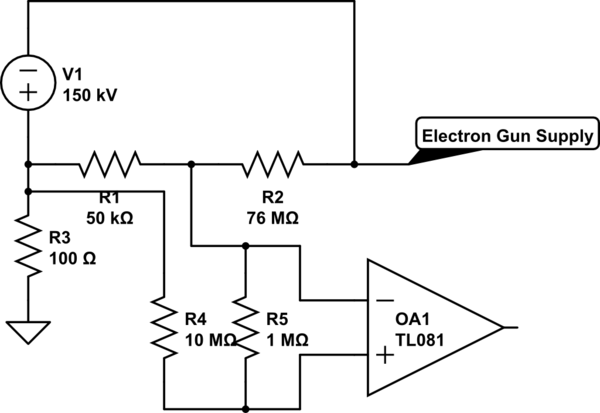

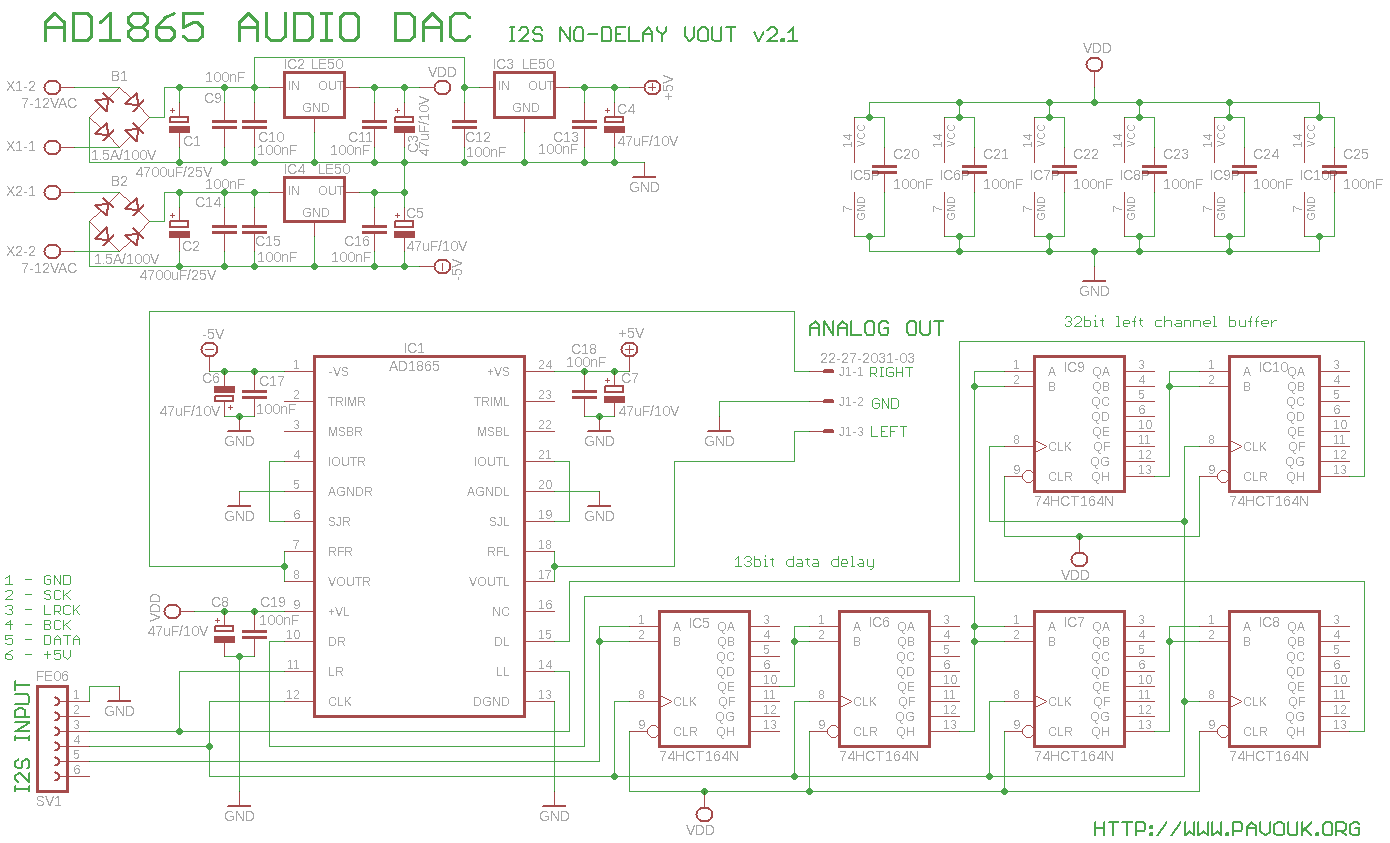

The AD1865 circuit is regarded as one of the best 18-bit stereo audio DACs available. Previous DAC designs encountered issues with weak current output, leading to the decision to utilize the integrated current-to-voltage (I/V) converter instead of an external one. The DAC lacks a data buffer, resulting in alternate output from the left and right channels, which can theoretically introduce a phase shift. The intention is to connect the DAC to a USB receiver that outputs only I2S data. The circuit design addresses these challenges. It requires two separate windings from a power transformer, as a positive voltage regulator is used for the negative supply branch. After rectification through diodes B1 and B2, filter capacitors C1 and C2 are employed, followed by a group of block capacitors. Low-drop voltage regulators (LE50) are utilized: one for the digital section and two for the positive and negative analog sections of the DAC. Small filter and blocking capacitors are placed near the regulators and integrated circuits. The DAC does not support I2S input, which is common; instead, it has individual data inputs for each channel along with separate "latch" inputs that transfer data from an internal register to the DAC output. I2S formatted data (left justified) is delayed by 13 bits, ensuring that after shifting the 18 most significant bits to the DAC register, they are written to the output. To achieve simultaneous playback of both channels, the left channel data is delayed by 32 clock cycles (the frame length for a single channel). Consequently, data for both channels is shifted together into the DAC and written to the output with a shared latch signal. The lack of a 32-bit shift register presented two options: creating one using Xilinx technology or assembling one from commonly available 8-bit shift registers. The latter was preferred to avoid the complexity of a register train; however, a prototype with a CMOS 64-bit register (CD4517) failed due to incompatible logic levels. Ultimately, the solution involved using several 74HCT164 shift registers, which provide a 13-bit delay function and a 32-bit register for the left channel data. The final result exceeded expectations, with the DAC functioning correctly for signals up to 192 kHz/24-bit, corresponding to a clock frequency of 12.288 MHz. The voltage output of the DAC reaches +/-3V at maximum deflection, which is sufficient for most amplifiers, while the output remains at zero otherwise, with a minimal DC offset of a few millivolts. If necessary, the output can be decoupled with a high-quality capacitor to address any offset issues. No filters are present on the output to limit frequency, as it is anticipated that filtering will occur in subsequent audio chain components such as amplifiers, speakers, and the human ear. The PCB assembly process involves starting with SMD capacitors, followed by wire connections. Soldering is performed using a small soldering iron and 0.5 mm diameter solder. In case of an emergency, a transformer soldering iron and larger solder can be utilized. If pads are inadvertently connected, excess solder can be removed using solder wick. The ICs (IC5 to IC10) and small capacitors are installed from the top side, followed by voltage regulators, connectors, rectifiers, the DAC, and finally, larger capacitors. The PCB is designed as a single-sided board with four wire junctions, facilitating assembly in amateur conditions. SMD components are placed on the bottom side, while wired components and connectors are on the top side. Supply wires are designed with a focus on proper grounding and the junction of analog and digital grounds at a single point. Block capacitors are positioned close to the circuits. The PCB includes four mounting holes for screws. The design process was challenging due to the high component count, but ultimately, all components fit onto a relatively small board with only four wire connections. After the DAC was built, minor modifications were made to the board to eliminate digital noise observed on one of the analog outputs. Ground traces were adjusted accordingly.Circuit AD1865 is considered like best 18bit stereo audio DAC ever. I already built another DAC, that I will not say everything again. However I found, that current output is too weak and instead of using external I/V converter I used this, what is included in DAC. Because DAC doesn`t have buffer for data, that both channels was not on the output simultaneously, but alternately left and right channel. This can produce theoretically hearable phase-shift. Last I want to connect DAC to USB receiver with only I2S data output. All troubles solve following circuit. Supplying need two separated windings on power transformer, because I used positive voltage regulator for negative supply branch. After rectifiers B1 and B2 are filter capacitors C1 and C2 and behind them group of block capacitors.

I used available low-drop voltage regulators LE50. One is for supplying of digital part and two are for positive and negative analog part of dac. Closely to regulators and integrated circuits are small filter and blocking capacitors. DAC doesn`t have I2S input, which is usual. It has individual data inputs for left and right channel and individual "latch" inputs which rewrites data from internal register to DAC output. Input data in I2S format (left justified) are first delayed for 13 bits thus that after shifting of 18 most significant bits to the dac register they will be written to output.

For simultaneous playing of left and right channel we must delay data of left channel for 32 clocks (frame lenght for one channel). Result is that data for left and right channel are shifted together to the dac and they are written to the output with common latch signal.

Because there doesn`t exists 32bit shift-register I had two choices. Create them with help of Xilinx, but I have not experience with it or assemble them from easily available 8bit shift-registers. I wanted to avoid variant with registers train. However prototype with CMOS 64bit register CD4517 doesn`t work thanks to different logic levels. On the end I had to use plenty of 74HCT164 which have 13 bits delay function and 32 bit register for left channel data.

Result exceeded my expectations and DAC is fully functional for signals up to 192kHz/24bit which is 12. 288MHz clock frequency. This time I choose voltage DAC output. Output has +/-3V at maximum deflection which must be enough for every amplifier. In rest is zero on the output. Respectively there can be small DC offset few milivolts. Output can be direct-current separated with high quality capacitor if offset matter. There are no one filter on the output limiting frequency. I count with filtering in next parts of audio chain like amplifier, speaker and ear. We assemble PCB from smaller parts to bigger. We begins with SMD capacitors and next with wire wraps. Circuits we can solder with small soldering iron and small 0. 5mm tube tin. In case of emergency we can use transformer soldering iron and bigger tin. When some of pads will be connected together, we can exhaust overflowing tin with solder wick. Next I installed IC5 to IC10 and small capacitors from top side and next voltage regulators, connectors, rectifiers, dac and last big capacitors.

PCB is designed single sided with four wire junctions. It help as to make them in amateur conditions. SMD parts are from a bottom side and parts with wires and connectors are from a top side. Supply wires are designed with accent on right ground wiring and junction of analog and digital ground in a one point. Block capacitors are very close to circuits. PCB has four assembling holes for mounting with screws. Design of this board was this time difficult thanks to big number of parts, but finally all components was on the pretty small board with only four wire connections.

After build of DAC I had to slightly modify board, because there was small digital noise visible on oscilloscope on one of the analog outputs. Now there are ground trac 🔗 External reference

I used available low-drop voltage regulators LE50. One is for supplying of digital part and two are for positive and negative analog part of dac. Closely to regulators and integrated circuits are small filter and blocking capacitors. DAC doesn`t have I2S input, which is usual. It has individual data inputs for left and right channel and individual "latch" inputs which rewrites data from internal register to DAC output. Input data in I2S format (left justified) are first delayed for 13 bits thus that after shifting of 18 most significant bits to the dac register they will be written to output.

For simultaneous playing of left and right channel we must delay data of left channel for 32 clocks (frame lenght for one channel). Result is that data for left and right channel are shifted together to the dac and they are written to the output with common latch signal.

Because there doesn`t exists 32bit shift-register I had two choices. Create them with help of Xilinx, but I have not experience with it or assemble them from easily available 8bit shift-registers. I wanted to avoid variant with registers train. However prototype with CMOS 64bit register CD4517 doesn`t work thanks to different logic levels. On the end I had to use plenty of 74HCT164 which have 13 bits delay function and 32 bit register for left channel data.

Result exceeded my expectations and DAC is fully functional for signals up to 192kHz/24bit which is 12. 288MHz clock frequency. This time I choose voltage DAC output. Output has +/-3V at maximum deflection which must be enough for every amplifier. In rest is zero on the output. Respectively there can be small DC offset few milivolts. Output can be direct-current separated with high quality capacitor if offset matter. There are no one filter on the output limiting frequency. I count with filtering in next parts of audio chain like amplifier, speaker and ear. We assemble PCB from smaller parts to bigger. We begins with SMD capacitors and next with wire wraps. Circuits we can solder with small soldering iron and small 0. 5mm tube tin. In case of emergency we can use transformer soldering iron and bigger tin. When some of pads will be connected together, we can exhaust overflowing tin with solder wick. Next I installed IC5 to IC10 and small capacitors from top side and next voltage regulators, connectors, rectifiers, dac and last big capacitors.

PCB is designed single sided with four wire junctions. It help as to make them in amateur conditions. SMD parts are from a bottom side and parts with wires and connectors are from a top side. Supply wires are designed with accent on right ground wiring and junction of analog and digital ground in a one point. Block capacitors are very close to circuits. PCB has four assembling holes for mounting with screws. Design of this board was this time difficult thanks to big number of parts, but finally all components was on the pretty small board with only four wire connections.

After build of DAC I had to slightly modify board, because there was small digital noise visible on oscilloscope on one of the analog outputs. Now there are ground trac 🔗 External reference