Attaching a GPS module to the EB675001DIP

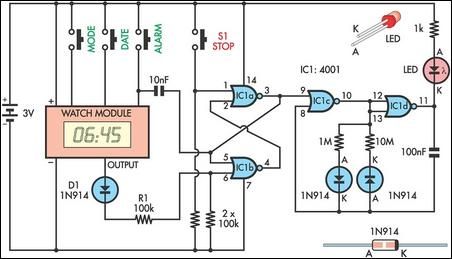

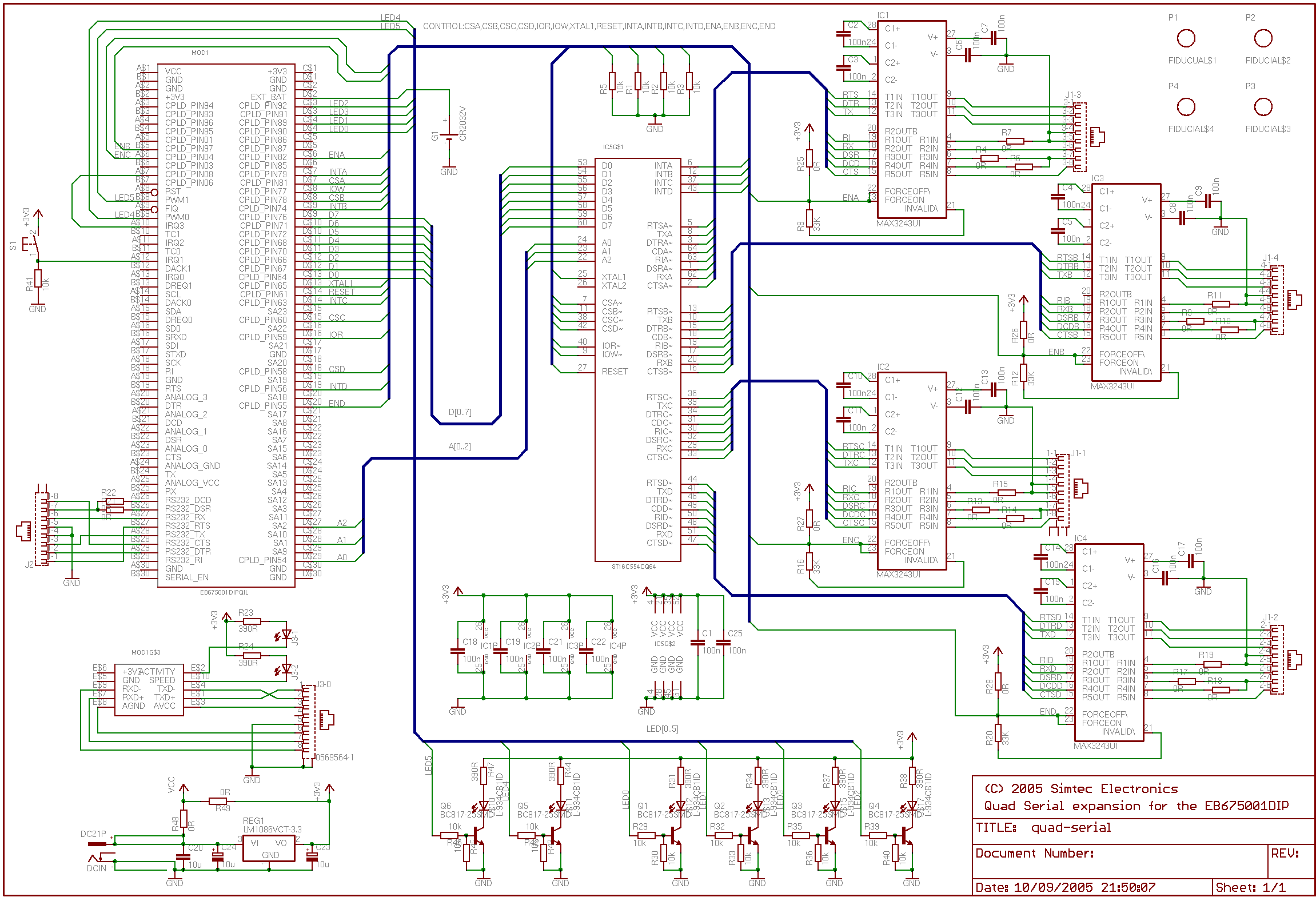

The CPLD in this design is utilized solely for interfacing with the LCD module, employing the same code as outlined in the application note for connecting an LCD module to the EB675001DIP. Communication with the GPS module is facilitated through CLinux, utilizing the ttyS0 serial port configured to 4800 baud, with 8 data bits, no parity, and 1 stop bit (4800, 8N1). It is the user's responsibility to ensure that the application meets their specifications. Simtec Electronics assumes no liability regarding the accuracy or use of this information, nor for any infringement of patents or other intellectual property rights that may arise.

The CPLD (Complex Programmable Logic Device) serves as a crucial component in this electronic design, primarily functioning to create a seamless interface between the LCD module and the rest of the system. The design employs a pre-existing codebase that has been validated in the context of the EB675001DIP application note, ensuring reliability and compatibility with the LCD module.

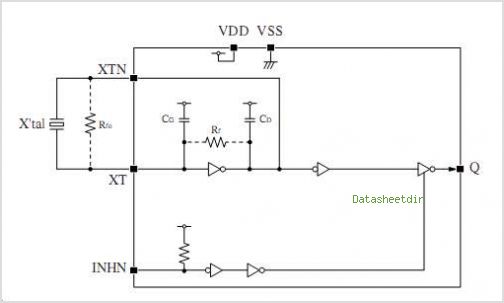

The communication protocol established with the GPS module utilizes the CLinux operating system, which is adept at managing serial communications. The ttyS0 serial port is configured to operate at a baud rate of 4800, which is a standard speed for many GPS modules, ensuring reliable data transmission. The parameters of 8 data bits, no parity, and 1 stop bit (often referred to as 8N1) are standard settings that facilitate effective communication by defining the structure of the data packets being sent and received.

In terms of circuit design, the CPLD's role may involve managing the timing and control signals necessary for the LCD module to function correctly, including data transfer and display updates. The integration of the GPS module through the serial port requires careful attention to signal integrity and timing to ensure accurate data retrieval and processing.

The user's responsibility to meet application specifications emphasizes the importance of thorough testing and validation of the entire system to ensure that all components, including the CPLD, LCD, and GPS module, work harmoniously together without errors. This consideration is critical in applications where precision and reliability are paramount.

Lastly, the disclaimer from Simtec Electronics highlights the need for users to conduct their due diligence in application development, particularly regarding intellectual property rights and the accuracy of the information provided. This serves as a reminder that while the design and components may be well-documented, the ultimate responsibility for compliance and functionality lies with the user.The user CPLD is only used in this design to interface the LCD module and is the same code as used in the Attaching an LCD module to the EB675001DIP application note. CLinux was used to communicate with the GPS module. Communication is simply achieved using the ttyS0 serial port set to 4800 baud, 8 data bits no parity and 1 stop bit (4800, 8N1).

It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Simtec Electronics with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. 🔗 External reference

The CPLD (Complex Programmable Logic Device) serves as a crucial component in this electronic design, primarily functioning to create a seamless interface between the LCD module and the rest of the system. The design employs a pre-existing codebase that has been validated in the context of the EB675001DIP application note, ensuring reliability and compatibility with the LCD module.

The communication protocol established with the GPS module utilizes the CLinux operating system, which is adept at managing serial communications. The ttyS0 serial port is configured to operate at a baud rate of 4800, which is a standard speed for many GPS modules, ensuring reliable data transmission. The parameters of 8 data bits, no parity, and 1 stop bit (often referred to as 8N1) are standard settings that facilitate effective communication by defining the structure of the data packets being sent and received.

In terms of circuit design, the CPLD's role may involve managing the timing and control signals necessary for the LCD module to function correctly, including data transfer and display updates. The integration of the GPS module through the serial port requires careful attention to signal integrity and timing to ensure accurate data retrieval and processing.

The user's responsibility to meet application specifications emphasizes the importance of thorough testing and validation of the entire system to ensure that all components, including the CPLD, LCD, and GPS module, work harmoniously together without errors. This consideration is critical in applications where precision and reliability are paramount.

Lastly, the disclaimer from Simtec Electronics highlights the need for users to conduct their due diligence in application development, particularly regarding intellectual property rights and the accuracy of the information provided. This serves as a reminder that while the design and components may be well-documented, the ultimate responsibility for compliance and functionality lies with the user.The user CPLD is only used in this design to interface the LCD module and is the same code as used in the Attaching an LCD module to the EB675001DIP application note. CLinux was used to communicate with the GPS module. Communication is simply achieved using the ttyS0 serial port set to 4800 baud, 8 data bits no parity and 1 stop bit (4800, 8N1).

It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Simtec Electronics with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. 🔗 External reference