FSK Demodulator

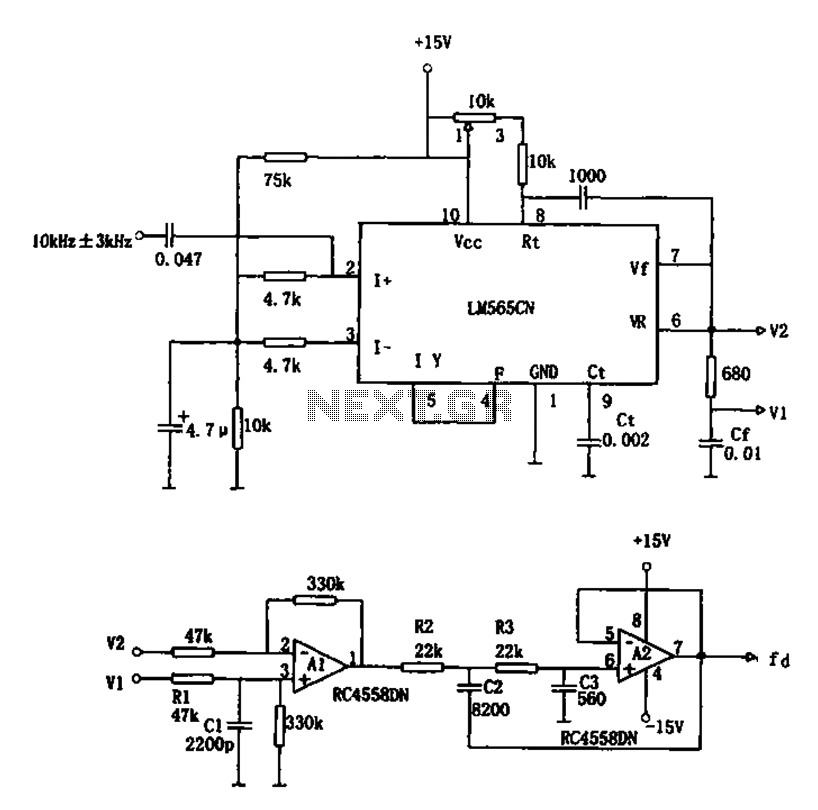

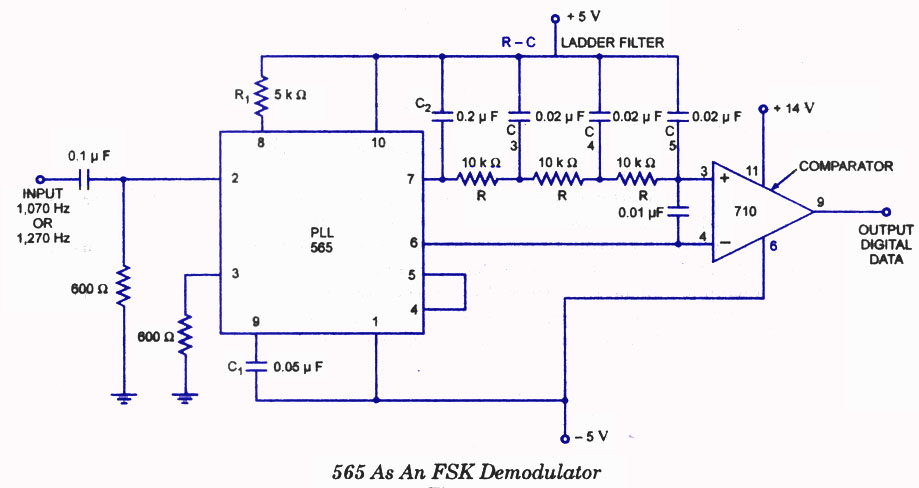

A highly effective application of the 565 Phase-Locked Loop (PLL) is its use as a Frequency Shift Keying (FSK) demodulator. In the 565 PLL, frequency shifting is typically achieved by driving a Voltage-Controlled Oscillator (VCO) with a binary data signal, resulting in two frequencies that correspond to the logic 0 and logic 1 states of the binary data signal. These frequencies are commonly referred to as mark and space frequencies. Various standards are established to define the mark and space frequencies. An FSK signal demodulator can be constructed as depicted in the corresponding figure. The demodulator receives a signal at one of the two distinct carrier frequencies, 1,270 Hz or 1,070 Hz, which represent the RS-232 C logic levels of mark (-5 V) or space (+14 V), respectively. Capacitive coupling is utilized at the input to eliminate a DC level. When the signal is applied to the input of the 565 PLL, the PLL locks onto the input frequency and tracks it between the two possible frequencies, producing a corresponding DC shift at the output. Resistor R1 and capacitor C1 set the free-running frequency of the VCO. Capacitor C2 serves as a loop filter capacitor that defines the dynamic characteristics of the demodulator. C2 is selected to be smaller than typical values to prevent overshoot on the output pulse. A three-stage RC ladder filter is used to remove the sum frequency component from the output. The VCO frequency is adjusted using R1 to ensure that the DC voltage level at the output (pin 7) matches that at pin 6. An input frequency of 1,070 Hz increases the demodulator output voltage to a higher positive level, resulting in a digital output at a high level (space or +14 V). Conversely, an input at 1,270 Hz reduces the 565 DC output to a less positive voltage, causing the digital output to drop to a low level (mark or -5 V).

The 565 PLL FSK demodulator circuit operates by utilizing the phase-locked loop mechanism to synchronize with the incoming FSK signal. The VCO's output frequency is modulated based on the input binary data, which effectively translates the frequency variations into corresponding voltage levels. The use of capacitive coupling at the input stage is critical for blocking any DC bias that may affect the demodulation process, allowing only the AC components of the FSK signal to pass through.

The choice of R1 and C1 is integral to the proper functioning of the VCO. These components determine the free-running frequency, ensuring that the VCO can adequately track the incoming FSK signal. Capacitor C2, being smaller than typical values, is essential for achieving fast response times and minimizing overshoot, thereby enhancing the fidelity of the demodulated output.

The three-stage RC ladder filter plays a vital role in signal processing by attenuating unwanted frequency components, specifically the sum frequency that can arise during demodulation. This filtering ensures that the output signal remains clean and representative of the original binary data.

In summary, the 565 PLL demodulator is a sophisticated yet effective solution for decoding FSK signals. Its design optimally balances the need for responsiveness, accuracy, and signal integrity, making it suitable for applications requiring reliable data transmission and reception.A very useful application of the 565 PLL is as a FSK demodulator. In the 565 PLL the frequency shift is usually accomplished by driving a VCO with the binary data signal so that the two resulting frequencies corre spond to the logic 0 and logic 1 states of the binary data signal. The frequencies corresponding to logic 1 and logic 0 states are com monly called the mark and space frequencies. Several standards are used to set the mark and space frequencies. An FSK signal demodulator can be built as illustrated in figure. The demodulator receives a signal at one of the two distinct carrier frequencies, 1, 270 Hz or 1, 070 Hz representing the RS-232 C logic levels of mark (- 5 V) or space (+ 14 V), respectively. Capacitance coupling is used at the input to remove a dc level. As the signal appears at the input of 565 PLL, the PLL locks to the input frequency and tracks it between the two possible frequencies with a corresponding dc shift at the output.

Resistor R1 and capacitor C1 determine the free-running frequency of the VCO. Capacitor C2 is a loop filter capacitor that establishes the dynamic characteristics of the demodulator. Capacitor C2 is chosen smaller than usual one to eliminate overshoot on the output pulse. A three-stage RC ladder filter is employed for removing the sum frequency component from the output. The VCO frequency is adjusted with R1 so that the dc voltage level at the output (pin 7) is the same as that at pin 6.

An input at frequency 1, 070 Hz drives the demodulator output voltage to a more positive voltage level, driving the digital output to the high level (space or + 14 V). An input at 1, 270 Hz correspondingly drives the 565 dc output less positive with the digital output, which then drops to the low level (mark or 5 V).

🔗 External reference

The 565 PLL FSK demodulator circuit operates by utilizing the phase-locked loop mechanism to synchronize with the incoming FSK signal. The VCO's output frequency is modulated based on the input binary data, which effectively translates the frequency variations into corresponding voltage levels. The use of capacitive coupling at the input stage is critical for blocking any DC bias that may affect the demodulation process, allowing only the AC components of the FSK signal to pass through.

The choice of R1 and C1 is integral to the proper functioning of the VCO. These components determine the free-running frequency, ensuring that the VCO can adequately track the incoming FSK signal. Capacitor C2, being smaller than typical values, is essential for achieving fast response times and minimizing overshoot, thereby enhancing the fidelity of the demodulated output.

The three-stage RC ladder filter plays a vital role in signal processing by attenuating unwanted frequency components, specifically the sum frequency that can arise during demodulation. This filtering ensures that the output signal remains clean and representative of the original binary data.

In summary, the 565 PLL demodulator is a sophisticated yet effective solution for decoding FSK signals. Its design optimally balances the need for responsiveness, accuracy, and signal integrity, making it suitable for applications requiring reliable data transmission and reception.A very useful application of the 565 PLL is as a FSK demodulator. In the 565 PLL the frequency shift is usually accomplished by driving a VCO with the binary data signal so that the two resulting frequencies corre spond to the logic 0 and logic 1 states of the binary data signal. The frequencies corresponding to logic 1 and logic 0 states are com monly called the mark and space frequencies. Several standards are used to set the mark and space frequencies. An FSK signal demodulator can be built as illustrated in figure. The demodulator receives a signal at one of the two distinct carrier frequencies, 1, 270 Hz or 1, 070 Hz representing the RS-232 C logic levels of mark (- 5 V) or space (+ 14 V), respectively. Capacitance coupling is used at the input to remove a dc level. As the signal appears at the input of 565 PLL, the PLL locks to the input frequency and tracks it between the two possible frequencies with a corresponding dc shift at the output.

Resistor R1 and capacitor C1 determine the free-running frequency of the VCO. Capacitor C2 is a loop filter capacitor that establishes the dynamic characteristics of the demodulator. Capacitor C2 is chosen smaller than usual one to eliminate overshoot on the output pulse. A three-stage RC ladder filter is employed for removing the sum frequency component from the output. The VCO frequency is adjusted with R1 so that the dc voltage level at the output (pin 7) is the same as that at pin 6.

An input at frequency 1, 070 Hz drives the demodulator output voltage to a more positive voltage level, driving the digital output to the high level (space or + 14 V). An input at 1, 270 Hz correspondingly drives the 565 dc output less positive with the digital output, which then drops to the low level (mark or 5 V).

🔗 External reference