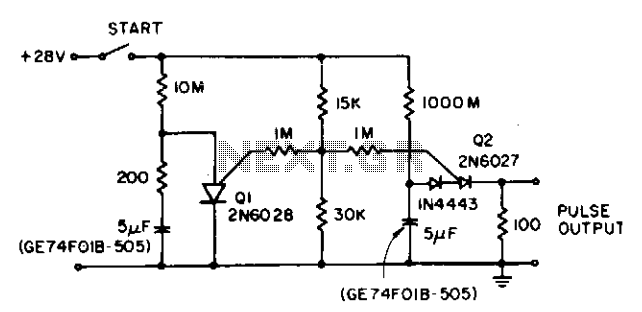

Hour time-delay sampling circuit

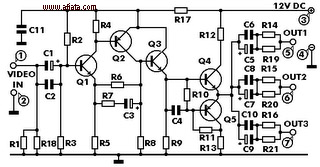

The circuit reduces the effective peak current of the output PUT, Q2. It allows the capacitor to charge with a high gate voltage and periodically lowers the gate voltage. When Q1 fires, the timing resistor can be set to a value that supplies a significantly lower current than IP. The triggering requirement is that there must be a minimum charge to initiate current flow through the timing resistor during the period of the Q1 oscillator. This behavior is not dependent on the size of the capacitor, but rather on the leakage and stability of the capacitor.

The described circuit employs a Programmable Unijunction Transistor (PUT) as the primary output switching device (Q2). The operation of this circuit hinges on the controlled charging and discharging of a capacitor, which is connected to the gate of the PUT. Initially, a high gate voltage is applied, allowing the capacitor to charge rapidly. This charging phase is crucial as it sets the stage for the subsequent operation of the circuit.

Once the capacitor reaches a certain voltage threshold, the gate voltage is periodically reduced. This reduction is essential as it influences the firing of the PUT (Q2). When Q1, which functions as an oscillator, fires, it creates a pulse that allows the timing resistor to regulate the current flowing through the circuit. The value of the timing resistor is critical; it must be chosen such that it limits the current to a level significantly lower than the peak current (IP). This design choice is important for protecting the circuit components from excessive current that could lead to failure.

The triggering mechanism relies on ensuring that the capacitor maintains a minimum charge during the oscillation period of Q1. This minimum charge is necessary to allow current to flow through the timing resistor, thus enabling the circuit to function as intended. The performance of the circuit is influenced not by the size of the capacitor but by its leakage characteristics and stability over time. High leakage can lead to insufficient charge retention, while instability can affect the timing and reliability of the circuit operation.

In summary, this circuit effectively manages the output current through careful control of the capacitor's charging and discharging cycles, utilizing the characteristics of the PUT and the timing resistor to achieve desired operational parameters.The circuit lowers the effective peak current of the output PUT, Q2. By allowing the capacitor to charge with high gate voltage and periodically lowering gate voltage, when Ql fires, the timing resistor can be a value which supplies a much lower current than IP. The triggering requirement here is that minimum charge to trigger flow through the timing resistor during the period of the Ql oscillator.

This is not capacitor size dependent, only capacitor leakage and stability dependent.

The described circuit employs a Programmable Unijunction Transistor (PUT) as the primary output switching device (Q2). The operation of this circuit hinges on the controlled charging and discharging of a capacitor, which is connected to the gate of the PUT. Initially, a high gate voltage is applied, allowing the capacitor to charge rapidly. This charging phase is crucial as it sets the stage for the subsequent operation of the circuit.

Once the capacitor reaches a certain voltage threshold, the gate voltage is periodically reduced. This reduction is essential as it influences the firing of the PUT (Q2). When Q1, which functions as an oscillator, fires, it creates a pulse that allows the timing resistor to regulate the current flowing through the circuit. The value of the timing resistor is critical; it must be chosen such that it limits the current to a level significantly lower than the peak current (IP). This design choice is important for protecting the circuit components from excessive current that could lead to failure.

The triggering mechanism relies on ensuring that the capacitor maintains a minimum charge during the oscillation period of Q1. This minimum charge is necessary to allow current to flow through the timing resistor, thus enabling the circuit to function as intended. The performance of the circuit is influenced not by the size of the capacitor but by its leakage characteristics and stability over time. High leakage can lead to insufficient charge retention, while instability can affect the timing and reliability of the circuit operation.

In summary, this circuit effectively manages the output current through careful control of the capacitor's charging and discharging cycles, utilizing the characteristics of the PUT and the timing resistor to achieve desired operational parameters.The circuit lowers the effective peak current of the output PUT, Q2. By allowing the capacitor to charge with high gate voltage and periodically lowering gate voltage, when Ql fires, the timing resistor can be a value which supplies a much lower current than IP. The triggering requirement here is that minimum charge to trigger flow through the timing resistor during the period of the Ql oscillator.

This is not capacitor size dependent, only capacitor leakage and stability dependent.