Low power timer switch

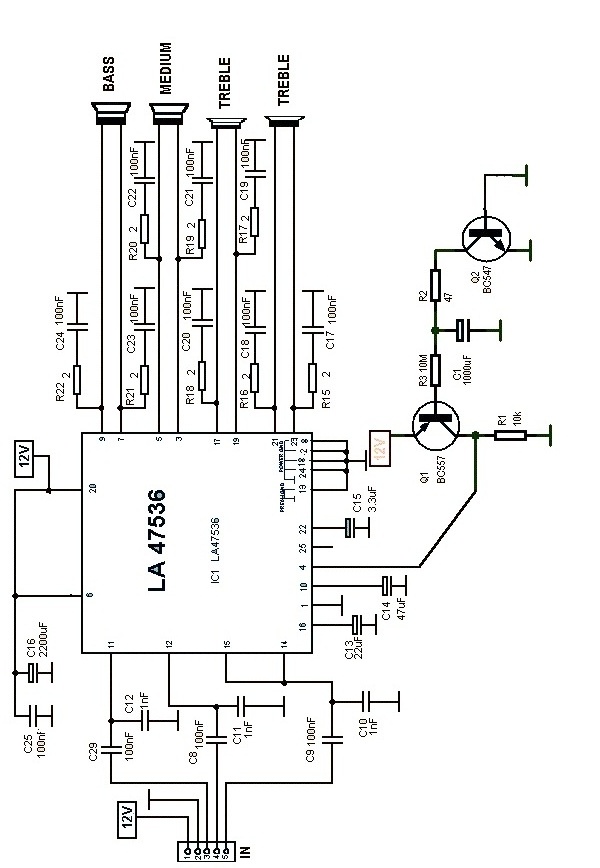

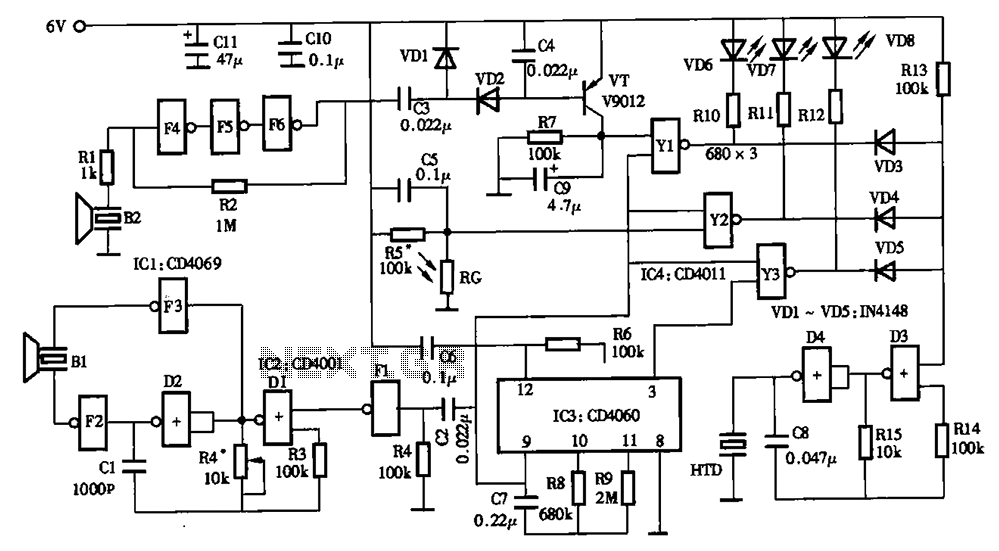

The timing circuit utilizes an electronic switch composed of F1, F2, and VT1 to reduce quiescent current to approximately 1 to 2 A with the 555 timer. Upon initial power-up, the voltage across capacitor C2 cannot instantly change, causing the gate of F2 to go high, which results in F1 locking in a low output state and turning off VT1. This configuration minimizes the quiescent current of the entire circuit. When the timer switch AN is pressed, a negative pulse is applied to the input of F1, causing its output to go high and activating VT1, which supplies power to the 555 timer. Simultaneously, the negative pulse is applied to pin 2 of the 555 timer, setting it and initiating the timing cycle. The timing period, td, is determined by the formula td = 1.1 * R4 * C3, where the timing can be adjusted by changing the values of resistor R4 and capacitor C3.

The timing circuit described operates effectively by leveraging the characteristics of the 555 timer in conjunction with discrete electronic components. The use of F1 and F2 as electronic switches allows for a significant reduction in quiescent current, enhancing the efficiency of the circuit during idle states. The operation begins with the application of power, at which point capacitor C2 remains uncharged, preventing immediate changes in voltage. This leads to F2 achieving a high state, which in turn locks F1 in a low state, effectively disabling the output of VT1 and minimizing current draw.

When the timer switch AN is engaged, it introduces a negative pulse to the input of F1. This pulse is critical as it triggers F1 to switch to a high output state, thereby activating VT1. Consequently, the 555 timer receives its supply voltage, enabling its operational capabilities. The application of the negative pulse to pin 2 of the 555 timer is equally important, as it sets the timer into motion, commencing the timing cycle.

The duration of the timing cycle, represented by td, is directly influenced by the components R4 and C3. The formula td = 1.1 * R4 * C3 indicates that the timing period can be extended or reduced by varying either the resistance of R4 or the capacitance of C3. This flexibility allows for customization of the timing circuit to suit various applications, making it a versatile solution for timing-related tasks in electronic designs. As shown, the timing circuit due to the installation of the electronic switch by the F1, F2 and VT1 composed of quiescent current can be reduced to 555 l ~ 2 A. When the power is first turned on, since the voltage on C2 can not jump, so F2 gate goes high, F1 to lock in a low output potential, VT1 off, so that the quiescent current of the entire circuit is small. When you press the timer switch AN, F1 input of a negative pulse appears, F1 output goes high, VT conduction, only the supply voltage 555.

At the same time, due to the negative pulse is applied to 555 feet 2, 555 set, K Pull, the timer starts. Timing td 1.1R4C3. Timing can be changed by adjusting the length of the time constant R4C3 of.

The timing circuit described operates effectively by leveraging the characteristics of the 555 timer in conjunction with discrete electronic components. The use of F1 and F2 as electronic switches allows for a significant reduction in quiescent current, enhancing the efficiency of the circuit during idle states. The operation begins with the application of power, at which point capacitor C2 remains uncharged, preventing immediate changes in voltage. This leads to F2 achieving a high state, which in turn locks F1 in a low state, effectively disabling the output of VT1 and minimizing current draw.

When the timer switch AN is engaged, it introduces a negative pulse to the input of F1. This pulse is critical as it triggers F1 to switch to a high output state, thereby activating VT1. Consequently, the 555 timer receives its supply voltage, enabling its operational capabilities. The application of the negative pulse to pin 2 of the 555 timer is equally important, as it sets the timer into motion, commencing the timing cycle.

The duration of the timing cycle, represented by td, is directly influenced by the components R4 and C3. The formula td = 1.1 * R4 * C3 indicates that the timing period can be extended or reduced by varying either the resistance of R4 or the capacitance of C3. This flexibility allows for customization of the timing circuit to suit various applications, making it a versatile solution for timing-related tasks in electronic designs. As shown, the timing circuit due to the installation of the electronic switch by the F1, F2 and VT1 composed of quiescent current can be reduced to 555 l ~ 2 A. When the power is first turned on, since the voltage on C2 can not jump, so F2 gate goes high, F1 to lock in a low output potential, VT1 off, so that the quiescent current of the entire circuit is small. When you press the timer switch AN, F1 input of a negative pulse appears, F1 output goes high, VT conduction, only the supply voltage 555.

At the same time, due to the negative pulse is applied to 555 feet 2, 555 set, K Pull, the timer starts. Timing td 1.1R4C3. Timing can be changed by adjusting the length of the time constant R4C3 of.