low power universal demultiplexer decoder

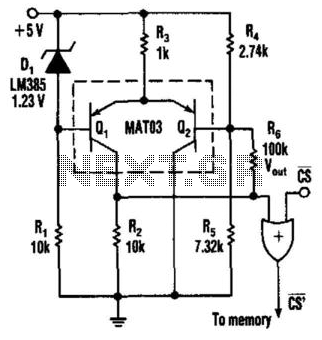

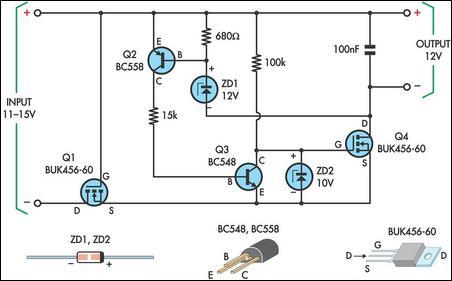

This circuit functions as a universal decoder, capable of operating either as a dual 1-of-4 decoder or as a single 1-of-8 decoder, depending on the signal applied to the Mode Control (M) input. In the dual mode, each section features a pair of active-LOW Enable (E) inputs. The pin assignments for the E inputs allow them to be easily connected in pairs in 1-of-8 mode, enabling two active-LOW enables (E1a to E1b, E2a to E2b). The auxiliary inputs Ha, Hb, and Hc control whether the outputs are active HIGH or active LOW. In dual 1-of-4 mode, the Address inputs are A0a, A1a, A0b, and A1b, with A2a left unused (either open, tied to VEE, or connected to a LOW signal). In the 1-of-8 mode, the Address inputs consist of A0a, A1a, and A2a, while A0b and A1b remain LOW or open. All inputs are equipped with 50 kΩ pull-down resistors.

The universal decoder circuit is designed to provide versatile functionality for various digital applications by allowing the selection between a dual or single decoding mode. In the dual 1-of-4 mode, each decoder section operates independently, providing four outputs based on the binary inputs A0 and A1. The active-LOW enable inputs ensure that the outputs are only activated when the corresponding enable signal is LOW, allowing for controlled operation in multi-device environments.

In the single 1-of-8 mode, the decoder combines the two sections into one, allowing for eight outputs based on three binary inputs (A0, A1, A2). The configuration of the inputs allows for a straightforward design where the outputs can be easily interfaced with other digital components. The inclusion of pull-down resistors on all inputs minimizes the risk of floating states, ensuring stable operation.

The circuit's adaptability makes it suitable for applications in data routing, multiplexing, and digital signal processing, where different modes of operation are required based on the system's needs. The design supports efficient use of space and resources, making it an ideal choice for integrated circuit implementations.This is a circuit for universal decoder that has functions as either a dual 1-of-4 decoder or as a single 1-of-8 decoder, depending on the signal applied to the Mode Control (M) input. Here`s the figure of the test circuit; In the dual mode, each half has a pair of active-LOW Enable (E) inputs.

Pin assignments for the E inputs are such that in the 1-of-8 mode they can easily be tied together in pairs to provide two active-LOW enables (E1a to E1b, E2a to E2b). Signals applied to auxiliary inputs Ha, Hb and Hc determine whether the outputs are active HIGH or active LOW.

In the dual 1-of-4 mode the Address inputs are A0a, A1a and A0b, A1b with A2a unused (i. e. , left open, tied to VEE or with LOW signal applied). In the 1-of-8 mode, the Address inputs are A0a, A1a, A2a with A0b and A1b LOW or open. All inputs have 50 kX pull down resistors. [Circuit diagram source: National Semiconductor Application Notes] 🔗 External reference

The universal decoder circuit is designed to provide versatile functionality for various digital applications by allowing the selection between a dual or single decoding mode. In the dual 1-of-4 mode, each decoder section operates independently, providing four outputs based on the binary inputs A0 and A1. The active-LOW enable inputs ensure that the outputs are only activated when the corresponding enable signal is LOW, allowing for controlled operation in multi-device environments.

In the single 1-of-8 mode, the decoder combines the two sections into one, allowing for eight outputs based on three binary inputs (A0, A1, A2). The configuration of the inputs allows for a straightforward design where the outputs can be easily interfaced with other digital components. The inclusion of pull-down resistors on all inputs minimizes the risk of floating states, ensuring stable operation.

The circuit's adaptability makes it suitable for applications in data routing, multiplexing, and digital signal processing, where different modes of operation are required based on the system's needs. The design supports efficient use of space and resources, making it an ideal choice for integrated circuit implementations.This is a circuit for universal decoder that has functions as either a dual 1-of-4 decoder or as a single 1-of-8 decoder, depending on the signal applied to the Mode Control (M) input. Here`s the figure of the test circuit; In the dual mode, each half has a pair of active-LOW Enable (E) inputs.

Pin assignments for the E inputs are such that in the 1-of-8 mode they can easily be tied together in pairs to provide two active-LOW enables (E1a to E1b, E2a to E2b). Signals applied to auxiliary inputs Ha, Hb and Hc determine whether the outputs are active HIGH or active LOW.

In the dual 1-of-4 mode the Address inputs are A0a, A1a and A0b, A1b with A2a unused (i. e. , left open, tied to VEE or with LOW signal applied). In the 1-of-8 mode, the Address inputs are A0a, A1a, A2a with A0b and A1b LOW or open. All inputs have 50 kX pull down resistors. [Circuit diagram source: National Semiconductor Application Notes] 🔗 External reference