MAX8632 PCB Layout Optimization

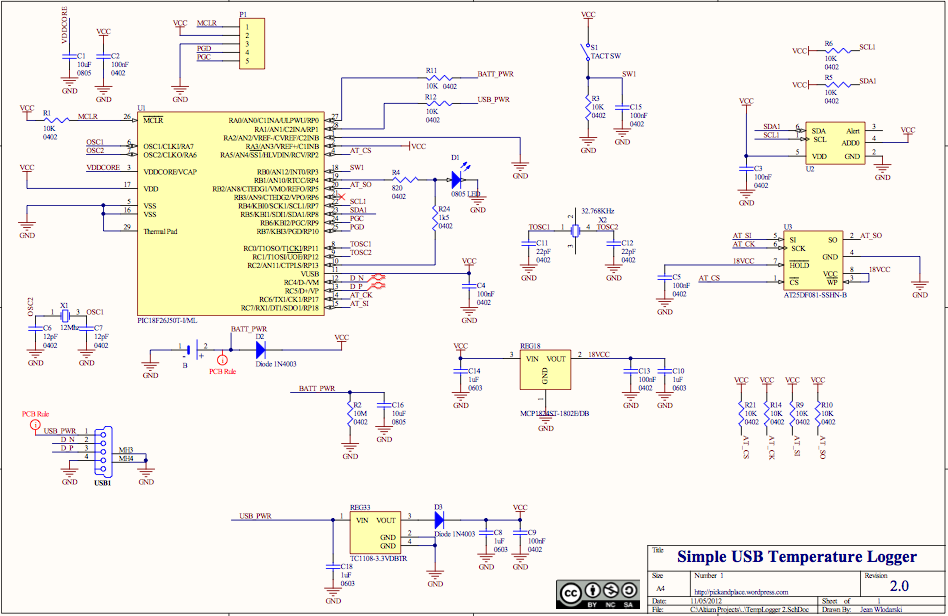

This document presents a well-defined printed circuit board layout for the implementation of the MAX8632 Integrated DDR Power Supply. The MAX8632 chip serves as a comprehensive DDR power supply solution, employing a synchronous buck controller to produce the VDDQ main rail. Additionally, it features a high-speed 3 Amp Low Drop-Out (LDO) regulator capable of sourcing and sinking current to generate the VTT bus termination, along with a 15mA VTTR reference buffer.

The MAX8632 Integrated DDR Power Supply is designed to efficiently deliver power to DDR memory modules, ensuring stable operation under varying load conditions. The synchronous buck controller is pivotal in achieving high efficiency during the conversion of input voltage to the VDDQ rail, which typically operates at voltages required by DDR memory, such as 1.5V or lower. This efficiency is crucial for minimizing thermal dissipation and enhancing overall system reliability.

The 3 Amp LDO regulator included in the MAX8632 architecture provides additional functionality by generating the VTT bus termination voltage, which is essential for maintaining signal integrity in DDR systems. This regulator can both source and sink current, allowing it to adapt to the dynamic load requirements of the DDR memory. The ability to sink current is particularly important during read operations, where the memory may draw current from the termination voltage.

Furthermore, the 15mA VTTR reference buffer serves as a stable reference voltage for the termination bus, ensuring that the VTT voltage remains consistent and within specified limits. This stability is critical for minimizing voltage fluctuations that could lead to data corruption or memory instability.

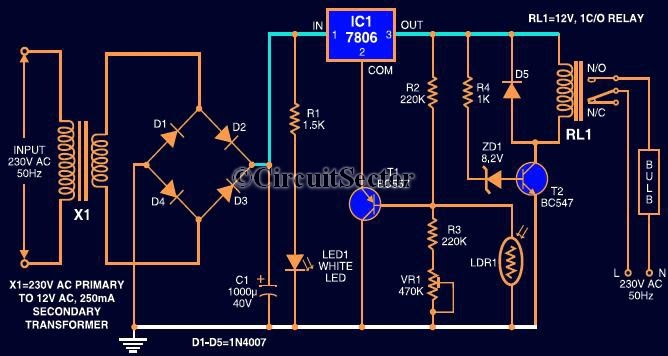

In terms of PCB layout, careful attention must be paid to the placement of components to minimize noise and optimize performance. The power traces should be designed to handle the load currents while minimizing inductance, and decoupling capacitors should be placed close to the power pins of the MAX8632 to ensure effective filtering of high-frequency noise. Ground planes should be utilized to provide a low-resistance return path, enhancing the overall performance of the power supply circuit.

This comprehensive design approach ensures that the MAX8632 Integrated DDR Power Supply operates effectively in a wide range of applications, delivering reliable power to DDR memory systems while adhering to strict performance and efficiency standards.This paper outlines a clear printed circuit board layout for implementation of the MAX8632 Integrated DDR Power Supply. This chip functions as an integrated DDR Power-Supply Solution that utilizes a synchronous-buck controller to generate VDDQ main rail, a 3 Amp high speed LDO (Low Drop Out) regulator that can source and sink current to generate VTT bus termination and a 15mA VTTR reference buffer..

🔗 External reference

The MAX8632 Integrated DDR Power Supply is designed to efficiently deliver power to DDR memory modules, ensuring stable operation under varying load conditions. The synchronous buck controller is pivotal in achieving high efficiency during the conversion of input voltage to the VDDQ rail, which typically operates at voltages required by DDR memory, such as 1.5V or lower. This efficiency is crucial for minimizing thermal dissipation and enhancing overall system reliability.

The 3 Amp LDO regulator included in the MAX8632 architecture provides additional functionality by generating the VTT bus termination voltage, which is essential for maintaining signal integrity in DDR systems. This regulator can both source and sink current, allowing it to adapt to the dynamic load requirements of the DDR memory. The ability to sink current is particularly important during read operations, where the memory may draw current from the termination voltage.

Furthermore, the 15mA VTTR reference buffer serves as a stable reference voltage for the termination bus, ensuring that the VTT voltage remains consistent and within specified limits. This stability is critical for minimizing voltage fluctuations that could lead to data corruption or memory instability.

In terms of PCB layout, careful attention must be paid to the placement of components to minimize noise and optimize performance. The power traces should be designed to handle the load currents while minimizing inductance, and decoupling capacitors should be placed close to the power pins of the MAX8632 to ensure effective filtering of high-frequency noise. Ground planes should be utilized to provide a low-resistance return path, enhancing the overall performance of the power supply circuit.

This comprehensive design approach ensures that the MAX8632 Integrated DDR Power Supply operates effectively in a wide range of applications, delivering reliable power to DDR memory systems while adhering to strict performance and efficiency standards.This paper outlines a clear printed circuit board layout for implementation of the MAX8632 Integrated DDR Power Supply. This chip functions as an integrated DDR Power-Supply Solution that utilizes a synchronous-buck controller to generate VDDQ main rail, a 3 Amp high speed LDO (Low Drop Out) regulator that can source and sink current to generate VTT bus termination and a 15mA VTTR reference buffer..

🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713