Tone-alert decoder

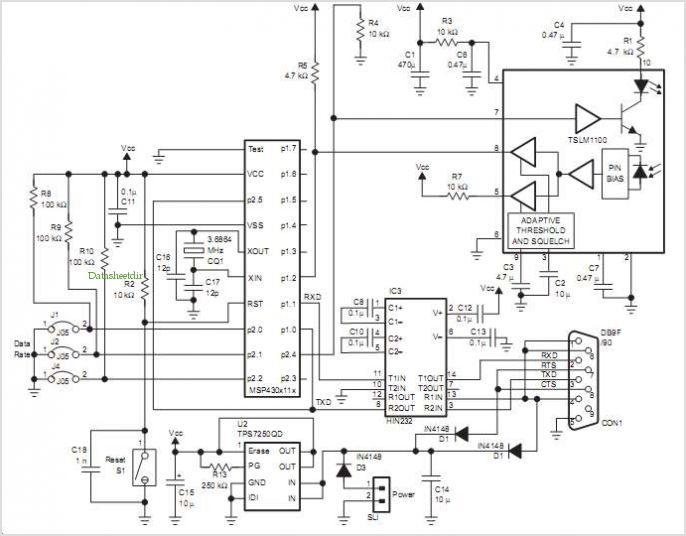

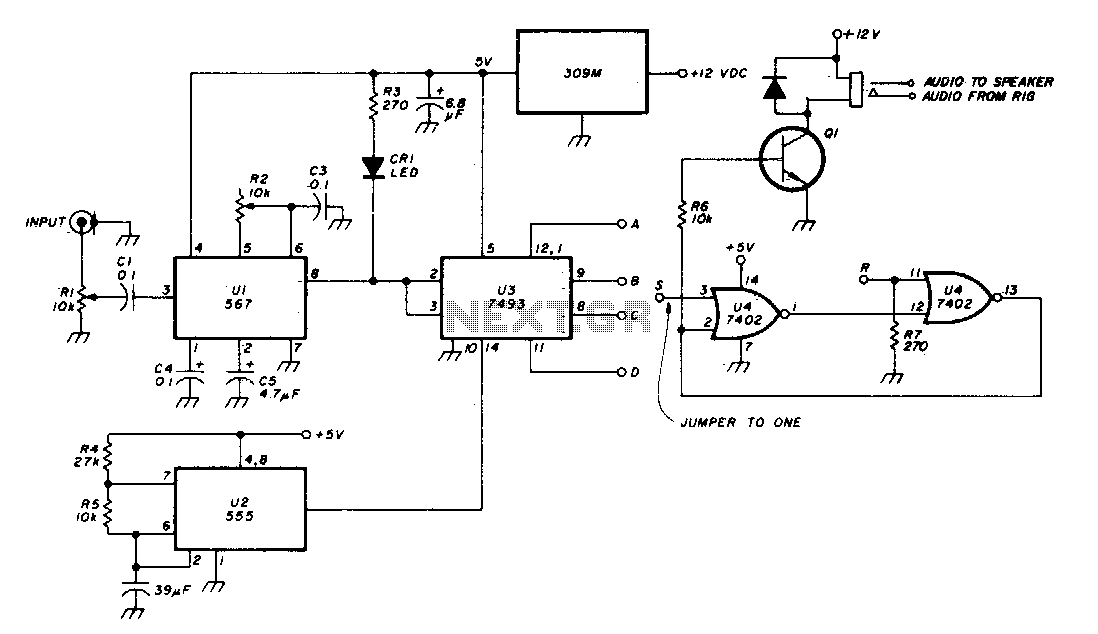

The Phase-Locked Loop (PLL) integrated circuit (U1) is configured with resistor R2 to achieve the desired tone frequency. An LED indicator is used to show when the PLL has locked onto the signal. To ensure proper lock-up, the signal level is reduced using resistor R1, and R2 is readjusted as necessary. The delay is determined by the output of counter U3. The circuit latches by activating transistor Q1, which allows audio to be sent to the speaker when the correct frequency and duration signal is detected. To reset the latch, a brief positive voltage must be applied to the R input of U4.

The described circuit utilizes a Phase-Locked Loop (PLL) mechanism to maintain synchronization with a reference signal, which is crucial for applications requiring precise frequency control, such as audio signal processing. The PLL circuit is configured with an external resistor (R2) that sets the frequency of operation. The LED indicator serves as a visual confirmation of the PLL's lock status, which is essential for troubleshooting and operational verification.

To fine-tune the PLL's frequency locking, the circuit incorporates a feedback loop where the signal level is adjusted using resistor R1. This adjustment process ensures that the PLL can lock onto the desired frequency reliably. The output from counter U3 provides a timing signal that introduces a delay, allowing for the stabilization of the PLL before activating the audio output.

The activation of transistor Q1 is a critical function of the circuit, as it controls the flow of audio signals to the speaker. The latch mechanism ensures that audio is only output when the PLL has achieved the correct frequency and duration, preventing unwanted noise or signal artifacts from reaching the speaker.

For reset functionality, the circuit design includes a provision to apply a temporary positive voltage to the R input of U4. This reset action is necessary for reinitializing the latch state, allowing the circuit to restart the frequency detection and locking process as needed. Overall, this configuration offers a robust solution for achieving reliable audio output based on precise frequency control.PLL (Ul) is set with R2 to desired tone frequency. LED lights to indicate lock-up of PLL. Reduce signal level (Rl) and readjust R2 to assure lock-up. Delay is selected from counter U3 output. Circuits latches (turns on Q1 to allow audio to speaker) when proper frequency/duration signal is received To reset latch, a positive voltage must be applied briefly to the R input of U4. 🔗 External reference

The described circuit utilizes a Phase-Locked Loop (PLL) mechanism to maintain synchronization with a reference signal, which is crucial for applications requiring precise frequency control, such as audio signal processing. The PLL circuit is configured with an external resistor (R2) that sets the frequency of operation. The LED indicator serves as a visual confirmation of the PLL's lock status, which is essential for troubleshooting and operational verification.

To fine-tune the PLL's frequency locking, the circuit incorporates a feedback loop where the signal level is adjusted using resistor R1. This adjustment process ensures that the PLL can lock onto the desired frequency reliably. The output from counter U3 provides a timing signal that introduces a delay, allowing for the stabilization of the PLL before activating the audio output.

The activation of transistor Q1 is a critical function of the circuit, as it controls the flow of audio signals to the speaker. The latch mechanism ensures that audio is only output when the PLL has achieved the correct frequency and duration, preventing unwanted noise or signal artifacts from reaching the speaker.

For reset functionality, the circuit design includes a provision to apply a temporary positive voltage to the R input of U4. This reset action is necessary for reinitializing the latch state, allowing the circuit to restart the frequency detection and locking process as needed. Overall, this configuration offers a robust solution for achieving reliable audio output based on precise frequency control.PLL (Ul) is set with R2 to desired tone frequency. LED lights to indicate lock-up of PLL. Reduce signal level (Rl) and readjust R2 to assure lock-up. Delay is selected from counter U3 output. Circuits latches (turns on Q1 to allow audio to speaker) when proper frequency/duration signal is received To reset latch, a positive voltage must be applied briefly to the R input of U4. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713