3 square waves generator

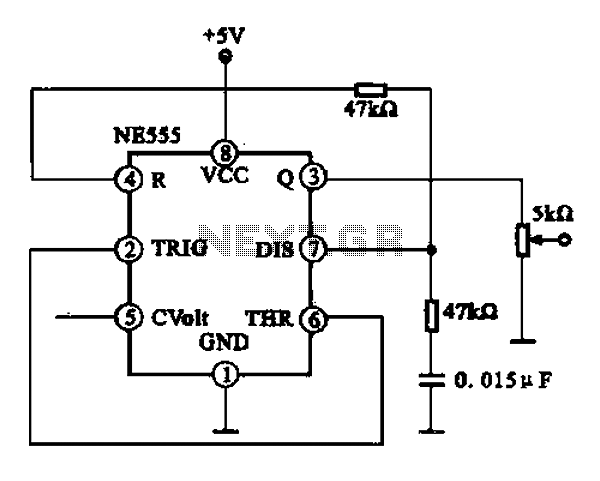

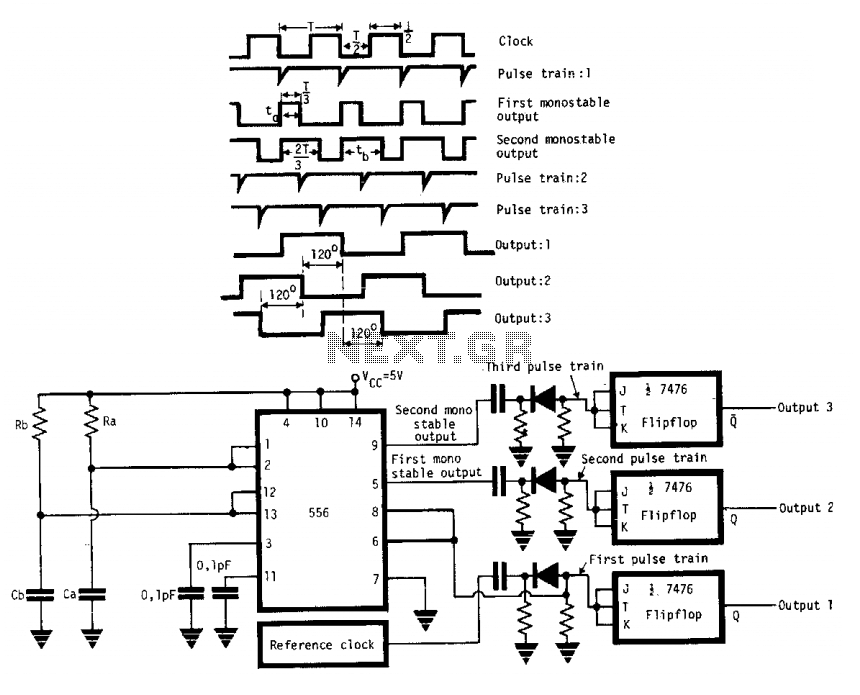

The circuit generates three square wave outputs with a 120° phase difference between each output. The reference clock frequency is set to twice the desired output frequency. This can be achieved using a crystal oscillator followed by a series of frequency dividers or by configuring an LM555 timer in astable mode with a 50% duty cycle. If 1/T represents the frequency of the reference clock, a dual timer (556) is employed to produce two monostable output pulses with durations of T/3 and 2T/3. The first timer's resistor (R) and capacitor (C) values are adjusted to ensure that ta = 1.1RaCa = T/3, while the second timer's R and C values are set to yield tb = 1.1RbCb = 2T/3. A negative pulse train is derived from the reference clock using a differentiator and clipper combination to trigger the two monostable timers. The resulting three pulse trains are used to trigger three JK flip-flops, which generate the three phase-shifted square wave outputs.

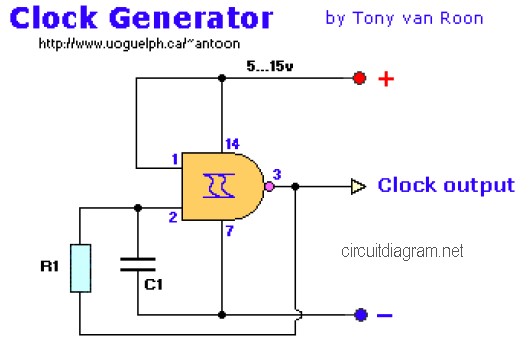

The schematic for this circuit includes several key components: a crystal oscillator, a series of frequency dividers, an LM555 timer configured in astable mode, a dual timer (556), resistors, capacitors, and JK flip-flops. The crystal oscillator serves as the primary frequency source, providing a stable reference clock. The frequency dividers reduce the clock frequency to the desired level, ensuring that the output frequency is half of the reference clock frequency.

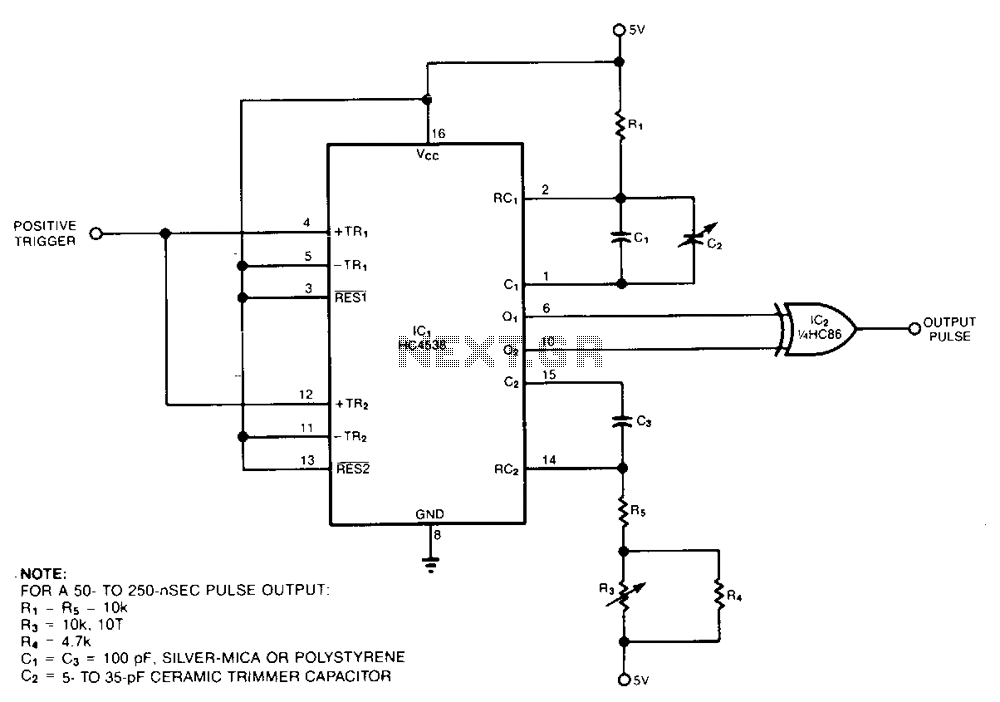

The LM555 timer is configured to operate in astable mode, generating a continuous square wave signal. The duty cycle is adjusted to 50%, which is essential for maintaining equal high and low periods in the output signal. The dual timer (556) is crucial for generating the monostable output pulses. The first timer is set to produce a pulse of duration T/3, while the second timer produces a longer pulse with a duration of 2T/3. The precise timing is achieved through careful selection of resistor and capacitor values according to the formulas provided.

To trigger the timers, a differentiator circuit is employed to create a negative pulse train from the reference clock. This pulse train is then processed through a clipper circuit to ensure that the pulses are of the correct amplitude and shape for reliable triggering of the monostable timers.

The output from the monostable timers is fed into three JK flip-flops, which are configured to toggle their outputs based on the incoming pulse trains. Each flip-flop produces a square wave output that is phase-shifted by 120° relative to the others. This configuration is particularly useful in applications requiring synchronized square wave signals, such as in motor control, phase-locked loops, or signal processing systems. The overall design emphasizes stability, precision, and reliability in generating multiple phase-shifted outputs from a single reference clock source.The circuit provides three square wave outputs with 120° of phase difference between each other. Reference clock frequency is twice that of the required frequency. This can be obtained from a crystal oscillator with a chain of dividers or by using LM 555 in 50% duty cycle astable mode. If 1/T is the frequency of the reference clock, the dual timer 556 is connected to give two mono-stable output pulses of duration T/3 and 2T/3. The first timer R and C value are adjusted so that ta = l.lRaCa = T/3 and the second timer R and C values so that tb = l.lRbCb = 2T/3.

For triggering the two monostables a negative pulse train (1st) is derived from the reference clock with a differentiator and a clipper combination as shown. The three pulse trains trigger three JK flip flops giving three phase square wave outputs.

The schematic for this circuit includes several key components: a crystal oscillator, a series of frequency dividers, an LM555 timer configured in astable mode, a dual timer (556), resistors, capacitors, and JK flip-flops. The crystal oscillator serves as the primary frequency source, providing a stable reference clock. The frequency dividers reduce the clock frequency to the desired level, ensuring that the output frequency is half of the reference clock frequency.

The LM555 timer is configured to operate in astable mode, generating a continuous square wave signal. The duty cycle is adjusted to 50%, which is essential for maintaining equal high and low periods in the output signal. The dual timer (556) is crucial for generating the monostable output pulses. The first timer is set to produce a pulse of duration T/3, while the second timer produces a longer pulse with a duration of 2T/3. The precise timing is achieved through careful selection of resistor and capacitor values according to the formulas provided.

To trigger the timers, a differentiator circuit is employed to create a negative pulse train from the reference clock. This pulse train is then processed through a clipper circuit to ensure that the pulses are of the correct amplitude and shape for reliable triggering of the monostable timers.

The output from the monostable timers is fed into three JK flip-flops, which are configured to toggle their outputs based on the incoming pulse trains. Each flip-flop produces a square wave output that is phase-shifted by 120° relative to the others. This configuration is particularly useful in applications requiring synchronized square wave signals, such as in motor control, phase-locked loops, or signal processing systems. The overall design emphasizes stability, precision, and reliability in generating multiple phase-shifted outputs from a single reference clock source.The circuit provides three square wave outputs with 120° of phase difference between each other. Reference clock frequency is twice that of the required frequency. This can be obtained from a crystal oscillator with a chain of dividers or by using LM 555 in 50% duty cycle astable mode. If 1/T is the frequency of the reference clock, the dual timer 556 is connected to give two mono-stable output pulses of duration T/3 and 2T/3. The first timer R and C value are adjusted so that ta = l.lRaCa = T/3 and the second timer R and C values so that tb = l.lRbCb = 2T/3.

For triggering the two monostables a negative pulse train (1st) is derived from the reference clock with a differentiator and a clipper combination as shown. The three pulse trains trigger three JK flip flops giving three phase square wave outputs.