Dual 8051S Execute In Lock-Step

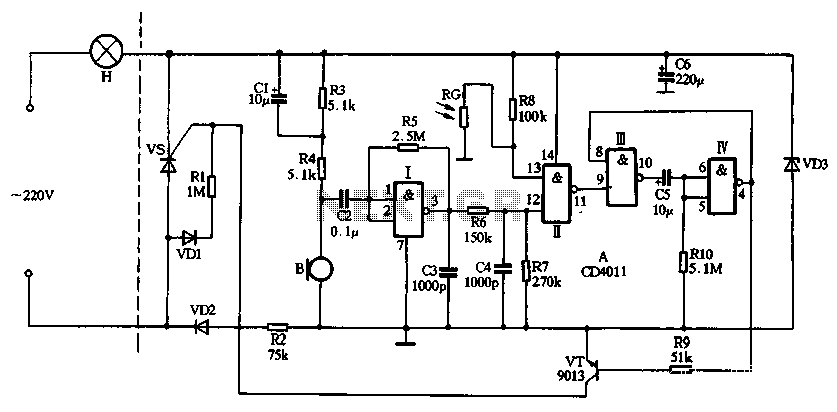

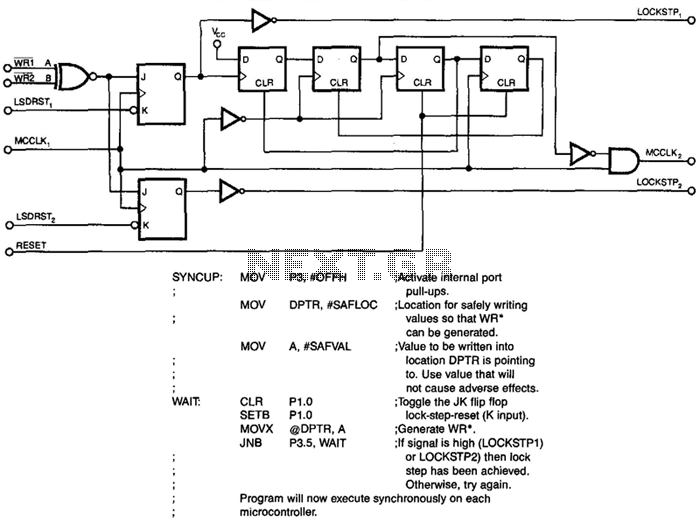

This hardware-software combination removes clocks from the slave until both integrated circuits synchronize. The firmware loop causes each circuit to generate a write (WR) signal once per loop. The circuit employs an exclusive-OR operation on the two WR signals to produce a miss-compare pulse. This miss-compare pulse is latched into two JK flip-flops via outputs LOCKSTP1 and LOCKSTP2. A high signal on these outputs indicates that the integrated circuits are in lock-step, prompting both circuits to exit the firmware loop. When using discrete components, it is advisable to utilize the Q output of the JK flip-flop and eliminate the circuit's inverters. The schematic utilizes ports 1 and 3 of the integrated circuits. A memory-mapped location cannot be used for the lock-step-detect clear (K input) as this would generate additional WR signals. This concept could potentially be applied to other circuits using their read (RD) signals, allowing the generation of an RD signal to activate the lock-step-detect clear without impacting the synchronization inputs.

The described circuit functions as a synchronization mechanism for two integrated circuits (ICs), ensuring that they operate in unison by removing clock signals from the slave device until synchronization is achieved. The firmware loop plays a crucial role in generating a WR signal for each iteration, which is essential for monitoring the operational status of both ICs.

The exclusive-OR gate serves as a critical component, comparing the WR signals from both ICs. When there is a discrepancy between the two signals, the exclusive-OR gate outputs a miss-compare pulse. This pulse is vital as it triggers the JK flip-flops, which are designed to latch the state of the synchronization process. The outputs LOCKSTP1 and LOCKSTP2 indicate whether the ICs are in lock-step operation, which is characterized by both circuits executing their programs in sync.

In practical implementations using discrete components, it is recommended to connect to the Q output of the JK flip-flops. This approach simplifies the design by removing unnecessary inverters, thereby enhancing circuit efficiency. The use of ports 1 and 3 of the ICs for this configuration is strategic, ensuring that the necessary signals are accessible for proper synchronization.

It is important to note that utilizing a memory-mapped location for the lock-step-detect clear (K input) is not feasible due to the risk of generating additional WR signals, which could disrupt the synchronization process. Instead, employing the RD signals from the ICs can provide a more effective means of managing the lock-step-detect clear without interfering with the synchronization inputs, thus maintaining the integrity of the synchronization process. This design can be extended to other types of circuits, offering versatility in synchronization applications across various electronic systems. This hardware-software combination deletes clocks from the slave until both /iPs synchronize. The firmware loop causes each to generate a WR signal once per loop. The circuit exclusive-ORs the two WR signals to produce a miss-compare pulse. The miss-compare pulse latches into the two JK flip-flops via outputs LOCKSTP1 and LOCKSTP2. A high on these signals indicates that the /tPs are in lock-step, causing both juPs" programs" execution to exit the firmware loop. If you use discrete components, you"ll probably want to use the Q output of the JK flip-flop and delete the circuit"s inverters.

The listing uses the /iPs" ports 1 and 3. You cannot use a memory-mapped location for the lock-step-detect clear (K input) because this scheme would generate additional WR signals. You could apply this idea to other, perhaps using their RD signals. This way, generating an RD signal to activate the lock-step-detect clear would not affect the synchronization inputs.

The described circuit functions as a synchronization mechanism for two integrated circuits (ICs), ensuring that they operate in unison by removing clock signals from the slave device until synchronization is achieved. The firmware loop plays a crucial role in generating a WR signal for each iteration, which is essential for monitoring the operational status of both ICs.

The exclusive-OR gate serves as a critical component, comparing the WR signals from both ICs. When there is a discrepancy between the two signals, the exclusive-OR gate outputs a miss-compare pulse. This pulse is vital as it triggers the JK flip-flops, which are designed to latch the state of the synchronization process. The outputs LOCKSTP1 and LOCKSTP2 indicate whether the ICs are in lock-step operation, which is characterized by both circuits executing their programs in sync.

In practical implementations using discrete components, it is recommended to connect to the Q output of the JK flip-flops. This approach simplifies the design by removing unnecessary inverters, thereby enhancing circuit efficiency. The use of ports 1 and 3 of the ICs for this configuration is strategic, ensuring that the necessary signals are accessible for proper synchronization.

It is important to note that utilizing a memory-mapped location for the lock-step-detect clear (K input) is not feasible due to the risk of generating additional WR signals, which could disrupt the synchronization process. Instead, employing the RD signals from the ICs can provide a more effective means of managing the lock-step-detect clear without interfering with the synchronization inputs, thus maintaining the integrity of the synchronization process. This design can be extended to other types of circuits, offering versatility in synchronization applications across various electronic systems. This hardware-software combination deletes clocks from the slave until both /iPs synchronize. The firmware loop causes each to generate a WR signal once per loop. The circuit exclusive-ORs the two WR signals to produce a miss-compare pulse. The miss-compare pulse latches into the two JK flip-flops via outputs LOCKSTP1 and LOCKSTP2. A high on these signals indicates that the /tPs are in lock-step, causing both juPs" programs" execution to exit the firmware loop. If you use discrete components, you"ll probably want to use the Q output of the JK flip-flop and delete the circuit"s inverters.

The listing uses the /iPs" ports 1 and 3. You cannot use a memory-mapped location for the lock-step-detect clear (K input) because this scheme would generate additional WR signals. You could apply this idea to other, perhaps using their RD signals. This way, generating an RD signal to activate the lock-step-detect clear would not affect the synchronization inputs.