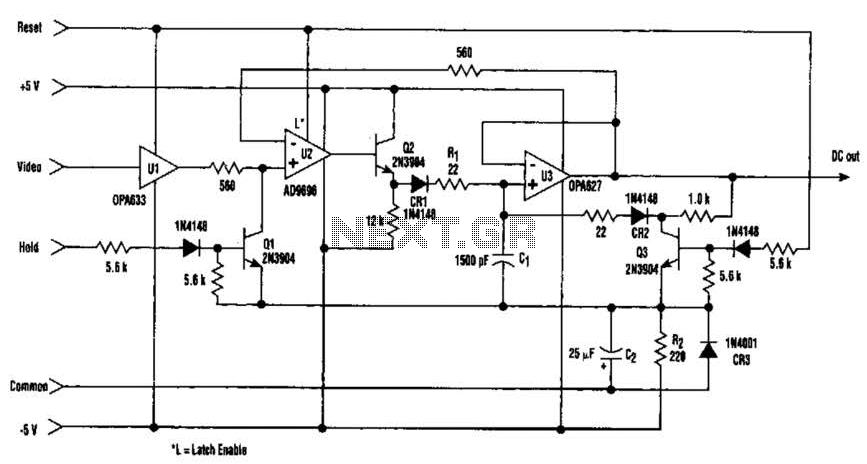

Fast Video Signal Amplitude Measurer Circuit

The amplitude of a video signal can be measured using a straightforward circuit that functions as a modified standard peak detector. This device is capable of verifying RGB signals produced by video RAMDACs. U1 is a high-speed buffer, while U2 serves as a latched comparator. C1 acts as a hold capacitor, and reset operations are managed by Q3. U2 features a latch that retains the last state of the comparator, ensuring that the output remains low during the reset phase. The DC output voltage corresponds to the maximum amplitude of the signal.

The circuit operates by capturing the peak amplitude of the video signal, which is essential in various applications such as video processing and display calibration. The high-speed buffer (U1) ensures that the incoming video signal is accurately transmitted to the comparator (U2) without significant delay or distortion. This is crucial for maintaining the integrity of the signal being measured.

The latched comparator (U2) compares the incoming signal with a reference level and latches its output state, thus providing a stable reading of the peak amplitude. The hold capacitor (C1) retains the measured voltage, allowing for a consistent output that reflects the maximum amplitude of the video signal over time. This feature is particularly useful when analyzing rapid changes in video signal amplitudes, as it allows for a snapshot of the peak value.

The reset mechanism, controlled by transistor Q3, is vital for ensuring that the system can accurately measure new peaks without interference from previously captured values. During a reset operation, Q3 pulls the comparator output low, clearing the previous state and preparing the circuit for the next measurement cycle.

Overall, this circuit design is effective for applications requiring precise measurement of video signal amplitudes, ensuring reliable performance in various electronic systems that utilize RGB signals from video RAMDACs. Video-signal amplitude can be measured with this simple circuit, which is basically a modified standard peak detector. The device can verify RGB generated by video RAMDACs. Ul is a high-speed buffer and U2 is a latched comparator. CI is a hold capacitor. Reset is performed by Q3. U2 has a latch that maintains the last comparator state. The reset holds the comparator output low during the reset operation. The dc output voltage is equal to the signal`s maximum amplitude.

The circuit operates by capturing the peak amplitude of the video signal, which is essential in various applications such as video processing and display calibration. The high-speed buffer (U1) ensures that the incoming video signal is accurately transmitted to the comparator (U2) without significant delay or distortion. This is crucial for maintaining the integrity of the signal being measured.

The latched comparator (U2) compares the incoming signal with a reference level and latches its output state, thus providing a stable reading of the peak amplitude. The hold capacitor (C1) retains the measured voltage, allowing for a consistent output that reflects the maximum amplitude of the video signal over time. This feature is particularly useful when analyzing rapid changes in video signal amplitudes, as it allows for a snapshot of the peak value.

The reset mechanism, controlled by transistor Q3, is vital for ensuring that the system can accurately measure new peaks without interference from previously captured values. During a reset operation, Q3 pulls the comparator output low, clearing the previous state and preparing the circuit for the next measurement cycle.

Overall, this circuit design is effective for applications requiring precise measurement of video signal amplitudes, ensuring reliable performance in various electronic systems that utilize RGB signals from video RAMDACs. Video-signal amplitude can be measured with this simple circuit, which is basically a modified standard peak detector. The device can verify RGB generated by video RAMDACs. Ul is a high-speed buffer and U2 is a latched comparator. CI is a hold capacitor. Reset is performed by Q3. U2 has a latch that maintains the last comparator state. The reset holds the comparator output low during the reset operation. The dc output voltage is equal to the signal`s maximum amplitude.