Frequency doubler II

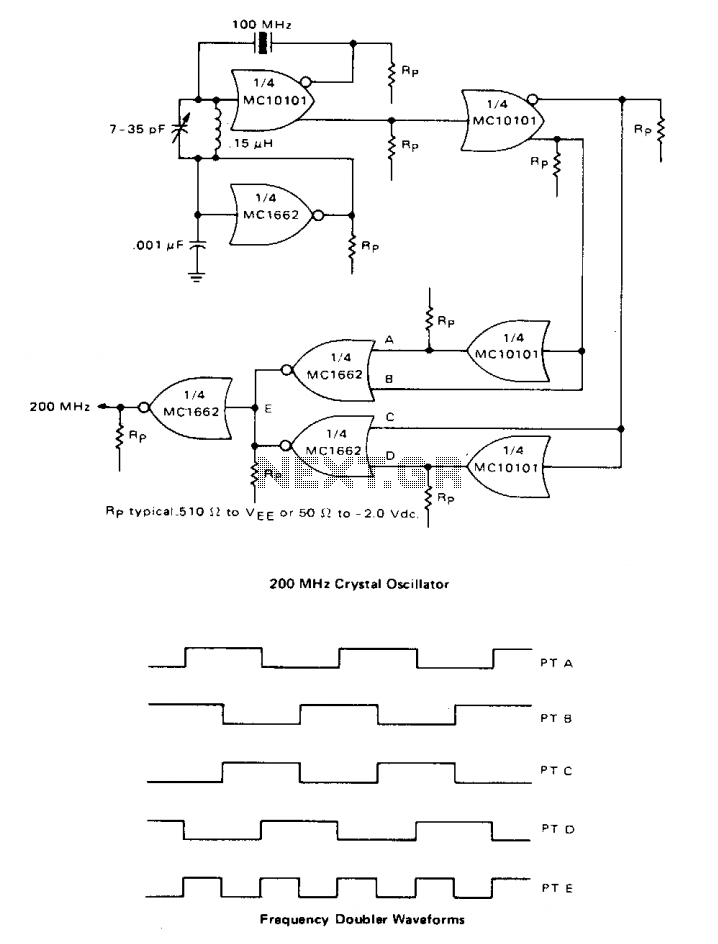

This frequency doubler uses one CMOS quad, two input NAND gate package type 4011. The frequency doubler proper consists of an inverter IC1B, two differentiating networks R1/C1, R2/C2 and NAND gate IC1A, IC1C and IC1D function as input and output buffers. In Fig.2 exist the pulses in different points of circuit.

The described frequency doubler circuit utilizes a CMOS quad two-input NAND gate IC, specifically the 4011 package, to achieve frequency multiplication. The core operation relies on the conversion of an input frequency to its double by employing a combination of logic gates and differentiating networks.

The circuit is structured around an inverter (IC1B) that is responsible for inverting the input signal. This inversion is crucial as it helps to create the necessary phase shifts required for the frequency doubling process. The differentiating networks, composed of resistors (R1, R2) and capacitors (C1, C2), play a significant role in shaping the input waveform. These networks convert the square wave input into a series of sharp pulses, which are essential for effective triggering of the NAND gates.

The NAND gates (IC1A, IC1C, and IC1D) serve multiple functions in this circuit. IC1A acts as the primary logic gate to process the differentiated signals, while IC1C and IC1D are utilized as buffers to ensure that the output signals maintain their integrity and drive capabilities. This arrangement allows for a robust output that can effectively double the frequency of the input signal.

The output of the circuit presents a waveform that oscillates at twice the frequency of the original input, demonstrating the effectiveness of the frequency doubler. The arrangement of components ensures minimal signal degradation, allowing for a clean and precise output waveform. The use of CMOS technology contributes to low power consumption and high-speed operation, making this frequency doubler suitable for various applications in signal processing and communication systems.

In summary, the frequency doubler circuit based on the CMOS quad NAND gate 4011 is a well-structured design that efficiently converts an input frequency into its double using inverting and buffering techniques, along with differentiating networks for optimal signal shaping. This frequency doubler uses one CMOS quad, two input NAND gate package type 4011. The frequency doubler proper consists of an inverter IC1B, two differentiating networks R1/C1, R2/C2 and NAND gate IC1A, IC1C and IC1D function as input and output buffers. In Fig.2 exist the pulses in different points of circuit. 🔗 External reference

The described frequency doubler circuit utilizes a CMOS quad two-input NAND gate IC, specifically the 4011 package, to achieve frequency multiplication. The core operation relies on the conversion of an input frequency to its double by employing a combination of logic gates and differentiating networks.

The circuit is structured around an inverter (IC1B) that is responsible for inverting the input signal. This inversion is crucial as it helps to create the necessary phase shifts required for the frequency doubling process. The differentiating networks, composed of resistors (R1, R2) and capacitors (C1, C2), play a significant role in shaping the input waveform. These networks convert the square wave input into a series of sharp pulses, which are essential for effective triggering of the NAND gates.

The NAND gates (IC1A, IC1C, and IC1D) serve multiple functions in this circuit. IC1A acts as the primary logic gate to process the differentiated signals, while IC1C and IC1D are utilized as buffers to ensure that the output signals maintain their integrity and drive capabilities. This arrangement allows for a robust output that can effectively double the frequency of the input signal.

The output of the circuit presents a waveform that oscillates at twice the frequency of the original input, demonstrating the effectiveness of the frequency doubler. The arrangement of components ensures minimal signal degradation, allowing for a clean and precise output waveform. The use of CMOS technology contributes to low power consumption and high-speed operation, making this frequency doubler suitable for various applications in signal processing and communication systems.

In summary, the frequency doubler circuit based on the CMOS quad NAND gate 4011 is a well-structured design that efficiently converts an input frequency into its double using inverting and buffering techniques, along with differentiating networks for optimal signal shaping. This frequency doubler uses one CMOS quad, two input NAND gate package type 4011. The frequency doubler proper consists of an inverter IC1B, two differentiating networks R1/C1, R2/C2 and NAND gate IC1A, IC1C and IC1D function as input and output buffers. In Fig.2 exist the pulses in different points of circuit. 🔗 External reference