generating stripboard layouts

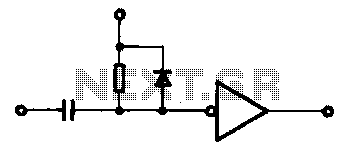

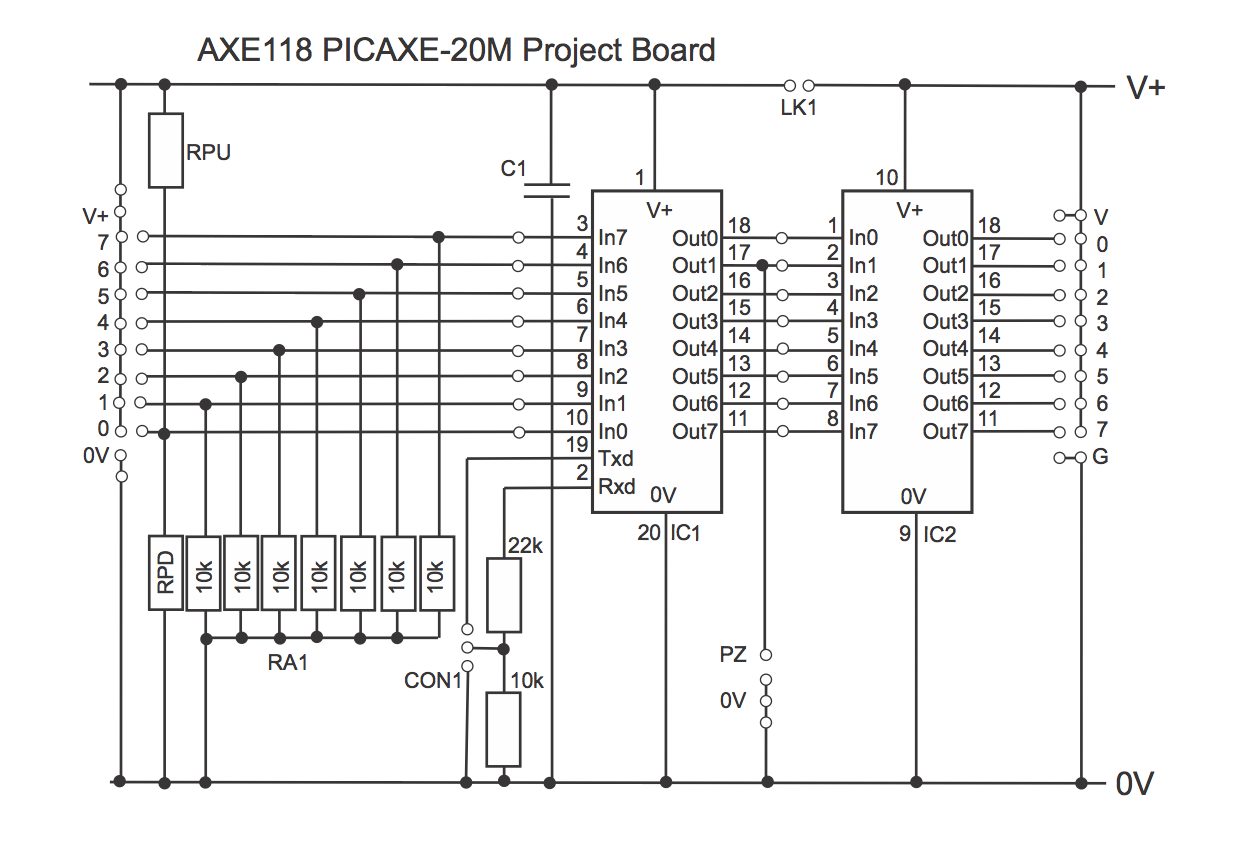

The task involves arranging components in such a way that connections are made along the same lanes. To facilitate this process, lanes can be broken or joined using wire links. The focus of this discussion is on automating the arrangement to achieve an optimal and seamless transition from a graphical representation to a set of lanes. The N-Queens problem serves as a relevant example, where N queens must be placed on an NxN board without any queen threatening another. This is accomplished using the all-different constraint, which ensures that the queens occupy distinct rows, columns, and diagonals. Lanes are defined as a finite set of numbers, which allows the use of all-different constraints but complicates the representation of broken lines. Components are represented as a list of connected points, with connected components sharing the same variable. However, this approach encounters difficulties when integrating wire links.

The circuit design described involves a logical arrangement of components based on the principles of the N-Queens problem. In this context, the components are represented as nodes on a graph, with lanes acting as pathways for connections. The use of the all-different constraint ensures that each component occupies a unique position within the defined lanes, thereby preventing conflicts in connectivity.

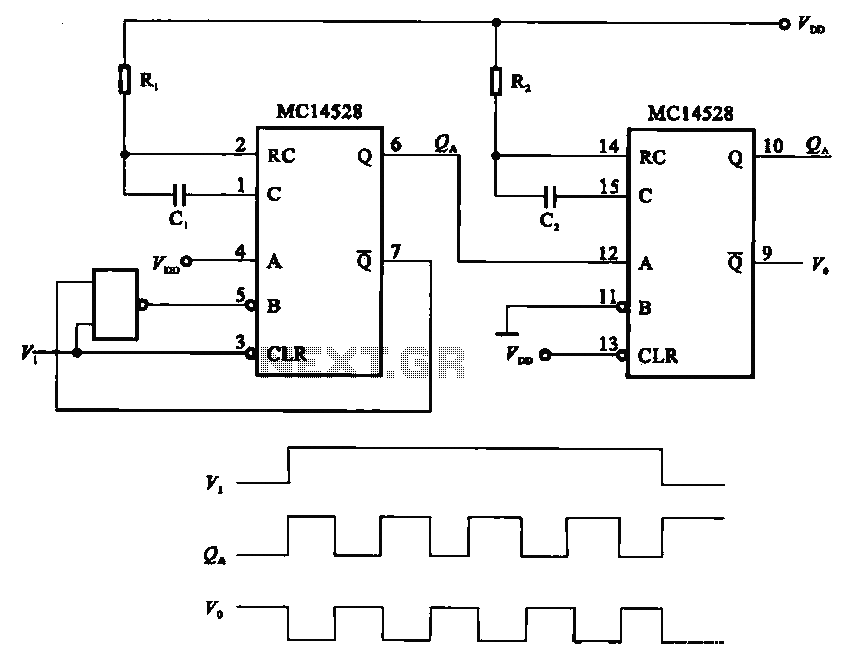

The implementation begins by defining the lanes as a range of integers, which establishes a finite domain for the connections. A function is defined to represent the relationship between connected components, ensuring that they adhere to the constraints of the circuit design. For example, the resistor function is utilized to define connections between two points, requiring that the lanes assigned to the components are distinct and valid according to the defined constraints.

The circuit also incorporates wire links to facilitate connections between broken lanes. This is achieved through the use of fresh variables that represent the new connections, allowing for flexibility in the arrangement of components. The distinctness of lanes is maintained through the use of the distinctfd function, which checks that the lanes assigned to each component do not overlap.

The overall process involves running queries that generate valid configurations of the circuit, ensuring that all components are connected appropriately while adhering to the constraints imposed by the N-Queens problem. This automated approach not only streamlines the arrangement of components but also enhances the efficiency of circuit design by reducing the potential for errors in connectivity.All you have to do is insert the pieces so that things that should connect are on the same lane. To make things even easier, you can break lanes, or join lanes with a wire link. Right, this brings me to the meat of this post. How can we automate this, to get an optimal and flawless translation from what is basically a graph, to a set of lanes In he N-Queens problem, N queens must be arranged on an NxN board, so that no queen attacks another queen. This is implemented using all-difffd 2, which forces the queens to all be on different rows, columns and diagonals.

For starters, lets define lanes as a finite domain of numbers. This allows us to use all-difffd, but gets us in trouble when we need to express broken lines. In this simplified version, I also just defined components as a list of points they are connected to. Components that are connected, use the same fresh variable. This also gets us into trouble when we insert wire links. > (run 1 (q) (fresh (l1 l2 l3 l4) (infd l1 l2 l3 l4 (range 0 10) (= q (list (list `r1 l1 l2) (list `r2 l3 l4) (list `fet l1 l3 l2) (distinctfd (list l1 l2 l3 l4) (r1 0 1) (r2 2 3) (fet 0 2 1) (define lanes (range 0 50) (define lane (lambda (l) (infd l lanes) (define resistor (lambda (l1 l2 r) (fresh (l2+) (lane l1) (lane l2) (lane l2+) (plusfd l2 2 l2+) ( (run 5 (q) (fresh (l1 l2) (resistor l1 l2 q) (r 3 0) (r 4 0) (r 4 1) (r 5 0) (r 5 1) > (run 1 (q) (fresh (l1 l2 l3 l4 r1 r2) (infd l1 l2 l3 l4 lanes) (resistor l1 l2 r1) (resistor l3 l4 r2) (= q (list r1 r2 (list `fet l1 l3 l2) (distinctfd (list l1 l2 l3 l4) (r 3 0) (r 4 1) (fet 3 4 0)

🔗 External reference

The circuit design described involves a logical arrangement of components based on the principles of the N-Queens problem. In this context, the components are represented as nodes on a graph, with lanes acting as pathways for connections. The use of the all-different constraint ensures that each component occupies a unique position within the defined lanes, thereby preventing conflicts in connectivity.

The implementation begins by defining the lanes as a range of integers, which establishes a finite domain for the connections. A function is defined to represent the relationship between connected components, ensuring that they adhere to the constraints of the circuit design. For example, the resistor function is utilized to define connections between two points, requiring that the lanes assigned to the components are distinct and valid according to the defined constraints.

The circuit also incorporates wire links to facilitate connections between broken lanes. This is achieved through the use of fresh variables that represent the new connections, allowing for flexibility in the arrangement of components. The distinctness of lanes is maintained through the use of the distinctfd function, which checks that the lanes assigned to each component do not overlap.

The overall process involves running queries that generate valid configurations of the circuit, ensuring that all components are connected appropriately while adhering to the constraints imposed by the N-Queens problem. This automated approach not only streamlines the arrangement of components but also enhances the efficiency of circuit design by reducing the potential for errors in connectivity.All you have to do is insert the pieces so that things that should connect are on the same lane. To make things even easier, you can break lanes, or join lanes with a wire link. Right, this brings me to the meat of this post. How can we automate this, to get an optimal and flawless translation from what is basically a graph, to a set of lanes In he N-Queens problem, N queens must be arranged on an NxN board, so that no queen attacks another queen. This is implemented using all-difffd 2, which forces the queens to all be on different rows, columns and diagonals.

For starters, lets define lanes as a finite domain of numbers. This allows us to use all-difffd, but gets us in trouble when we need to express broken lines. In this simplified version, I also just defined components as a list of points they are connected to. Components that are connected, use the same fresh variable. This also gets us into trouble when we insert wire links. > (run 1 (q) (fresh (l1 l2 l3 l4) (infd l1 l2 l3 l4 (range 0 10) (= q (list (list `r1 l1 l2) (list `r2 l3 l4) (list `fet l1 l3 l2) (distinctfd (list l1 l2 l3 l4) (r1 0 1) (r2 2 3) (fet 0 2 1) (define lanes (range 0 50) (define lane (lambda (l) (infd l lanes) (define resistor (lambda (l1 l2 r) (fresh (l2+) (lane l1) (lane l2) (lane l2+) (plusfd l2 2 l2+) (

🔗 External reference