Simple Combination Lock

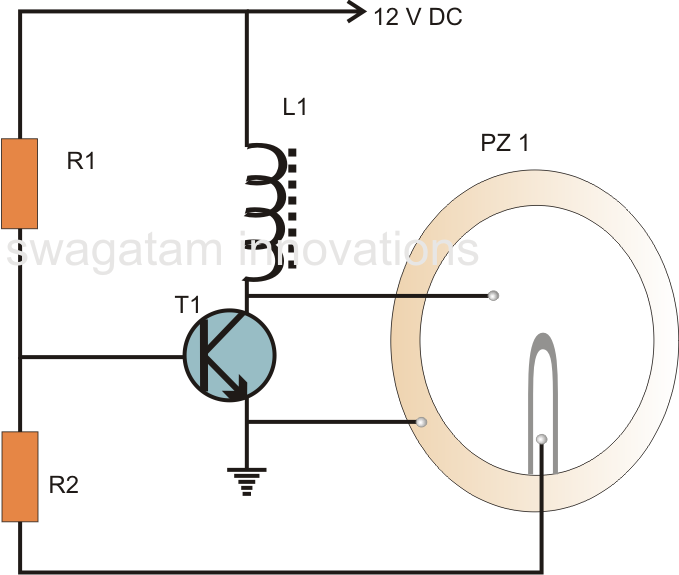

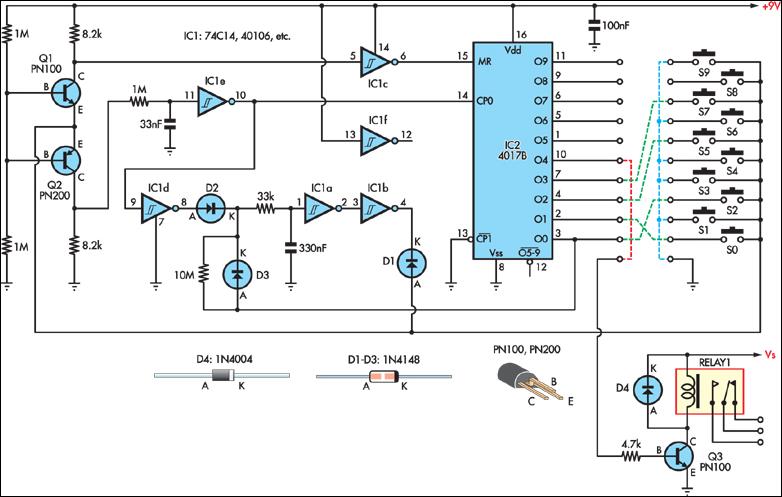

This simple combination lock accommodates codes from 1 to 9 digits long, with the only restriction being that the same digit cannot be used twice. The circuit is designed for a 4-digit code, illustrated by the example "2057". Any unused switches are connected to ground. When power is applied, the 330nF capacitor connected to pin 1 of inverter IC1a discharges, maintaining a logic low level. The high output is inverted by a second gate (IC1b), resulting in a logic low on pin 4. This pulls the emitter of transistor Q1 low via diode D1, causing the transistor to conduct. The decreasing voltage on the collector then pulls the input of IC1c low, which resets counter IC2. Upon reset, output O0 (pin 3) of IC2 goes high, charging the 330nF capacitor through diode D2 and the 33kΩ resistor. If switch S2 is pressed, the emitter of Q2 is pulled high, causing Q2 to conduct and applying a rising positive voltage to one end of the 1MΩ resistor. This resistor and the 33nF capacitor form a switch debounce circuit, delaying the pulse through IC1e by about 33ms. After this delay, the output of IC1e goes low. However, counter IC2 does not increment at this stage, as it requires a positive-going edge at the clock input (pin 14). When the switch is released, Q2 turns off, IC1e's output returns high after the debounce period, and the counter advances to the next state (i.e., O0 goes low and O1 goes high). When output O0 (pin 3) goes low, the 330nF capacitor begins discharging through the 33kΩ and 10MΩ resistors, allowing approximately 3 seconds for the operator to press the next button. If no button is pressed within this timeframe, the output of IC1b goes low, pulling the emitter of Q1 low and resetting the counter via IC1c. Consequently, the code entry must be restarted. When the second digit of the code is entered (0 in this example), the emitter of Q2 is again pulled high. Q2 turns on, and after the debounce delay, IC1e's output goes low. Upon releasing the switch, Q2 turns off, IC1e's output goes high, and the counter advances to state 2. It is important to note that while the switch is pressed, the output of IC1d remains high, recharging the 330nF capacitor and resetting the 3-second delay, thereby allowing the operator another 3 seconds to press the next digit. This sequence continues for each digit in the code. If an incorrect switch is pressed at any point, IC2 is reset as previously described. Conversely, if the correct code is entered, IC1 advances to state 4 (for the 4-digit example) upon releasing the fourth switch. Output O4 then goes high, activating transistor Q3 and relay 1. Q3 can handle a load current of up to approximately 300mA. For higher current requirements, a Darlington pair or power MOSFET can be used as a substitute. Diode D4 is necessary if the load is inductive (for example, a relay or solenoid).

The combination lock circuit functions based on a series of logical states and transitions that are managed through the use of various integrated circuits and passive components. The core of the design revolves around the use of flip-flops and counters to track the input sequence of digits. Each switch press is debounced to prevent false triggering, ensuring that only deliberate presses are counted. The timing mechanism, facilitated by the capacitor and resistors, provides a window for user input while also ensuring that the system resets if input is not received within the specified timeframe.

The choice of components, such as the 330nF capacitor and 33kΩ resistor, is critical in determining the debounce timing and the overall responsiveness of the lock. The use of a relay driven by Q3 allows for the control of higher power loads, making the system versatile for various applications. The inclusion of protection diodes for inductive loads ensures that the circuit remains robust against back EMF, which could otherwise damage sensitive components.

This combination lock circuit is an excellent example of how digital logic can be used to create practical and secure applications, combining user input with electronic control to achieve reliable operation.This simple combination lock accommodates codes from 1-9 digits long, with the only restriction being that the same digit cannot be used twice. The circuit shows strapping for a 4-digit code, in this case "2057". Any unused switches are strapped to ground. When power is applied, the 330nF capacitor connected to pin 1 of inverter IC1a is discharged , holding it at a logic low level. The high output is inverted by a second gate (IC1b), with the result being a logic low on pin 4. This pulls Q1`s emitter low via D1, causing the transistor to conduct. The falling voltage on the collector then pulls the input of IC1c low, which in turn resets counter IC2. On reset, output O0 (pin 3) of IC2 goes high, charging the 330nF capacitor via D2 and the 33k © resistor.

If switch S2 is now pressed, Q2`s emitter will be pulled high and so Q2 conducts, applying a rising positive voltage to one end of the 1M © resistor. This resistor and the 33nF capacitor act as a switch "debounce" circuit, delaying the pulse through IC1e by about 33ms.

After the delay, the output of IC1e goes low. However, counter IC2 does not increment at this stage, since it needs a positive-going edge at the clock input (pin 14). When the switch is released, Q2 turns off, IC1e`s output goes high after the debounce period and the counter advances to the next state (ie.

O0 goes low and O1 goes high). When output O0 (pin 3) goes low, the 330nF capacitor starts discharging through the 33k © and 10M © resistors. This allows about 3s for the operator to press the next button. If no button is pressed within this period, IC1b`s output goes low, which pulls Q1`s emitter low and resets the counter via IC1c.

Hence the code entry must be restarted. When the second digit of the code is entered (0 in this example), Q2`s emitter is again pulled high. Q2 thus turns on and after the debounce delay, IC1e`s output goes low. When the switch is released, Q2 turns off, IC1e`s output goes high and the counter advances to state 2. Note that while the switch is pressed, IC1d`s output is high, recharging the 330nF capacitor and therefore resetting the 3s delay.

Thus, the operator is allowed another 3s to press the next digit. This process is repeated for each digit in the sequence. If the wrong switch is pressed at any point, IC2 is reset as described above. Conversely, if the correct code is entered, IC1 advances to state 4 (for our 4-digit example) on release of the fourth switch. Output O4 then goes high and turns on Q3 and relay 1. Q3 can handle up to about 300mA of load current. If more current is required, then either a Darlington or power Mosfet can be substituted. D4 is required if the load is inductive (eg, a relay, solenoid, etc). 🔗 External reference

The combination lock circuit functions based on a series of logical states and transitions that are managed through the use of various integrated circuits and passive components. The core of the design revolves around the use of flip-flops and counters to track the input sequence of digits. Each switch press is debounced to prevent false triggering, ensuring that only deliberate presses are counted. The timing mechanism, facilitated by the capacitor and resistors, provides a window for user input while also ensuring that the system resets if input is not received within the specified timeframe.

The choice of components, such as the 330nF capacitor and 33kΩ resistor, is critical in determining the debounce timing and the overall responsiveness of the lock. The use of a relay driven by Q3 allows for the control of higher power loads, making the system versatile for various applications. The inclusion of protection diodes for inductive loads ensures that the circuit remains robust against back EMF, which could otherwise damage sensitive components.

This combination lock circuit is an excellent example of how digital logic can be used to create practical and secure applications, combining user input with electronic control to achieve reliable operation.This simple combination lock accommodates codes from 1-9 digits long, with the only restriction being that the same digit cannot be used twice. The circuit shows strapping for a 4-digit code, in this case "2057". Any unused switches are strapped to ground. When power is applied, the 330nF capacitor connected to pin 1 of inverter IC1a is discharged , holding it at a logic low level. The high output is inverted by a second gate (IC1b), with the result being a logic low on pin 4. This pulls Q1`s emitter low via D1, causing the transistor to conduct. The falling voltage on the collector then pulls the input of IC1c low, which in turn resets counter IC2. On reset, output O0 (pin 3) of IC2 goes high, charging the 330nF capacitor via D2 and the 33k © resistor.

If switch S2 is now pressed, Q2`s emitter will be pulled high and so Q2 conducts, applying a rising positive voltage to one end of the 1M © resistor. This resistor and the 33nF capacitor act as a switch "debounce" circuit, delaying the pulse through IC1e by about 33ms.

After the delay, the output of IC1e goes low. However, counter IC2 does not increment at this stage, since it needs a positive-going edge at the clock input (pin 14). When the switch is released, Q2 turns off, IC1e`s output goes high after the debounce period and the counter advances to the next state (ie.

O0 goes low and O1 goes high). When output O0 (pin 3) goes low, the 330nF capacitor starts discharging through the 33k © and 10M © resistors. This allows about 3s for the operator to press the next button. If no button is pressed within this period, IC1b`s output goes low, which pulls Q1`s emitter low and resets the counter via IC1c.

Hence the code entry must be restarted. When the second digit of the code is entered (0 in this example), Q2`s emitter is again pulled high. Q2 thus turns on and after the debounce delay, IC1e`s output goes low. When the switch is released, Q2 turns off, IC1e`s output goes high and the counter advances to state 2. Note that while the switch is pressed, IC1d`s output is high, recharging the 330nF capacitor and therefore resetting the 3s delay.

Thus, the operator is allowed another 3s to press the next digit. This process is repeated for each digit in the sequence. If the wrong switch is pressed at any point, IC2 is reset as described above. Conversely, if the correct code is entered, IC1 advances to state 4 (for our 4-digit example) on release of the fourth switch. Output O4 then goes high and turns on Q3 and relay 1. Q3 can handle up to about 300mA of load current. If more current is required, then either a Darlington or power Mosfet can be substituted. D4 is required if the load is inductive (eg, a relay, solenoid, etc). 🔗 External reference