4017 CMOS Decade Counter

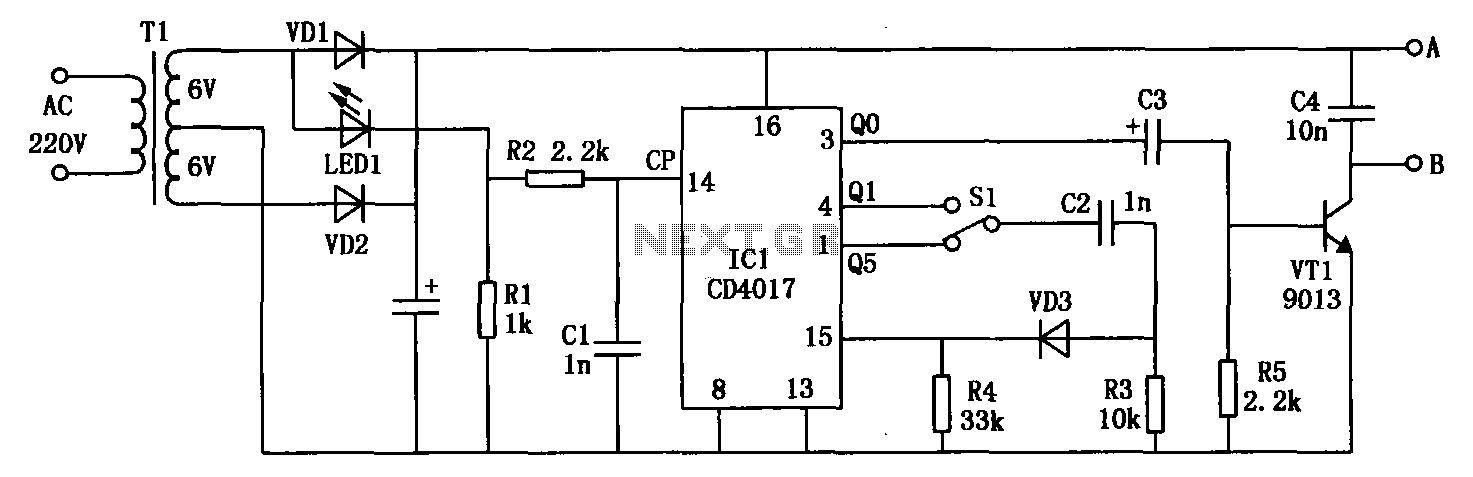

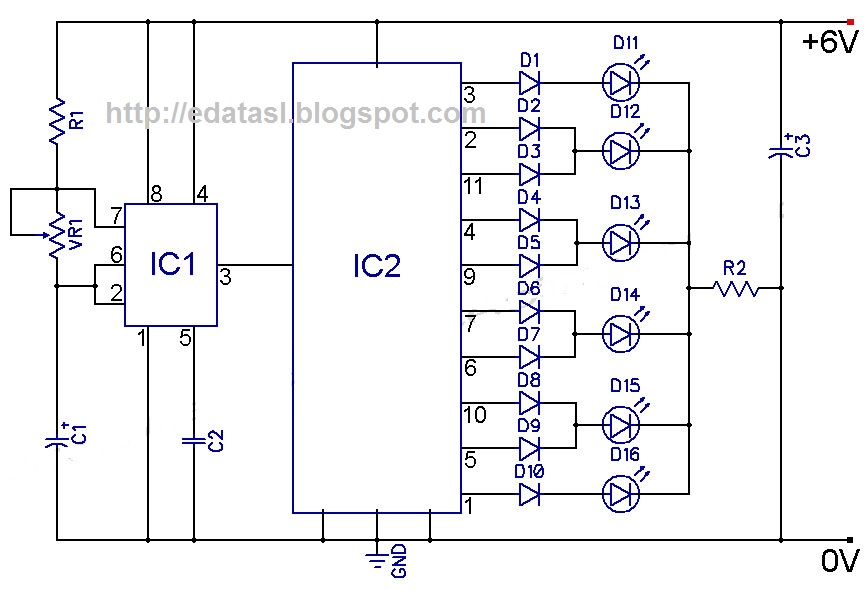

At the onset of the second clock cycle, the output labeled "0" transitions to a LOW state while the output labeled "1" transitions to a HIGH state. This sequence persists across ten outputs, eventually cycling back to output "0" on the eleventh cycle.

The described circuit appears to function as a sequential output generator that relies on clock cycles to control the state of multiple outputs. In this configuration, the clock signal serves as the primary timing reference, dictating the transitions of the outputs.

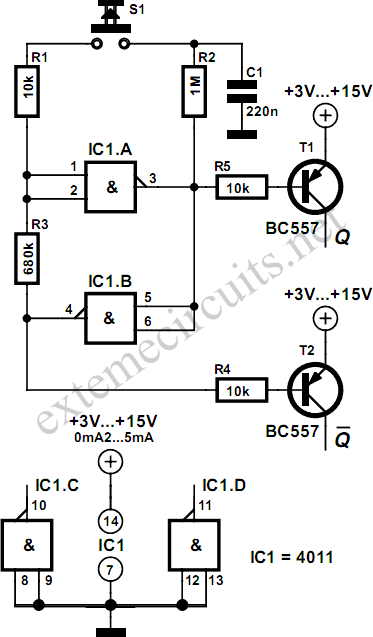

The circuit likely employs a flip-flop or a series of flip-flops to manage the state changes of each output. When the clock signal rises, the flip-flops are triggered to change their states. Specifically, the first output, designated as "0," is set to LOW, indicating an inactive state, while the second output, labeled "1," is set to HIGH, indicating an active state.

The design suggests a binary counting mechanism, where each subsequent clock cycle results in a shift of the output states. After the tenth output has been activated, the sequence resets, cycling back to the first output on the eleventh cycle. This behavior is characteristic of a ring counter or a shift register configured for a specific counting sequence.

To implement this circuit, a series of D flip-flops can be connected in a cascade configuration, with the output of one flip-flop serving as the input to the next. The clock signal would be connected to the clock input of all flip-flops to ensure synchronous operation. The outputs can be monitored through LEDs or other indicators to visually represent the state transitions. Additionally, resistors may be included in series with the outputs to limit current and protect the components.

Overall, this circuit effectively demonstrates the principles of digital logic and sequential circuits, showcasing how clock signals can be used to control multiple outputs in a predictable manner.On the rise of the second clock cycle, output "0" goes LOW and output "1" goes HIGH. This process continues across the tenoutputs and cycles to output "0" on the eleventh cycle. 🔗 External reference

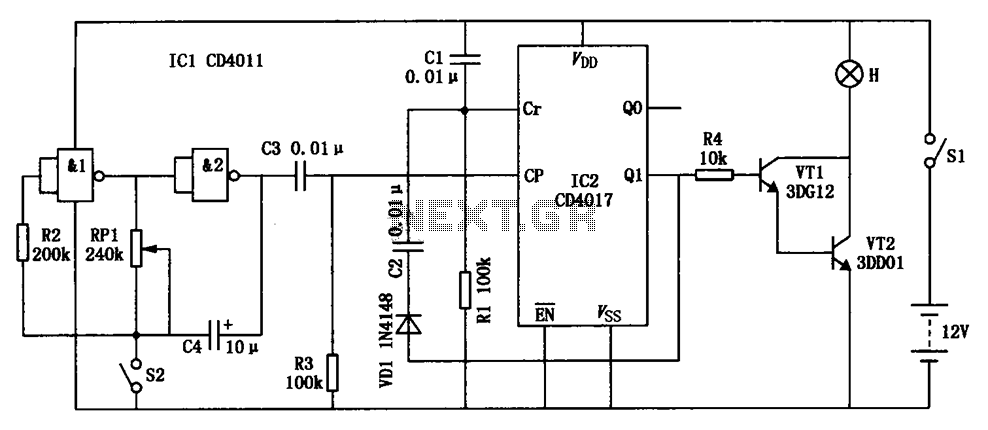

The described circuit appears to function as a sequential output generator that relies on clock cycles to control the state of multiple outputs. In this configuration, the clock signal serves as the primary timing reference, dictating the transitions of the outputs.

The circuit likely employs a flip-flop or a series of flip-flops to manage the state changes of each output. When the clock signal rises, the flip-flops are triggered to change their states. Specifically, the first output, designated as "0," is set to LOW, indicating an inactive state, while the second output, labeled "1," is set to HIGH, indicating an active state.

The design suggests a binary counting mechanism, where each subsequent clock cycle results in a shift of the output states. After the tenth output has been activated, the sequence resets, cycling back to the first output on the eleventh cycle. This behavior is characteristic of a ring counter or a shift register configured for a specific counting sequence.

To implement this circuit, a series of D flip-flops can be connected in a cascade configuration, with the output of one flip-flop serving as the input to the next. The clock signal would be connected to the clock input of all flip-flops to ensure synchronous operation. The outputs can be monitored through LEDs or other indicators to visually represent the state transitions. Additionally, resistors may be included in series with the outputs to limit current and protect the components.

Overall, this circuit effectively demonstrates the principles of digital logic and sequential circuits, showcasing how clock signals can be used to control multiple outputs in a predictable manner.On the rise of the second clock cycle, output "0" goes LOW and output "1" goes HIGH. This process continues across the tenoutputs and cycles to output "0" on the eleventh cycle. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713