An Overly Sensitive One-Shot

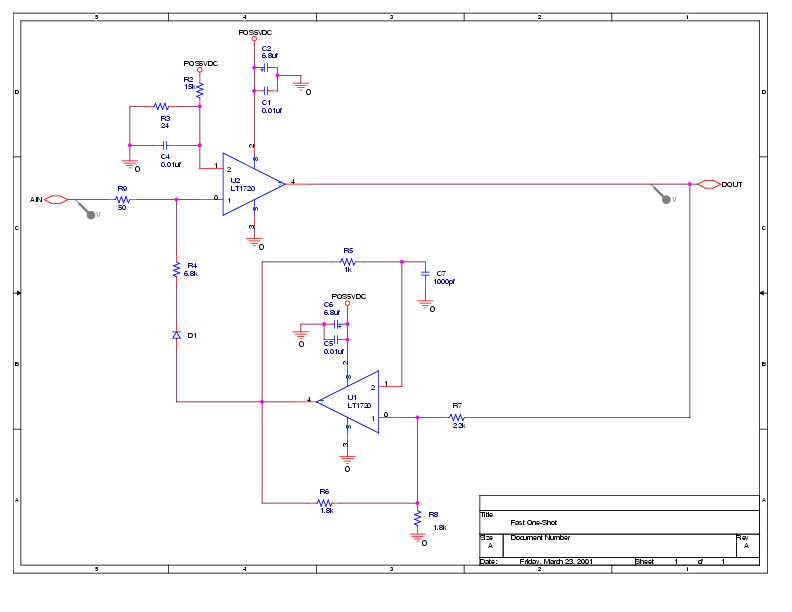

This circuit is from the datasheet for Linear Technology's LT1720, a 4.5 ns comparator. It is labeled "Pulse Stretcher" at the end of the document. Essentially, it functions as a one-shot with sensitivity down to 14 mV for input pulses ranging from 5 ns to 10 ns, meaning it does not require a full swing from logical low to high like most one-shots, and it provides TTL logic level outputs. The circuit exhibits a delay of only 4.5 ns from input to output. An OrCAD schematic (PDF) is available for simulating the circuit. The diode (D1) used is a 1N5711. PSpice simulations confirm that it has the advertised sensitivity, successfully triggering with a 5 ns 14 mV pulse, provided the input has 2 ns rise and fall times. However, the datasheet does not mention that this one-shot has a significant recovery time of approximately six time constants, leading to output signals that are shorter than the desired time constant (1 µs for the schematic) for any additional inputs arriving 1 to 7 time constants after the initial input. Discharging the timing capacitor (C7) with a FET switch can substantially reduce the recovery time. An OrCAD schematic illustrating this technique (PDF) is also available, with the FET used being a 2N7000. By turning this FET on for about 15 ns using the falling edge of the circuit's output, the recovery time can be reduced to no more than 20 ns. In the schematic, this is achieved by injecting the desired "on pulse" into the FET's gate at the appropriate time. A digital photo of a physical version of the circuit is provided; while it does not include the FET switch, it otherwise adheres to the latter schematic. To enhance the circuit's stability, a DC bias was added to the negative input of the lower comparator (U1), and the DC bias on the negative input of the upper comparator (U2) was increased, necessitating an increase in the input isolation resistor (R9).

This pulse stretcher circuit leverages the LT1720 comparator to create a reliable one-shot pulse generator with a remarkable response time. The sensitivity of the circuit allows it to detect low-voltage pulses, making it suitable for applications requiring precise timing control. The incorporation of the 1N5711 diode ensures that the circuit can handle fast switching operations without significant delay or distortion. The use of PSpice simulations validates the circuit's performance characteristics, confirming its ability to trigger accurately under specified conditions.

The notable challenge with this circuit lies in its recovery time, which can limit its effectiveness in high-frequency applications. The solution to this limitation involves integrating a FET switch, specifically the 2N7000, to discharge the timing capacitor (C7) quickly. This modification minimizes the recovery time significantly, allowing the circuit to reset and be ready for subsequent triggering events in a much shorter timeframe. The method for activating the FET at the appropriate moment is critical, as it directly influences the overall performance and reliability of the pulse generator.

The adjustments made to the biasing of the comparators enhance the overall stability of the circuit, ensuring consistent operation across varying input conditions. The increase in the input isolation resistor (R9) further aids in maintaining signal integrity, preventing unwanted interactions between the comparators and the timing capacitor. This careful design consideration is essential for achieving the desired performance in practical applications.

Overall, this pulse stretcher circuit exemplifies the principles of high-speed signal processing and pulse generation, providing a valuable tool for engineers in various electronic applications.This circuit is from the data sheet for Linear Technology`s LT1720 (a 4. 5ns comparator). It`s the circuit entitled "Pulse Stretcher" at the very end. Essentially, it`s a one-shot with sensitivity down to 14mV for 5ns to 10ns inputs (i. e. , it doesn`t require a full swing from logical low to high as do most one-shots), and TTL logic level outputs. I t also exhibits a mere 4. 5ns delay from input to output. Here`s an OrCAD schematic ( pdf ) used to simulate the circuit: The diode (D1) is a 1N5711. PSpice simulations indicate that it does indeed have the advertised sensitivity (I was able to get it to fire cleanly with a 5 ns 14mV pulse provided the input had 2ns rise and fall times). This is great. or so one would think. What the data sheet fails to mention is that this one-shot has a large recovery time (roughly 6 time constants), resulting in outputs of less than the desired time constant (1us for the above schematic) for any additional inputs arriving 1 to 7 time constants after the initial input.

Discharging the timing capacitor (C7) with a FET switch reduces the recovery time substantially. Here`s an OrCAD schematic illustrating how one might do this ( pdf ): The FET used is a 2N7000. If one could turn this FET on for about 15ns using the falling edge of the circuit`s output, the recovery time is reduced to no more than 20ns. In the above schematic this is done artificially by injecting the desired "on pulse" into the FET`s gate at the appropriate time.

Here`s a digital photo of a real version of the circuit: It doesn`t incorporate the FET switch (obviously), but otherwise follows the latter schematic. To improve the circuit`s stability I added a dc bias to the negative input of the lower comparator (U1), and increased the dc bias on the negative input of the upper comparator (U2) (which also made it necessary to increase the input isolation resistor, R9).

🔗 External reference

This pulse stretcher circuit leverages the LT1720 comparator to create a reliable one-shot pulse generator with a remarkable response time. The sensitivity of the circuit allows it to detect low-voltage pulses, making it suitable for applications requiring precise timing control. The incorporation of the 1N5711 diode ensures that the circuit can handle fast switching operations without significant delay or distortion. The use of PSpice simulations validates the circuit's performance characteristics, confirming its ability to trigger accurately under specified conditions.

The notable challenge with this circuit lies in its recovery time, which can limit its effectiveness in high-frequency applications. The solution to this limitation involves integrating a FET switch, specifically the 2N7000, to discharge the timing capacitor (C7) quickly. This modification minimizes the recovery time significantly, allowing the circuit to reset and be ready for subsequent triggering events in a much shorter timeframe. The method for activating the FET at the appropriate moment is critical, as it directly influences the overall performance and reliability of the pulse generator.

The adjustments made to the biasing of the comparators enhance the overall stability of the circuit, ensuring consistent operation across varying input conditions. The increase in the input isolation resistor (R9) further aids in maintaining signal integrity, preventing unwanted interactions between the comparators and the timing capacitor. This careful design consideration is essential for achieving the desired performance in practical applications.

Overall, this pulse stretcher circuit exemplifies the principles of high-speed signal processing and pulse generation, providing a valuable tool for engineers in various electronic applications.This circuit is from the data sheet for Linear Technology`s LT1720 (a 4. 5ns comparator). It`s the circuit entitled "Pulse Stretcher" at the very end. Essentially, it`s a one-shot with sensitivity down to 14mV for 5ns to 10ns inputs (i. e. , it doesn`t require a full swing from logical low to high as do most one-shots), and TTL logic level outputs. I t also exhibits a mere 4. 5ns delay from input to output. Here`s an OrCAD schematic ( pdf ) used to simulate the circuit: The diode (D1) is a 1N5711. PSpice simulations indicate that it does indeed have the advertised sensitivity (I was able to get it to fire cleanly with a 5 ns 14mV pulse provided the input had 2ns rise and fall times). This is great. or so one would think. What the data sheet fails to mention is that this one-shot has a large recovery time (roughly 6 time constants), resulting in outputs of less than the desired time constant (1us for the above schematic) for any additional inputs arriving 1 to 7 time constants after the initial input.

Discharging the timing capacitor (C7) with a FET switch reduces the recovery time substantially. Here`s an OrCAD schematic illustrating how one might do this ( pdf ): The FET used is a 2N7000. If one could turn this FET on for about 15ns using the falling edge of the circuit`s output, the recovery time is reduced to no more than 20ns. In the above schematic this is done artificially by injecting the desired "on pulse" into the FET`s gate at the appropriate time.

Here`s a digital photo of a real version of the circuit: It doesn`t incorporate the FET switch (obviously), but otherwise follows the latter schematic. To improve the circuit`s stability I added a dc bias to the negative input of the lower comparator (U1), and increased the dc bias on the negative input of the upper comparator (U2) (which also made it necessary to increase the input isolation resistor, R9).

🔗 External reference