Based video surveillance system image sensor interface circuit

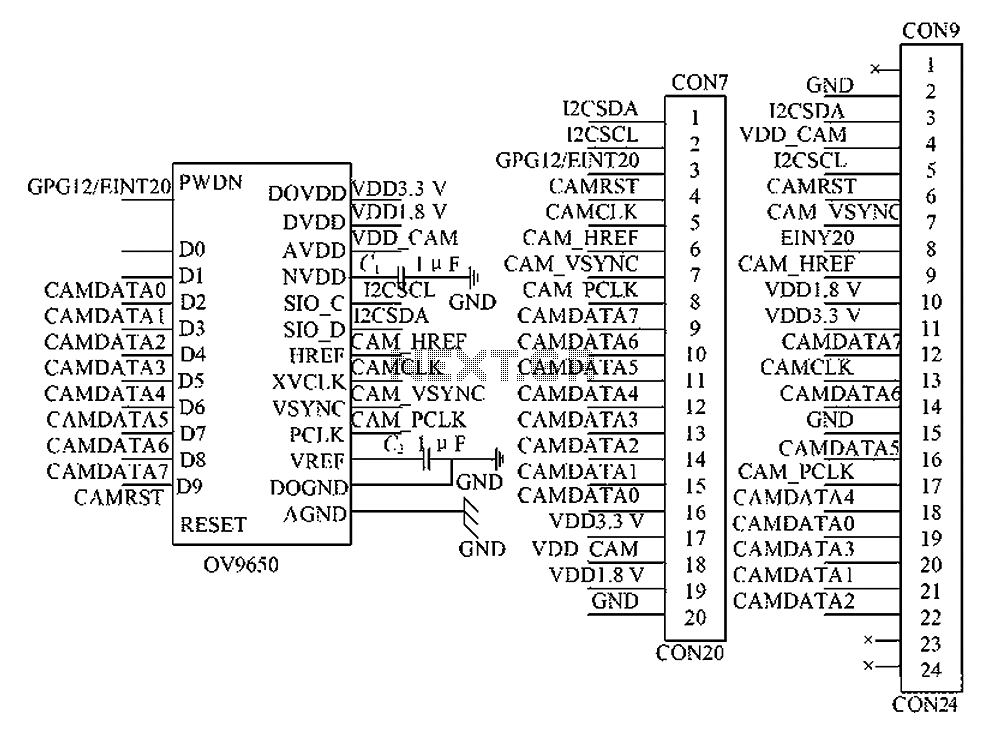

The circuit principle involves the OV9650 processor, which interfaces through three components: the SCCB interface, the data output interface, and the control interface. The SCCB interface is responsible for transferring initialization parameters from the processor's internal registers. It utilizes a data line (SIOD) and a clock line (SI-OC), functioning similarly to the I2C bus's SDA and SCL lines. In this configuration, the SCCB acts as an I2C bus, with the OV9650 serving as the I2C slave and the S3C2440 acting as the master. The I2C bus transmits data serially from high to low byte, and upon completing each byte transfer, the host controller sets the SDA line high and releases it, awaiting a confirmation signal from the device. The OV9650 features a built-in 10-bit A/D converter, providing 10 data outputs (D[0:9]). The output image data format can be in 10-bit RAW, RGB, or an 8-bit RGB conversion through an internal DSP/YCbCr. The CAM interface of the S3C2440 microprocessor supports an 8-bit YUV/YCbCr format, utilizing the OV9650's data interface (D[9:2]) connected to the CAMDAT A[7:0] port. The OV9650 receives a 24 MHz CPU operating clock as its XVCLK. Frame synchronization is achieved through an internally generated VSYNC signal, along with a horizontal synchronization signal (HREF) and a pixel clock signal (PCLK), which are controlled by the ARM chip for image acquisition. Each VSYNC pulse indicates the beginning of a new frame of image data acquisition.

The OV9650 camera module is designed to interface seamlessly with the S3C2440 microprocessor, leveraging the SCCB protocol for configuration and control. The SCCB interface operates similarly to the I2C communication protocol, allowing for efficient communication between the master (S3C2440) and the slave (OV9650). The use of a 10-bit A/D converter enhances the image quality by providing a higher resolution output, which can be processed in various formats depending on the application requirements.

The data output from the OV9650 can be configured to deliver either raw image data or processed formats, such as RGB or YUV, as needed for different image processing tasks. The internal digital signal processor (DSP) within the OV9650 plays a critical role in converting the raw data to a suitable format for display or further processing. The choice of the 8-bit YUV/YCbCr format is particularly advantageous for applications requiring efficient data bandwidth usage, as it reduces the amount of data transmitted while maintaining acceptable image quality.

Synchronization signals, such as VSYNC and HREF, are essential for coordinating the timing of image capture and processing. The VSYNC signal indicates the start of a new frame, while the HREF signal provides horizontal synchronization for each line of the image. The pixel clock (PCLK) further ensures that the data is read and processed at the correct intervals, enabling smooth image capture and playback.

In summary, the OV9650 camera module, in conjunction with the S3C2440 microprocessor, forms a robust and flexible imaging system capable of producing high-quality images suitable for various applications in embedded systems. The integration of advanced features such as the 10-bit A/D converter, multiple output formats, and precise synchronization mechanisms allows for efficient image processing and transmission. Circuit principle: OV9650 processor interfaces include three parts SCCB interface, data output interface and control interface. SCCB interface to play the role of transfer prov ided by the processor internal registers OV9650 initialization parameter, the data line and a clock line SIOD SI-OC, equivalent to the I2C bus SDA and SCL. That is, SC-CB acts I2C bus. OV9650 is I2C bus slave, S3C2440 is the corresponding master. I2 C bus using serial transmission from high to low byte data, each byte transfer is complete, the host controller will set high SDA and released pending confirmation signal sent from the device.

OV9650 embedded in a 10-bit A/D converter, corresponding to 10 data outputs D [0: 9]. Format of the output image data may be 10 original RAW, RGB or 8-bit RGB conversion through internal DSP/YCbCr. The choice of CAM IF S3C2440 microprocessor chip unit supports 8-bit YU V/YCbCr format, it takes the OV9650 data interface D [9: 2] data and CAM IF port CAMDAT A [7: 0] Phase connection.

The OV9650 XVCLK for receiving an output of 24 MHz CPU operating clock. Frame synchronization signal VSYNC OV9650 internally generated horizontal synchronization signal HREF, the pixel clock signal PCLK other three incoming ARM chip clock signal for controlling image acquisition. Each VSYN C pulse indicates the start of a frame of image data acquisition,

The OV9650 camera module is designed to interface seamlessly with the S3C2440 microprocessor, leveraging the SCCB protocol for configuration and control. The SCCB interface operates similarly to the I2C communication protocol, allowing for efficient communication between the master (S3C2440) and the slave (OV9650). The use of a 10-bit A/D converter enhances the image quality by providing a higher resolution output, which can be processed in various formats depending on the application requirements.

The data output from the OV9650 can be configured to deliver either raw image data or processed formats, such as RGB or YUV, as needed for different image processing tasks. The internal digital signal processor (DSP) within the OV9650 plays a critical role in converting the raw data to a suitable format for display or further processing. The choice of the 8-bit YUV/YCbCr format is particularly advantageous for applications requiring efficient data bandwidth usage, as it reduces the amount of data transmitted while maintaining acceptable image quality.

Synchronization signals, such as VSYNC and HREF, are essential for coordinating the timing of image capture and processing. The VSYNC signal indicates the start of a new frame, while the HREF signal provides horizontal synchronization for each line of the image. The pixel clock (PCLK) further ensures that the data is read and processed at the correct intervals, enabling smooth image capture and playback.

In summary, the OV9650 camera module, in conjunction with the S3C2440 microprocessor, forms a robust and flexible imaging system capable of producing high-quality images suitable for various applications in embedded systems. The integration of advanced features such as the 10-bit A/D converter, multiple output formats, and precise synchronization mechanisms allows for efficient image processing and transmission. Circuit principle: OV9650 processor interfaces include three parts SCCB interface, data output interface and control interface. SCCB interface to play the role of transfer prov ided by the processor internal registers OV9650 initialization parameter, the data line and a clock line SIOD SI-OC, equivalent to the I2C bus SDA and SCL. That is, SC-CB acts I2C bus. OV9650 is I2C bus slave, S3C2440 is the corresponding master. I2 C bus using serial transmission from high to low byte data, each byte transfer is complete, the host controller will set high SDA and released pending confirmation signal sent from the device.

OV9650 embedded in a 10-bit A/D converter, corresponding to 10 data outputs D [0: 9]. Format of the output image data may be 10 original RAW, RGB or 8-bit RGB conversion through internal DSP/YCbCr. The choice of CAM IF S3C2440 microprocessor chip unit supports 8-bit YU V/YCbCr format, it takes the OV9650 data interface D [9: 2] data and CAM IF port CAMDAT A [7: 0] Phase connection.

The OV9650 XVCLK for receiving an output of 24 MHz CPU operating clock. Frame synchronization signal VSYNC OV9650 internally generated horizontal synchronization signal HREF, the pixel clock signal PCLK other three incoming ARM chip clock signal for controlling image acquisition. Each VSYN C pulse indicates the start of a frame of image data acquisition,

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713